IC設計及驗證將迎來顛覆性改變

2019-09-27 12:39:21 EETOP 作者:周菊香日前,Mentor IC EDA 執(zhí)行副總裁 Joseph Sawicki 來到中國,參加一年一度的Mentor Forum 2019北京設計技術論壇。Sawicki在Mentor工作近30年,曾經領導過Mentor幾條業(yè)界享有盛譽的產品線,包括Calibre和Tessent等。把脈全球前沿技術趨勢,EETOP記者把握難得的機會,對Sawicki進行了深度采訪。

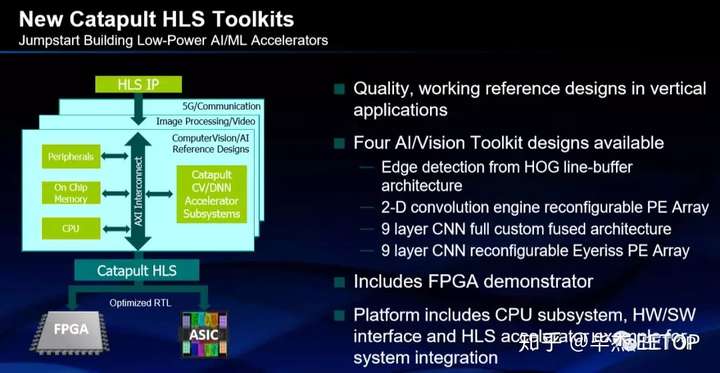

Sawicki分享說,在參加Mentor技術論壇之前,他走訪了一些中國企業(yè),其中有一家初創(chuàng)公司,剛剛成立兩年,但是半年前他們的AI芯片就已經去流片了。他感到驚訝的同時,也深表自豪,因為正是機器學習和人工智能技術,才可以讓該企業(yè)在如此短的時間內取得巨大成功。Sawicki特別強調地說:“人工智能和機器學習在下一個十年將會給整個半導體行業(yè)帶來巨大的機遇,EDA領域需要在設計和驗證方法論上有新的轉變。”針對IC設計方法論和驗證方法論的升級,EETOP記者特別提問:傳統(tǒng)芯片設計開發(fā)流程和人工智能時代的芯片開發(fā)流程有什么區(qū)別。Sawicki介紹說:“設計層級方面,要從 RTL 往上走,包括 C++甚至SystemC, 因為這些更高層級的設計語言可以更好地集成到人工智能開發(fā)平臺上。而傳統(tǒng)的開發(fā)流程,可能更關注的是設計上的規(guī)范和架構。在人工智能時代,我們更加需要關注的是應用的驗證,這是最重要的,而不是去驗證設計本身的正確性。”之前我們說到SoC集成電路芯片,更多說的是芯片的規(guī)格,比如內存的大小。而人工智能時代,未來設計方法論會有一些顛覆性的改變。這個時代的方法論更多的是RTL,然后才在芯片上面進行驗證,這種驗證是為了讓芯片的性能更強。對于半導體公司來說,最重要的,應是著眼于價值堆棧,必須定制出一些架構來滿足用戶的體驗,這樣的原生環(huán)境就是人工智能的開發(fā)平臺。顛覆性方法論帶來的IC設計驗證改變在傳統(tǒng)的設計環(huán)境中,通常會發(fā)現(xiàn),有時候是CPU太慢,有的時候是GPU功耗太高,應該怎么做?這時候需要找到一個很好的路勁,就是在原生設計環(huán)境當中運用人工智能,實現(xiàn)最優(yōu)的用戶體驗。HLS(高階綜合)可以作為連接 AI 原生環(huán)境和芯片的橋梁。它可以幫助客戶更好地設計架構,管理內存的分配、神經網絡的寬度和縱深,以及決定在里面放置多少管道等。管理好這些因素,才能為垂直應用提供經過優(yōu)化的 IC 軟件體驗。

針對HLS(高階綜合),Mentor已經開發(fā)出了Catapult軟件高級綜合(HLS)工具包和生態(tài)系統(tǒng),包括C/C++/SystemC HLS、HLS驗證以及低功耗HLS三大產品線。同時在整個Calibre平臺上增加了AI / ML基礎設施,并推出了兩種AI / ML技術,即Calibre Machine Learning OPC(mlOPC)和LFD with Machine Learning。據(jù)了解,該套件基于HLS C ++,提供了對象檢測參考設計和IP,可幫助設計人員快速找到神經網絡加速器引擎的最佳功率、性能和區(qū)域實現(xiàn)。該解決方案還包括一個完整的設置,用于構建AI / ML演示器平臺,在FPGA原型板上提供實時HDMI饋送。

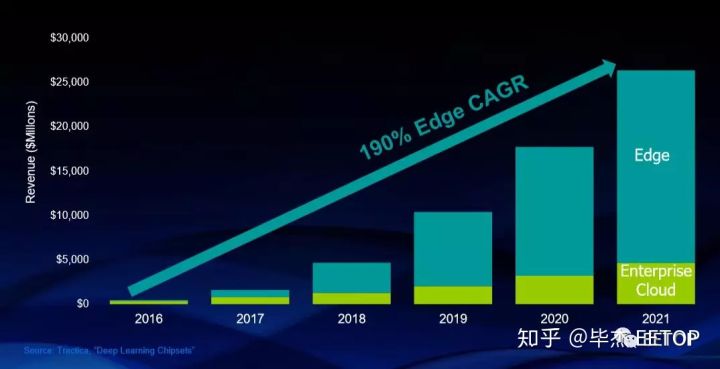

芯片設計的方法論需要發(fā)生轉變,驗證也同樣需要在方法論上進行改變。傳統(tǒng)的集成電路芯片驗證的測試方法就是要測試規(guī)則、架構和規(guī)范等,而在人工智能時代,更多的是垂直應用。需要進行的驗證是在應用層面,也就是說需要一些技術仿真出來一個 AI 引擎,然后在 CPU 系統(tǒng)上可以把這些數(shù)據(jù)推送到 AI 引擎上面。這樣就會生成一個界面,可以產生一個虛擬的PCI。此外,也可以執(zhí)行用戶想要執(zhí)行的應用,包括整個代碼的處理等。性能、耗能以及數(shù)據(jù)都可以通過驗證獲取。換而言之,也就是沒到芯片層面就可以理解整個過程的性能表現(xiàn)如何。Mentor致力于開源IPRFD設計中,Mentor也使用了機器學習,可以在云平臺上面進行 Face ID 或者語音識別。而且知道設計的問題和產出的限制在哪里,仿真的過程就可以大大降低。通過這樣的機器學習,可以仿真出一個可靠性非常高的庫或者矩陣。此外,通過機器學習方式,還可檢驗出測試系統(tǒng)當中哪些地方是失敗的,然后把這些和實體設計聯(lián)系起來就能夠找出問題在哪里,更好地推動設計的最終產品。Sawicki表示:“我們最終想要做出的IP,不是要在客戶芯片上直接進行應用,而是更多地幫助客戶有這樣的能力駕馭最新的設計方法論。具體在IP領域,Mentor的理念更多的是架構層面,也就是開源的IP。有了這樣的方式,我們的客戶就已經能夠得到優(yōu)化他們設計的起點。我們現(xiàn)在有許多客戶都在用高階綜合的方式來設計人工智能和機器學習的芯片。比如 NVIDIA ,他們利用這些方法論,一個很好的益處就是生產效率已經提高了50%。更重要的是,他們的驗證成本降低了80%。”數(shù)據(jù)中心聚合,看好邊緣計算那么到底是什么因素在驅動這些變革?Sawicki分析說,現(xiàn)在有越來越多海量的數(shù)據(jù)被移動到了網絡上,無論是車與車之間的智能網聯(lián),還是智慧城市、工業(yè)化/消費者層面的物聯(lián)網應用等。未來十年,這些高速數(shù)據(jù)將在網絡呈現(xiàn)數(shù)十倍的增長,這種高速增長一定會轉變現(xiàn)有的 CPU 或者數(shù)據(jù)中心由云進行管理的現(xiàn)有架構,都是由人工智能、機器學習帶來的機遇。除了數(shù)據(jù)聚合之外,現(xiàn)在還有越來越多的處理和運算被移動到了邊緣進行,未來六年邊緣計算每年都會有成倍的增長。這些,未來不管是在云的平臺還是在其它系統(tǒng)當中都可以大大提高系統(tǒng)的效率。

邊緣端連接設備的年復合增長率將達190%這些機遇會給市場帶來哪些不同影響?根據(jù)市場調研,人工智能可以助力半導體公司從技術堆棧當中獲得高達40%-50%的產值,移動端時代只是為半導體行業(yè)提供價值20%的產值。對于芯片客戶來說,可能會把越來越多的芯片放在數(shù)據(jù)中心進行管理,或是放在邊緣進行處理。對于風投公司來說,自2001年互聯(lián)網泡沫破滅后,風投公司已經大大降低了集成電路行業(yè)的投入。不過近幾年,風投資金有了很大的回歸和劇烈的增長,并且很多公司都已經著眼于人工智能和機器學習。對于芯片設計公司來說,絕大多數(shù)機遇都會發(fā)生在邊緣,面對這一顛覆性的市場,必須要做出一些改變。

Mentor仿真+西門子技術,強勢布局汽車市場Mentor是在2016年被西門子收購的。在收購當年,業(yè)界各種聲音,揣測Mentor緣何被收購。有認為是西門子為將來布局汽車電子市場而做的努力。今天看來,Mentor對西門子進軍AI領域起到了很大的推動作用。一方面,Mentor在被西門子收購之前在汽車行業(yè)表現(xiàn)的就很出色。Mentor有很多IC設計的工具,這些工具可以很好地提供給整車廠的供應商。在被西門子收購以后Mentor又開發(fā)了一項技術,還有模式分析方面的 OPC,需要有數(shù)千個CPU 24 小時不間斷地跑,通過機器學習提高效率,可以把整個時間和復雜性降低 3-4 倍。西門子過去這些年里在數(shù)字化雙胞胎技術(Digital Twin)方面一直在下大力氣去做。現(xiàn)在,通過Mentor的仿真系統(tǒng)與西門子的技術整合以后,通過Mentor的虛擬驗證方式生成自動駕駛在虛擬環(huán)境中所產生及處理數(shù)據(jù)的過程,之后將虛擬設備與西門子Simcentor Amesim機電一體化系統(tǒng)仿真平臺相連接,一方面是Veloce仿真整個芯片平臺,一方面是Amesim仿真整個動力總成和底盤系統(tǒng)平臺。通過雙方交互,實現(xiàn)整個電子和機械一體化的仿真驗證過程,可以讓 OEM 廠商在虛擬環(huán)境下直接了解車輛的性能。有了這樣的連接,最后的仿真和設計就可以達到一個非常高的表現(xiàn)和可靠性。據(jù)了解,目前在電氣和機械方面已經都可以在設計上完成。打造成功產品的三個關鍵Sawicki有敏銳的市場洞察力,在打造市場成功產品方面有非常豐富的經驗和成功案例。對于如何做出有市場優(yōu)勢的特色產品,Sawicki分享到:“首先我們必須要有一批非常具有熱情的開發(fā)者,這些開發(fā)者希望能夠向市場提供能夠帶來不同的產品,產品要能夠帶來不同才是價值所在。其次,這些工程師團隊必須非常密切地和客戶一起工作,因為遠離客戶的話就根本無法找到很好的解決問題的方式。最后,我們要找準客戶最困難的問題在哪里,就像 Calibre 的設計和 Tessent 的測試,我們要找到每個產品最重要的關鍵問題在哪里。如果能夠做到上述這三點,成功的概率就會非常大。”

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導體創(chuàng)芯網 快訊

相關文章