英特爾、三星、臺積電展示3D堆疊晶體管--CFET

2023-12-24 11:07:00 EETOP

芯片公司正在從 2011 年以來使用的FinFET器件結構過渡到納米片或環柵晶體管。這些名稱反映了晶體管的基本結構。在 FinFET 中,柵極控制流過垂直硅鰭的電流。在納米片器件中,該鰭被切割成一組帶,每個帶都被柵極包圍。CFET 實質上是將較高的硅帶堆疊起來,一半用于一個器件,一半用于另一個器件。英特爾工程師在 2022 年 12 月的《IEEE Spectrum》雜志上解釋說,這種器件在單一集成工藝中將兩種類型的晶體管--nFET 和 pFET 疊加在一起。

專家估計 CFET 將于七到十年后投入商業應用,但在準備就緒之前仍有大量工作要做。

英特爾是三者中最早展示 CFET 的公司,早在 2020 年就在 IEDM 上推出了早期版本。這一次,英特爾報告了圍繞 CFET 制造的最簡單電路(反向器)的幾項改進。CMOS 反相器將相同的輸入電壓發送到堆棧中兩個器件的柵極,并產生與輸入邏輯相反的輸出。

“反相器是在單個鰭片上完成的,”英特爾組件研究小組首席工程師 Marko Radosavljevic 在會議前告訴記者。他說,“在最大縮放比例下,它將是普通 CMOS 逆變器尺寸的 50%”。

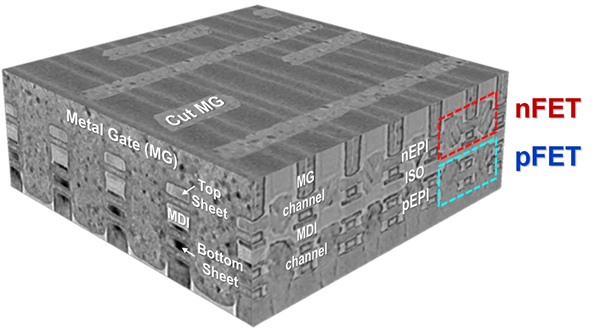

英特爾的反相器電路依賴于一種連接頂部和底部晶體管[黃色]的新方法,并從硅[灰色]下方接觸其中一個晶體管

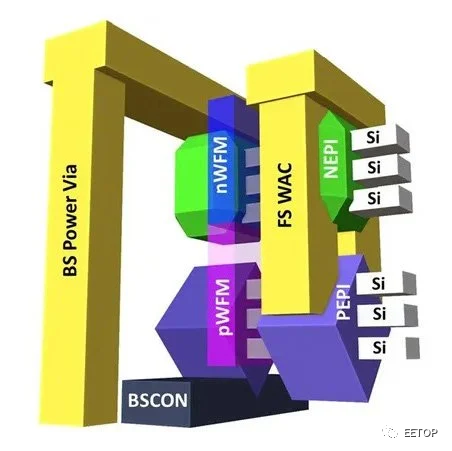

問題在于,將兩個晶體管堆棧擠入反相器電路所需的所有互連會削弱面積優勢。為了保持緊張,英特爾試圖消除連接堆疊設備時涉及的一些擁塞。在當今的晶體管中,所有連接都來自器件本身之上。但今年晚些時候,英特爾正在部署一種稱為背面供電的技術,該技術允許在硅表面上方和下方存在互連。使用該技術從下面而不是從上面接觸底部晶體管顯著簡化了電路。由此產生的逆變器具有 60 納米的密度質量,稱為接觸多晶間距(CPP,本質上是從一個晶體管柵極到下一個晶體管柵極的最小距離)。如今的5納米節點芯片的CPP約為50納米。

此外,英特爾還通過將每個器件的納米片數量從 2 個增加到 3 個、將兩個器件之間的間距從 50 nm 減小到 30 nm,以及使用改進的幾何形狀來連接器件的各個部分,從而改善了 CFET 堆棧的電氣特性。

與英特爾的 60 納米相比,三星采用了比英特爾更小的尺寸,展示了 48 納米和 45 納米接觸式多間距 (CPP) 的結果,不過這些結果是針對單個器件,而不是完整的反相器。雖然三星的兩個原型 CFET 中較小的性能有所下降,但幅度不大,該公司的研究人員相信制造工藝優化將解決這一問題。

三星成功的關鍵在于能夠對堆疊 pFET 和 nFET 器件的源極和漏極進行電氣隔離。如果沒有足夠的隔離,這種被三星稱為三維堆疊場效應晶體管(3DSFET)的器件就會泄漏電流。實現這種隔離的關鍵步驟是將涉及濕化學品的蝕刻步驟換成一種新型的干式蝕刻。這使得良率提高了 80%。

與英特爾一樣,三星也從硅片下方接觸器件底部,以節省空間。不過,這家韓國芯片制造商與美國公司不同的是,在每個配對器件中只使用了一片納米片,而不是英特爾的三片。據其研究人員稱,增加納米片的數量將提高 CFET 的性能。

臺積電躍躍欲試

與三星一樣,臺積電也成功實現了 48 納米的工業級間距。其設備的與眾不同之處在于采用了一種新方法,在頂部和底部設備之間形成一個介電層,以保持它們之間的隔離。納米片一般由硅層和硅鍺層交替形成。在工藝的適當步驟中,硅鍺特定蝕刻方法會去除這些材料,從而釋放出硅納米線。在隔離兩個器件的層中,臺積電使用了鍺含量特別高的硅鍺,因為它比其他硅鍺層的蝕刻速度更快。這樣,隔離層就可以在釋放硅納米線之前分幾步制作完成。