從FinFET到CFET:imec提出1nm器件新架構

2022-07-19 12:14:40 EETOPimec 研究人員發現了有關“互補 FET”的新發現,這是一種適用于 1nm 邏輯技術節點及以上節點的有吸引力的器件架構。

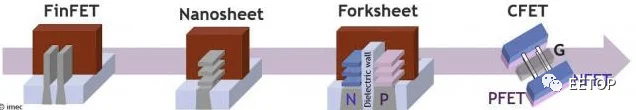

由于從平面 FET 過渡到FinFET,晶體管尺寸減小了,而性能卻提高了。這種轉變是必要的,因為平面 FET 的性能在柵極長度減小時開始下降。FinFET有助于維持擴展路徑。

在 FinFET 中,源極和漏極之間的通道是 Fin 的形式。閘門纏繞在這個通道周圍,從通道的三個側面施加控制。這種方法消除了平面 FET 遭受的短溝道效應。此外,更高的鰭片高度允許在相同區域內更高的器件驅動電流。

然而,隨著技術規模超過 5 nm,Fin 結構無法提供足夠的靜電控制。

為了實現進一步的縮放,imec 引入了一種垂直堆疊的納米片結構,其中柵極完全包裹在通道周圍。據說這種架構提供了卓越的控制和更好的三維體積分布。

Forksheet 器件是垂直堆疊納米片的延伸。在這里,納米片由三柵極叉形結構控制,這是通過在 p 和 nFET 器件之間引入介電壁來實現的。隔離允許更緊密的 n 到 p 間距和更高的性能。隔離還將標準單元的軌道高度擴展到 4T,這意味著四個單元內金屬線可以適應標準單元高度的范圍。

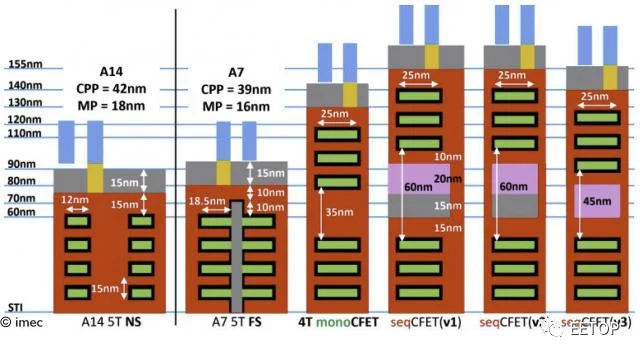

然而,金屬間距的 n 區和 p 區之間的間距低至 16 nm,這對于 4T 軌道高度單元設計來說太窄了。為了最大化溝道寬度和驅動電流,imec研究人員提出了 CFET 架構。

研究人員探索了兩種可能的集成方案來實現垂直堆疊:單片和順序。在 CFET 架構中,n 和 p 器件垂直堆疊在一起,消除了標準單元高度的 np 間距。

單片 CFET 流發生在三個部分:底部通道的外延生長、中間層的沉積以及頂部通道的外延生長。這種流程比順序流程更復雜,因為它會產生高縱橫比 (HAR) 垂直結構,需要進一步的圖案化。

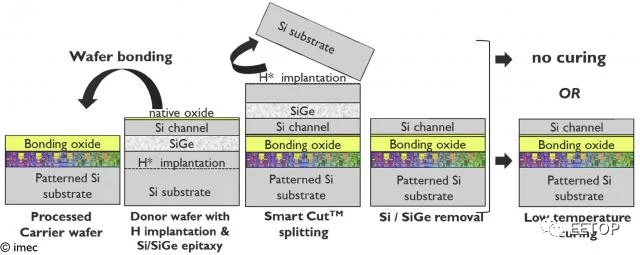

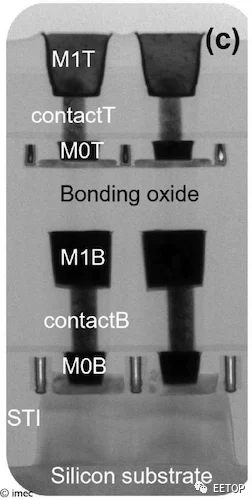

在順序制造流程中,底部器件被加工到觸點。然后,使用晶圓對晶圓鍵合技術在其頂部創建一個覆蓋半導體層。最后,集成頂層設備。這個過程更簡單,因為可以以二維方式單獨處理頂級設備。

這些過程中的每一個都有其優點和缺點。在 2022 年VLSI 論文中,imec 研究人員提出了 4T 標準單元設計中單片 CFET 與順序 CFET 的功率性能面積成本(PPAC) 評估。他們還評估了順序 CFET 的不同層轉移工藝。

imec報告說,從成本角度來看,半導體制造商 SOITEC 提供了一種很有前途的層轉移工藝——一種依賴于低溫“智能切割”流程的工藝。它使用在低溫下分裂的工程體供體晶圓。研究人員發現,在概念驗證層轉移后處理的頂層設備從降低的電氣性能中恢復。

imec邏輯 CMOS 微縮計劃主管 Naoto Horiguchi 強調,雖然這種架構是真正的 CFET 架構,但它不是真正的 CFET 實現,因為底部器件中沒有金屬互連層。

他指出,imec 的測試工具展示了“改進的層傳輸作為順序 CFET 和其他 3D 順序堆疊實現的關鍵模塊”。在未來的研究中,imec 報告說,研究人員將致力于實現真正的順序CFET。

https://www.allaboutcircuits.com/news/from-finfets-to-cfets-imecs-plan-for-continued-transistor-scaling/

EETOP 官方微信

創芯大講堂 在線教育

半導體創芯網 快訊

相關文章