晶體管級的堆疊!下一代晶體管技術:CFET,將全面替代GAA!英特爾和臺積電已走在最前列!

2023-10-06 11:59:34 EETOP據eeNewsEurope報道,英特爾和臺積電將在即將召開的國際電子器件會議(IEDM)上公布他們在垂直堆疊互補場效應晶體管(CFET)方面取得的進展。CFET 很可能在未來十年的某個時候接替全柵極 (GAA) 晶體管(GAA 晶體管本身尚未占領市場)。

CFET 的概念最初是由 IMEC (比利時微電子研究中心)于 2018 年提出的,它涉及將 n 型和 p 型晶體管層疊在一起。雖然早期的研究大多源自學術界,但英特爾和臺積電等商業公司現已涉足這一領域,并正在積極探索這種下一代晶體管。

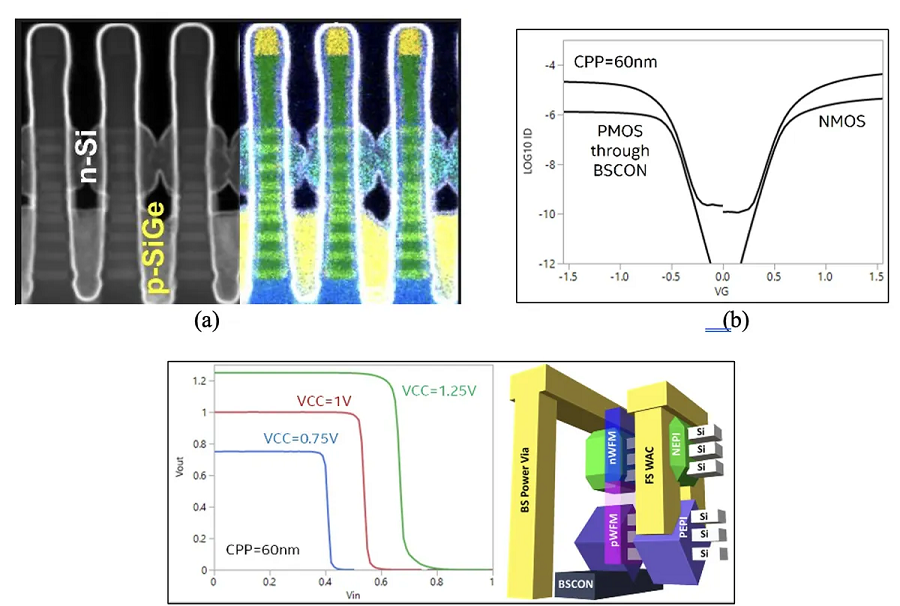

英特爾的研究人員構建了一個單片 3D CFET,其中包含三個 n-FET 納米帶,層疊在三個 p-FET 納米帶之上,保持 30nm 的垂直間隙。英特爾公司在題為 "“采用電源通孔和直接背面器件觸點的 60 納米柵極間距的堆疊式 CMOS 反相器演示”的演講中將介紹利用 60 納米柵極間距 CFET 的功能性反相器測試電路。該設計還采用了垂直分層雙源漏外延和雙金屬柵極堆棧,并結合了英特爾的 PowerVia 背面電源傳輸技術。

為了不被競爭對手超越,臺積電將介紹其實踐 CFET 的方法,該方法專為邏輯技術而定制,具有 48 納米柵極間距。臺積電的設計強調了在 p 型晶體管之上疊加放置的 n 型納米片晶體管,具有跨越六個數量級的顯著開/關電流比。

臺積電表示,該公司的晶體管已經證明了它們的耐用性,90%以上的晶體管成功經受住了測試。雖然臺積電承認,要充分利用CFET技術的能力,還有更多的功能需要吸收,但正在進行的工作是實現這一目標的關鍵一步。

CFET 給晶體管設計帶來了顯著轉變,其垂直堆疊允許兩個晶體管安裝在一個晶體管的占地面積內,從而增加芯片上的晶體管密度。這種設計不僅為提高空間效率鋪平了道路,而且還促進了更精簡的CMOS邏輯電路布局,有利于提高設計效率。

此外,CFET 的固有結構可能會減少寄生效應,從而潛在地提高性能和功率效率。它們的適應性設計能力(例如平衡 NMOS 和 PMOS 通道變化的能力)與背面供電等創新相結合,進一步簡化了制造工藝,使 CFET 成為晶體管技術領域的一個有前景的發展。

英特爾和臺積電的努力凸顯了 CFET 技術對半導體行業未來的重要性。

來源:由EETOP編譯整理自tomshardware