7納米和更小節點的時鐘設計分析及挑戰

2022-10-16 12:53:18 EETOP在曾經經歷過在過去的好日子里,時鐘信號看起來像方波,并且電壓擺幅為 5V or 3.3V,但是使用 7nm 技術,時鐘信號現在看起來更像鋸齒信號,實際上在芯片的核心內部可能無法達到 0.65V 的完整 Vdd 值。接下來我將介紹一些半導體市場趨勢,然后介紹分析 7nm 和更小工藝節點的高性能時鐘的挑戰。

市場走向

臺積電、三星和英特爾等代工廠正在為從事各種 SoC 設備的設計人員提供 7nm及更小的節點技術,這些設備用于:人工智能、機器人、自動駕駛汽車、航空電子設備、醫療電子、數據中心、5G 網絡和移動設備。這些設計需要數十億晶體管范圍內的高集成度,以及在電池或嚴格的功率預算內運行的低功率。

7nm 設計挑戰

高級節點存在許多設計挑戰,例如:

晶體管老化效應

更高的設計成本,每個7納米設計的成本在1.2-4.2億美元之間

使用較低的 Vdd 水平降低了設計裕度

功耗隨時鐘頻率上升

工藝變化的影響

更大的延遲變化

互連 RC 變化增加

更高電阻的互連導致信號失真

更快的晶體管開關時間帶來更大的功率瞬變

更多具有多電壓電源域的時鐘

與開關相關的功率密度和芯片溫度增加

老化效應

隨著晶體管器件的開啟和關閉,有兩個主要的物理效應會影響可靠性:

負偏壓溫度不穩定性 ( NBTI )

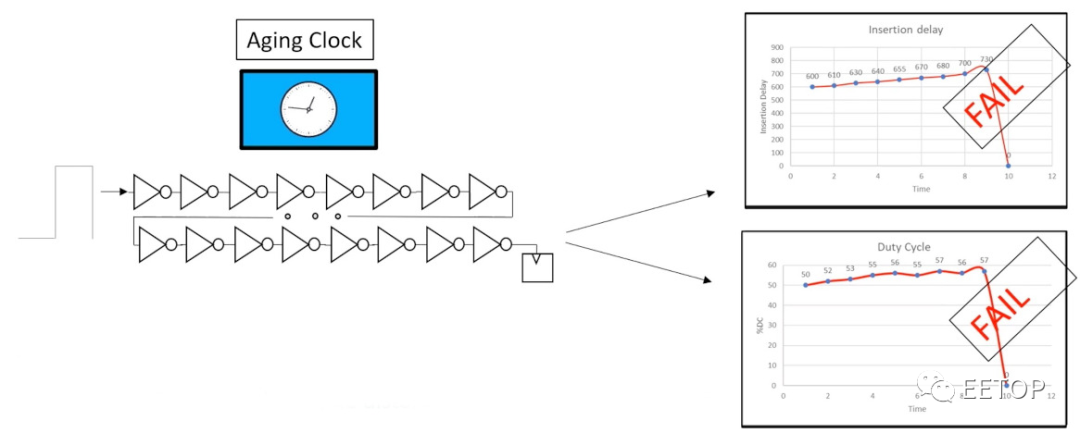

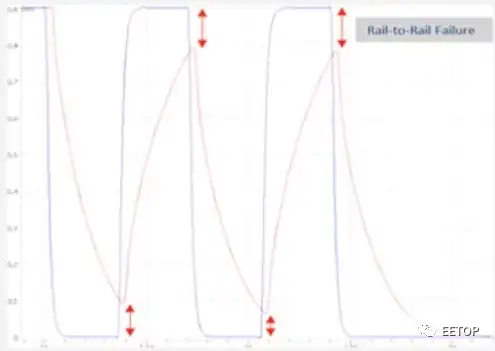

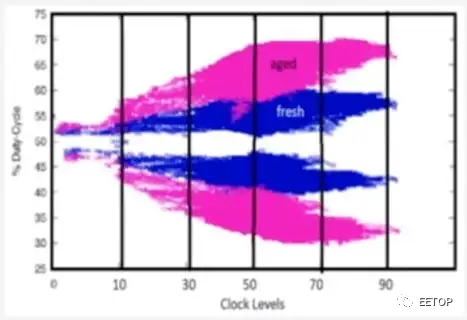

電路設計人員了解到,這些老化效應會改變器件的 Vt,進而減慢時鐘信號的上升和下降時間。隨著時間的推移,這些老化效應會扭曲時鐘的占空比,實際上會導致時鐘電路出現故障。下面顯示的是兩個圖表,其中時鐘插入延遲和占空比最終因老化效應而失敗。時鐘抖動和軌到軌(R2R) 違規的增加也表現為老化效應。

老化時鐘

老化時鐘

靜態時序分析 (STA)

多年來,EDA用戶一直依賴于STA工具,然而這些工具對老化效應做了簡化的假設,通過應用覆蓋式定時降額,而不是根據實際的開關活動應用老化。在長信號網絡中,由于電阻屏蔽,STA中的互連延遲模型會忽略占空比畸變誤差。STA工具也不能直接捕捉軌到軌故障,盡管它可以測量插入延遲和切換速率。抖動不是作為 STA 工具的一部分進行模擬的,因此設計人員不知道哪些區域需要修復的噪聲最高。

克服分析限制

理想的時鐘分析方法將提供整個時鐘域的SPICE級精度,即使有數百萬個器件。它將允許工程師測量整個時鐘路徑上每個節點的R2R和抖動,包括有無老化。多個時鐘可以在許多工藝角和Vdd組合中進行分析,在當前EDA工具流程中工作,并在一夜之間產生結果。

Infinisim 方法

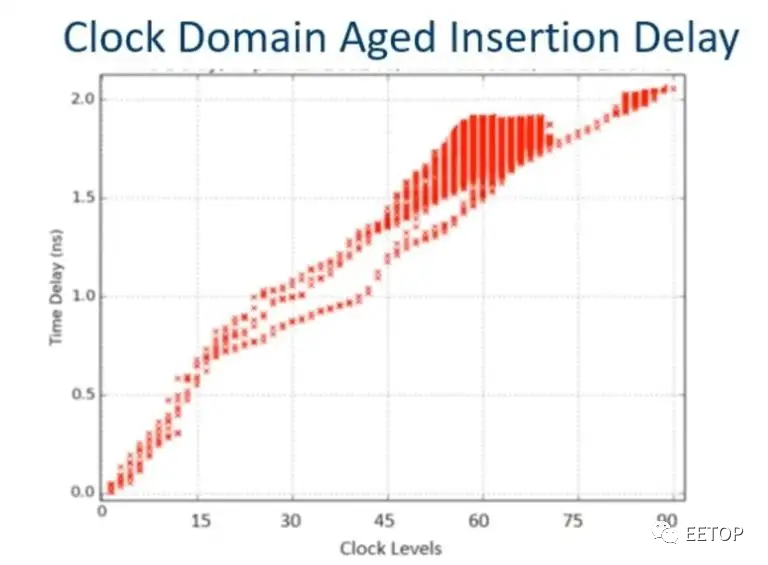

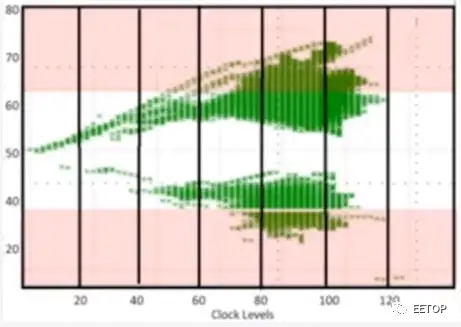

Infinisim 是一家專注于時鐘分析的 EDA 供應商,他們的工具稱為ClockEdge。以下是他們工具中時鐘域上升擺率和時鐘域老化插入延遲的兩個分析示例:

Infinisim 的 EDA開發人員想出了如何模擬整個時鐘域,產生具有 SPICE 精度的完整模擬結果,允許 SoC 團隊在老化時實際測量時鐘占空比,或測量 R2R,甚至測量噪聲引起的抖動。ClockEdge 工具甚至以分布式方式跨多個服務器運行,以便在較快地產生結果。

時鐘占空比退化

軌到軌故障檢測

老化效應

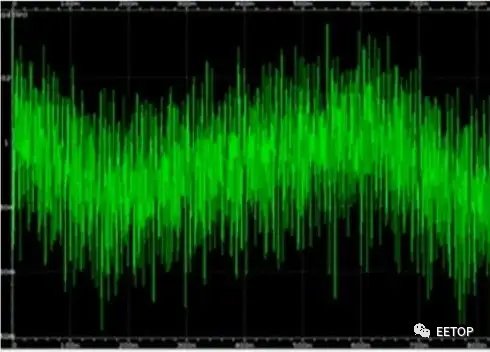

抖動

ClockEdge 確實是 STA 的補充, ClockEdge 將成為您的時鐘簽核工具。所有設備老化模型均由您的代工廠提供。作為 ClockEdge 性能的一個例子,它運行在一個有 450 萬個門、包含數十億個晶體管的時鐘電路上;跟蹤需要 4.5 小時,仿真總共需要 12 小時,在 250 個 CPU 上運行。

總結

設計 7nm 和更小工藝節點的 SoC 是一項艱巨的任務,需要專業的時鐘分析知識以確保首次通過硅片成功。

原文

https://semiwiki.com/eda/317962-analyzing-clocks-at-7nm-and-smaller-nodes/