據(jù)Sam Zeloof介紹,為了打造自己的芯片工廠,自 2016 年 10 月以來(lái),就一直在積累相關(guān)設(shè)備。2017年家庭芯片工廠初步建成。

隨后Sam Zeloof開始了集成電路的設(shè)計(jì)與制造研究,先從FET器件做起,然后在2018年高三器件做出了第一個(gè)第一個(gè)自制集成電路—Z1放大器。Z1 有 6 個(gè)晶體管,是開發(fā)所有工藝和設(shè)備的絕佳測(cè)試芯片。

一些更多的認(rèn)識(shí)與改進(jìn)。在此基礎(chǔ)上,Sam 做出了Z2芯片,該芯片 有 100 個(gè)晶體管,采用 10µm多晶硅柵極工藝——與英特爾的第一款處理器技術(shù)相同。Sam介紹,該芯片是一個(gè)簡(jiǎn)單的 10×10 晶體管陣列,用于測(cè)試、表征和調(diào)整過(guò)程,但這是向更先進(jìn)的 DIY 計(jì)算機(jī)芯片邁出的一大步。Intel 4004 有 2,200 個(gè)晶體管,Sam表示已經(jīng)在同一塊硅片上制造出 1,200 個(gè)晶體管。

在作者的博客上(http://sam.zeloof.xyz)詳細(xì)介紹了家庭芯片工廠諸多細(xì)節(jié),以及各款芯片的設(shè)計(jì)制造過(guò)程。

今天,我們?yōu)榇蠹曳窒硪幌伦髡咴?018年高三期間設(shè)計(jì)和制作第一款集成電路的詳細(xì)過(guò)程及方法。

前言

我很高興地宣布第一個(gè)自制集成電路的細(xì)節(jié),并分享這個(gè)項(xiàng)目在過(guò)去一年里帶給我的旅程。我希望我的成功能激勵(lì)他人并幫助開啟家用芯片制造的革命。當(dāng)我開始這個(gè)項(xiàng)目時(shí),我不知道自己進(jìn)入了什么領(lǐng)域,但最終我在物理、化學(xué)、光學(xué)、電子學(xué)和許多其他領(lǐng)域?qū)W到的東西比我想象的要多。

我展示了第一個(gè)自制的(光刻制造的)集成電路——“Z1”PMOS 雙差分放大器芯片。我說(shuō)“光刻制造”是因?yàn)?JeriEllsworth 制造了第一個(gè)晶體管和邏輯門(用導(dǎo)電環(huán)氧樹脂精心手工接線)并向世界展示了這是可能的。受到她工作的啟發(fā),我展示了由可擴(kuò)展的行業(yè)標(biāo)準(zhǔn)光刻工藝制成的 IC。不用說(shuō),這是我之前復(fù)制 Jeri 的 FET 制造工作的邏輯升級(jí)。

我介紹的第一個(gè)自制(光刻制造的)集成電路是"Z1"PMOS雙差分放大器芯片。在此之前Jeri Ellsworth自制過(guò)晶體管和邏輯門,門(用導(dǎo)電環(huán)氧樹脂精心手工布線),并向世界展示了這是可能的。受她工作的啟發(fā),我展示了由可擴(kuò)展的、符合工業(yè)標(biāo)準(zhǔn)的光刻工藝制造的集成電路。

設(shè)計(jì)

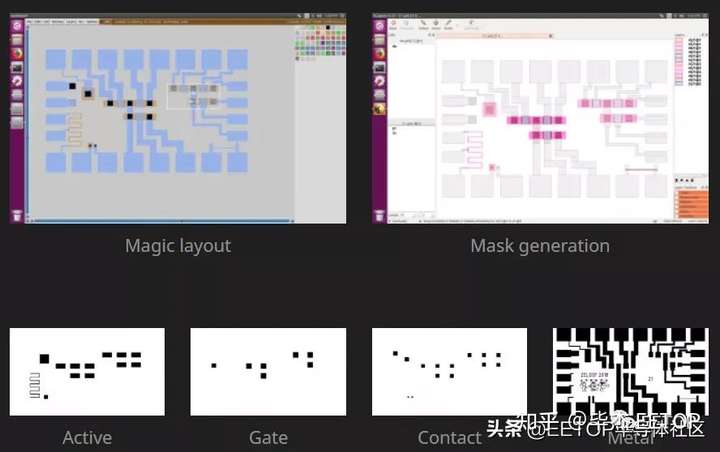

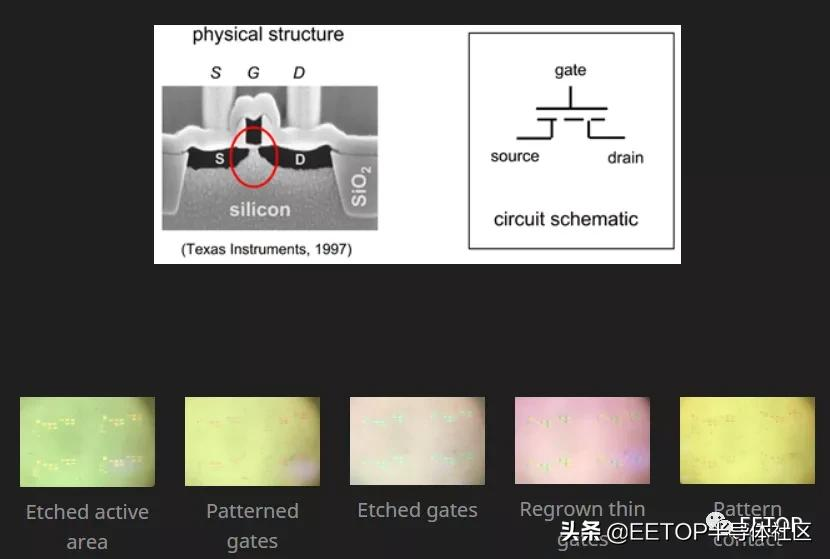

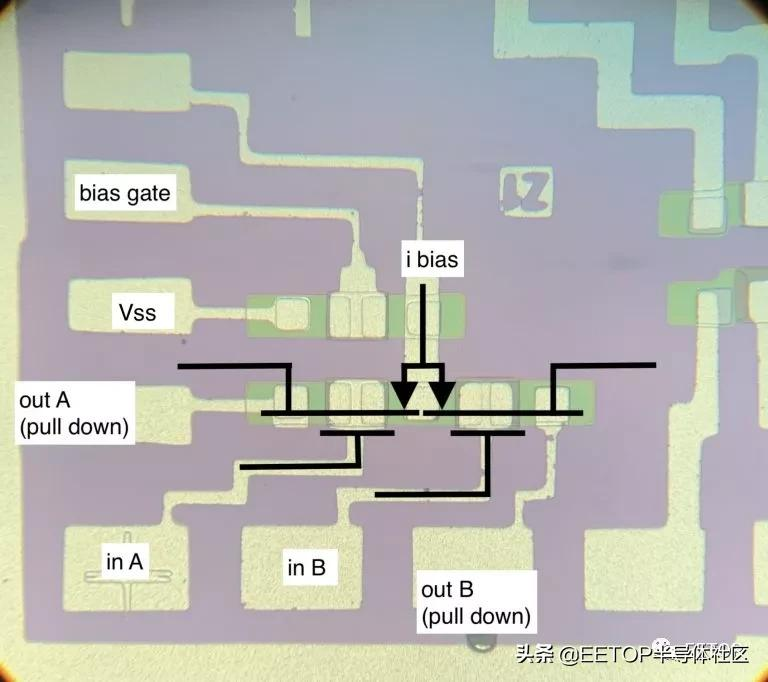

我設(shè)計(jì)Z1放大器是為了尋找一個(gè)簡(jiǎn)單的芯片來(lái)測(cè)試和調(diào)整我的工藝。在MagicVLSI中完成了4個(gè)掩模的PMOS工藝(有源/摻雜區(qū)、柵極氧化物、接觸窗口和頂部金屬)的布局。就避免離子污染而言,PMOS 比 NMOS 更具優(yōu)勢(shì),這使其能夠在車庫(kù)中制造。掩模被設(shè)計(jì)成16:9的長(zhǎng)寬比,便于投影光刻。

最初的芯片柵極尺寸約為 175μm(目前FET 柵極長(zhǎng)度(特征尺寸)已減小到 <5μm,(1975 技術(shù)水平),從而提高了器件性能。),每個(gè)放大器部分(中間和右側(cè))包含 3 個(gè)晶體管(2 個(gè)用于長(zhǎng)尾差分對(duì),一個(gè)用作電流源/負(fù)載電阻器),這意味著 IC 上總共有 6 個(gè) FET。IC 的左側(cè)部分包含電阻器、電容器、二極管和其他用于表征制造過(guò)程的測(cè)試功能。差分對(duì)的每個(gè)節(jié)點(diǎn)都連接到引線框架上的一個(gè)單獨(dú)引腳,因此可以對(duì)其進(jìn)行分析,并可以根據(jù)需要添加外部偏置。

功能圖

制造

制造這種芯片需要66個(gè)獨(dú)立的制造步驟,整個(gè)過(guò)程大約需要12個(gè)小時(shí)。制程良率可高達(dá)80%。

家用芯片制造化學(xué)工作臺(tái)如下圖所示,基本上包括制造 IC 所需的一切,除了真空室和光刻設(shè)備。

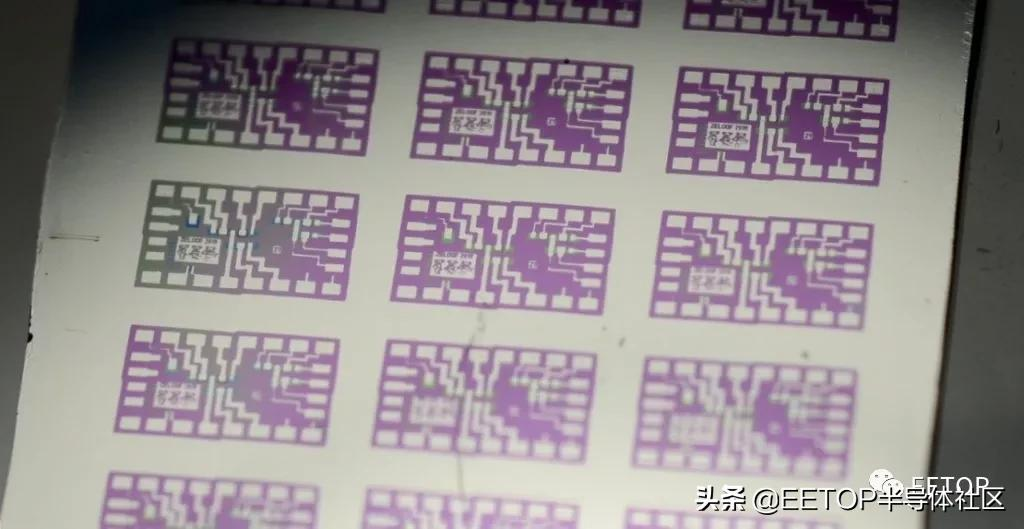

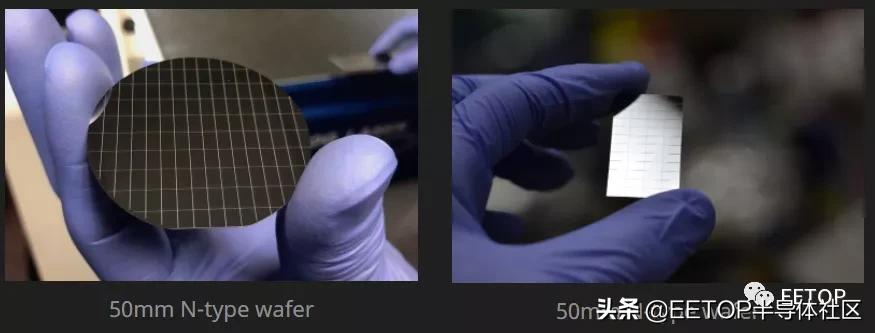

用Epilog光纖激光器將體電阻率為1到10Ω-cm(厚度為325µm時(shí)為30.8到308Ω/sq)的硅片劃成5.08x 3.175mm的裸片(約16mm^2的面積)。在激光刻劃之前,可以在晶片上旋涂溶于水或光刻膠中的聚乙烯醇,以“捕捉”激光燒蝕碎片,然后在加工前將薄膜在溶劑中去除。選擇此芯片尺寸以適合京瓷 24 針 DIP 載體。

原生氧化物被快速稀釋的HF浸泡剝離,然后在Piranha溶液(H2SO4:H2O2)、RCA1(H2O:NH3:H2O2)、RCA2(H2O:HCL:H2O2)中廣泛清洗,然后再進(jìn)行一次稀釋的HF浸泡。這些清洗浸漬大多為10分鐘,可以通過(guò)提高到~40ºC來(lái)促進(jìn)。

在水蒸氣環(huán)境中(濕式氧化),現(xiàn)場(chǎng)的氧化物被熱增長(zhǎng)到5000-8000Å的厚度。人們可以考慮在此步驟中把去離子水與百分之幾的鹽酸混合。氯化物原子有助于獲取和固定離子污染物,據(jù)說(shuō)還能使生長(zhǎng)率提高5-7%。再加上我正在制造PMOS器件而不是NMOS,這些都給污染控制帶來(lái)了巨大的優(yōu)勢(shì),并允許在車庫(kù)里制造出性能良好的器件。

氧化后的晶圓已準(zhǔn)備好用于有源/摻雜(P 型)區(qū)域的圖案化。正性光刻膠(用于 SiO2 圖案化的AZ MiR 701和 用于鋁層的AZ 4210)以大約 3000rpm 的速度旋轉(zhuǎn),產(chǎn)生約1.5μm 的 AZ MiR 701 或 3.5μm 的 AZ 4210 薄膜,該薄膜在熱板上在 90C 下軟烘烤.

光刻工藝細(xì)節(jié)

有源區(qū)掩模用我的Mark IV 無(wú)掩模光刻步進(jìn)機(jī)在 365nm UV 下曝光, 圖案在 TMAH 或 KOH 溶液中顯影,具體取決于抗蝕劑。

在接下來(lái)的HF蝕刻步驟中,將蝕刻圖案轉(zhuǎn)移到氧化層,并為摻雜打開裸硅表面的窗口,然后將抗蝕圖案烤硬,并使用一些其他技巧來(lái)確保良好的抗蝕附著力和化學(xué)穩(wěn)定性。這些區(qū)域后來(lái)成為fet的源/漏。

然后通過(guò)固體或液體源進(jìn)行摻雜。固體源是氮化硼圓盤,放置在管式爐中距離晶片附近 (<2mm)。或者,旋涂液體源可以由磷酸或硼酸在水或溶劑中制備,并在標(biāo)準(zhǔn)的預(yù)沉積/HF 浸漬/推進(jìn)/脫釉工藝中進(jìn)行摻雜。我在亞馬遜上獲得了純磷酸,從蟑螂和螞蟻藥那里獲得了硼酸。由于這里 PMOS 的起始晶片是 N 型,我正在為源極/漏極區(qū)進(jìn)行硼的P 擴(kuò)散,并針對(duì) 100 到 250 Ω/sq 的擴(kuò)散區(qū)中的薄層電阻。

然后對(duì)柵氧化層和接觸層重復(fù)上述構(gòu)圖步驟兩次。柵極氧化物必須比場(chǎng)氧化物薄得多(<~750Å),因此源極/漏極之間的區(qū)域被蝕刻掉,并且在那里生長(zhǎng)更薄的氧化物。然后,由于整個(gè)晶片在摻雜步驟中已被氧化,因此必須蝕刻金屬層的接觸窗以與源/漏摻雜區(qū)連接。

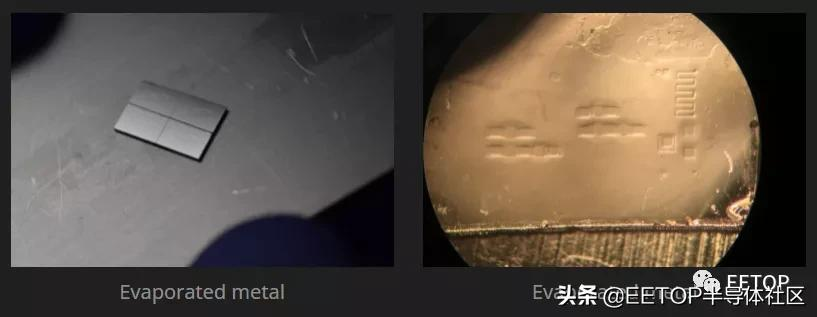

現(xiàn)在,所有晶體管都已形成并準(zhǔn)備好互連并斷開到引線框架。一層鋁(400-500nm)被濺射或熱蒸發(fā)到晶片上。另一種方法是使用剝離工藝,其中首先圖案化光刻膠,然后沉積金屬。為了支持引線鍵合,該金屬層做得更厚(對(duì)于 Au 線楔鍵合大約為 2.5µm。)對(duì)于熱蒸發(fā)膜,這些膜的測(cè)量體電阻率約為 5.4e-6 Ω-cm,是理想值 2.7e- 的兩倍在 20ºC 時(shí),Al為 6 Ω-cm。在真空沉積過(guò)程中將氧氣和其他氣體摻入鋁膜可能是造成這種差異的原因。

然后用光刻法對(duì)金屬層進(jìn)行圖案化,并在熱磷酸 (50ºC) 中蝕刻,以產(chǎn)生完整的 IC。測(cè)試前的最后一步是目視檢查和對(duì)鋁進(jìn)行高溫退火以創(chuàng)建歐姆連接。

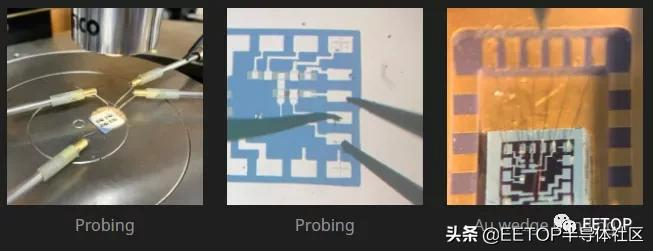

2018年時(shí)我還沒(méi)有焊線機(jī),所以當(dāng)時(shí)我的測(cè)試僅限于用鋒利的鑷子手動(dòng)探測(cè)晶圓或使用倒裝芯片板(難以對(duì)齊)將其連接到曲線跟蹤器。還對(duì)差分放大器進(jìn)行了經(jīng)驗(yàn)在線測(cè)試以驗(yàn)證操作。

二極管IV曲線

PMOS Id / Vds 曲線

正如您在上面的 PMOS FET Id 與 Vds 曲線中所見,芯片之間存在大量差異,同一天制造的器件可能具有截然不同的特性。以-1V Vgs 增量進(jìn)行 5 條跡線需要大約 -8V 的體/襯底偏置來(lái)克服固定電荷(柵極下捕獲的正雜質(zhì)離子)和柵極區(qū)域中的晶格缺陷,并產(chǎn)生預(yù)期的圖形。

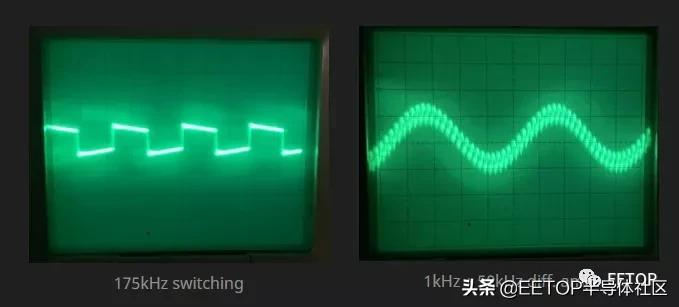

該芯片還可以連接為 3 級(jí)環(huán)形振蕩器,這是對(duì)新 IC 制造工藝的經(jīng)典測(cè)試:

顯示 3 個(gè)階段的自然頻率約為 5kHz,主要受到光刻對(duì)準(zhǔn)限制導(dǎo)致的柵極到源極電容過(guò)多的限制。

通過(guò)探測(cè)或引線鍵合,可以輕松且可重復(fù)地測(cè)試芯片。

鋁/硅結(jié)的電氣特性也得到了表征,并顯示了預(yù)期的結(jié)果。我們可以在鋁和硅之間建立三個(gè)這樣的基本接觸。鋁相對(duì)于硅來(lái)說(shuō)是P型的,所以只要鋁與輕度摻雜的N硅接觸就會(huì)形成肖特基二極管。有時(shí)我的器件顯示出隧道特性,而不是預(yù)期的二極管,因此我推斷,如果同一器件在高溫(>1000ºC)下處理較長(zhǎng)時(shí)間,由于N型摻雜物在SiO2中的溶解度增加,硅表面的氧化程度增加,導(dǎo)致晶圓表面的磷"堆積"。這在表面形成了一個(gè)"N+"區(qū)域,較高的摻雜物濃度產(chǎn)生了一個(gè)不斷減少的耗竭層,這與一個(gè)小的勢(shì)能障礙有關(guān)(電子可以很容易地穿過(guò)它),解釋了對(duì)稱的IV曲線。

此外,可以破壞性地測(cè)試柵極氧化物介電擊穿電壓。對(duì)于高質(zhì)量的SiO2,這應(yīng)該略高于 1V/nm,并且很容易通過(guò)從 0V 掃描 Vgs 并注意大電流流過(guò)時(shí)進(jìn)行測(cè)試(在正常操作中,柵極是絕緣的,應(yīng)該沒(méi)有電流流過(guò))。

該圖顯示了 25nm 厚的柵極器件在 21.7V 時(shí)發(fā)生的柵極介電擊穿,表明良好的熱生長(zhǎng)氧化物質(zhì)量可以通過(guò)在具有較高氮含量的氣氛中生長(zhǎng)來(lái)改善。

還可以演示開關(guān)和差分放大器特性。右側(cè)的軌跡顯示了配置為全差分放大器的芯片輸出,將 1kHz 和 50kHz 正弦波混合(相加/相減)在一起。

要測(cè)試的最后一個(gè)特性是低泄漏、完全絕緣的柵極,這是真正MOSFET 操作的主要要求之一。如您所見,我能夠?yàn)槠骷臇艠O充電并通過(guò)我的指尖通過(guò)高阻抗連接將其打開,并且FET 的 1, 0 狀態(tài)由于電荷留在柵極上而“鎖定” FET 并且沒(méi)有消散路徑。

很久以前,一些放大器受到"爆米花 "或爆裂噪聲的困擾,人們認(rèn)為這是由半導(dǎo)體內(nèi)部缺陷的隨機(jī)事件引起的。這表現(xiàn)為輸出中巨大的階躍脈沖變化,由于材料純度和加工清潔度的提高,在現(xiàn)代集成電路中幾乎已經(jīng)消除了。然而,我做的一些器件表現(xiàn)出大量的爆米花噪聲,如下圖視頻所示(差分對(duì)中的噪聲在范圍上被放大,零輸入產(chǎn)生數(shù)百毫伏的輸出)。關(guān)于這種類型的噪聲,我最喜歡的一句話是一位工程師在提到MAX9776時(shí)說(shuō)的:"你可以用青蛙腿和秒表來(lái)測(cè)量它。"我的顯然屬于這種類型...