柯尼卡美能達芯片設計 C++高級綜合(HLS)流程全視(附:白皮書下載)

2019-07-19 12:51:57 EETOP高級綜合(HLS)現在是公認的設計范例,柯尼卡美能達的工程師多年來一直使用C++作為設計輸入語言,同時設計多功能外圍設備,專業數字打印機,醫療保健用超聲設備和其他產品。

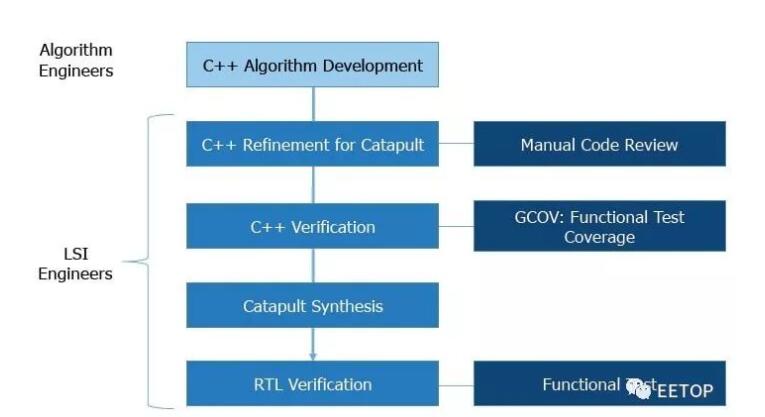

所使用的原始C++設計流程如下所示,使用Mentor的Catapult工具,其仿真時間比RTL快100倍:

即使有這種C++流程,也有一些額外的步驟和問題,例如:

手動檢查算法代碼需要花費太多時間。

使用GCOV進行代碼覆蓋不會產生對可綜合C ++代碼的深入了解,也無法表達,切換和功能覆蓋分析。

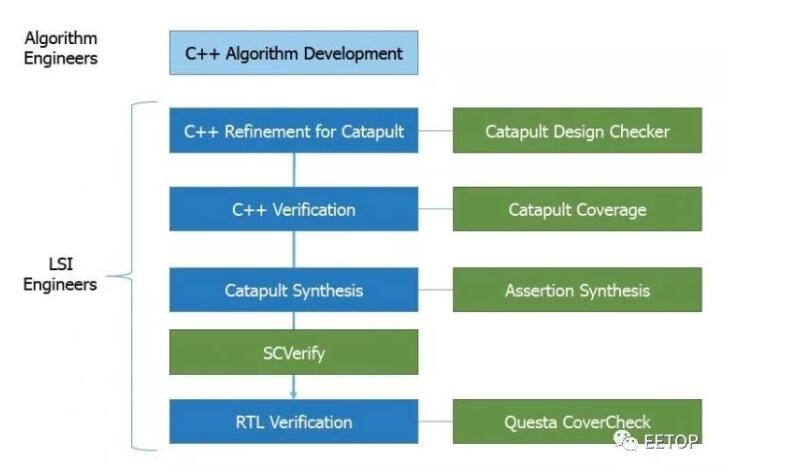

Catapult系列工具不僅僅是C ++綜合,因此添加了更多這些工具,如下面以綠色突出顯示:

讓我們解釋其中一些方框正在做的更詳細:

Catapult Design Checker – uncover coding bugs using static and formal approaches.

Catapult Coverage – C++ coverage analysis, knowing about hardware.

Assertion Synthesis – auto-generation of assertions in the RTL.

SCVerify – creates a smoke test, and sets up co-simulation of C++ and RTL, comparing for differences.

Questa CoverCheck – finds unreachable code using form RTL coverage analysis

檢查C++代碼

因此,這個更新的流程看起來非常自動化,但仍然存在問題。例如,C++是不定時的,而RTL具有時鐘周期的概念,因此在RTL仿真期間可能出現不匹配。Catapult Design Checker在這里發揮作用,當在幾個柯尼卡美能達設計上運行時,該工具檢測到大約20次違反陣列綁定讀取(ABR)規則,其中數組索引超出界限。這是一個ABR違規示例:

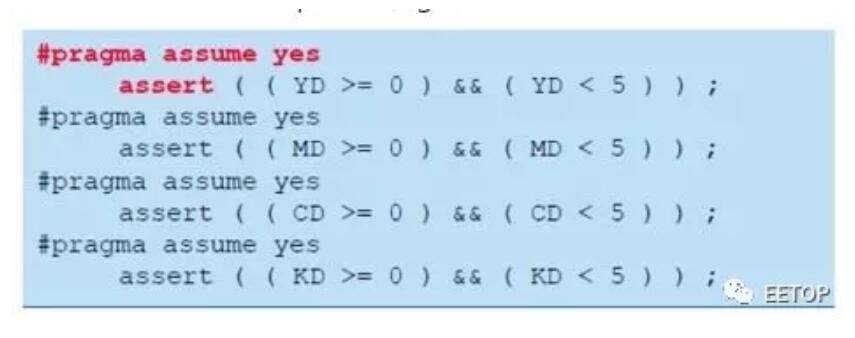

解決這個問題的方法是在C++代碼中添加斷言:

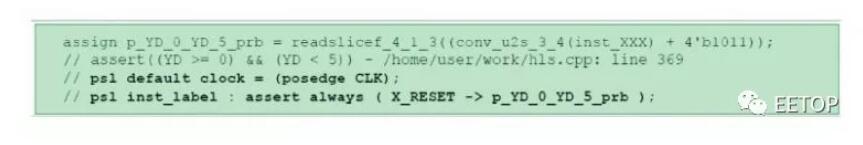

使用C++斷言,您將在模擬過程中看到任何違規,而Assertion Synthesis將添加如下所示的在RTL測試期間使用的PSL代碼。

代碼覆蓋范圍

Catapult Coverage(CCOV)工具了解硬件,而原始GCOV工具則不然,因此CCOV支持以下內容:

Statement

Branch

Focused Expression

Index Range

Toggle Coverage

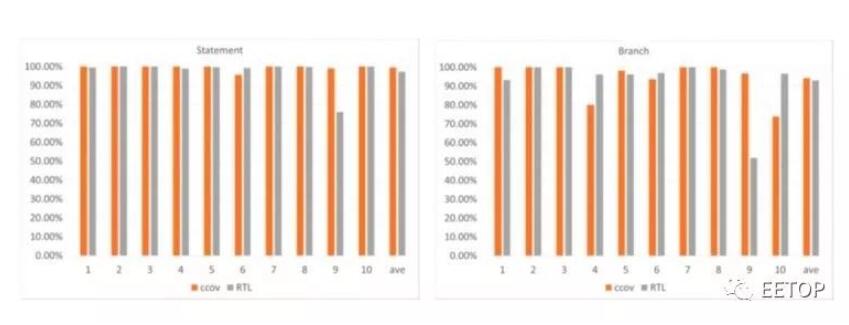

但仍然存在一個重要問題,C++覆蓋范圍與實際RTL覆蓋范圍有多接近?SCVerify工具用于10個設計,以比較報表和分支覆蓋的結果,下面顯示密切相關,平均報表覆蓋率為97%,CCOV的分支覆蓋率為93%。

無法訪問的代碼

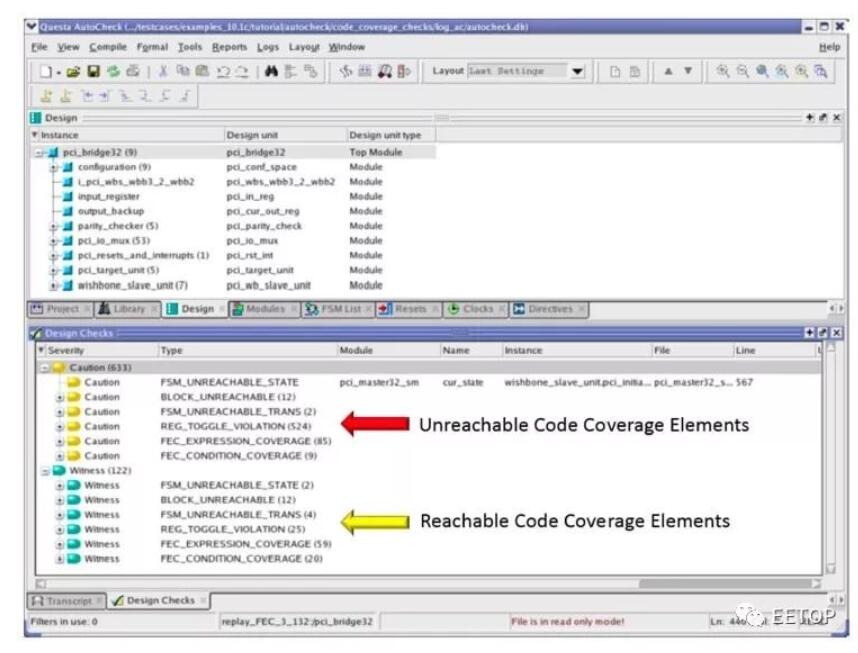

有任何無法訪問的代碼是一個問題,因此使用Questa CoverCheck工具有助于識別,然后有選擇地從統一覆蓋數據庫(UCDB)中刪除。這是工程師在運行CoverCheck后會看到的內容,黃色顯示的項目無法訪問:

一旦設計人員看到無法訪問的代碼,他們就會確定這是一個真正的錯誤還是可以放棄,如果元素可以訪問,那么就為它創建一個新的測試。

在高級別驗證期間,LSI工程師正在嘗試達到覆蓋目標,他們可以要求算法開發人員添加更多測試。將來,算法開發人員可以使用CCOV來實現代碼覆蓋,而LSI工程師則使用剩余的Catapult工具來實現RTL閉包。

結論

多年來,Takashi Kawabe在柯尼卡美能達的團隊成功地在C++流程中使用了Catapult工具,以便比傳統的RTL輸入方法更快地將產品推向市場。通過使用全套Catapult工具,他們在C++中的仿真速度比在RTL級別快100倍,并且已經證明C++級別的signoff現在已經可以實現。

白皮書下載

更詳細的可以下載相關白皮書了解。