超高速SerDes在芯片設(shè)計中的挑戰(zhàn)

2019-06-26 13:00:58 EETOP串行器/解串器用于將并行數(shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù),使設(shè)計人員無需增加引腳數(shù)即可加速數(shù)據(jù)通信。但隨著數(shù)據(jù)量的增加,以及隨著越來越多的設(shè)備連接到Internet并最終連接到云,越來越需要更快地移動更多數(shù)據(jù)。這反過來又使SerDes設(shè)計變得越來越復(fù)雜。

對高速SerDes的大部分需求來自大型數(shù)據(jù)中心,目前最先進的吞吐量為100 Gbps。最近開始想400Gbps進發(fā)。甚至人們已經(jīng)開始探路800 Gbps的支持。

因此,IEEE和光互聯(lián)網(wǎng)論壇的標準在單個通道上定義越來越高的數(shù)據(jù)速率,這允許將數(shù)據(jù)聚合到更大的系統(tǒng)。然后,為了將SerDes技術(shù)提升到更高的性能水平,其中一項重大進步是采用了高于28Gbps的PAM4信令。

Rambus業(yè)務(wù)運營高級主管Sunil Bhardwaj說:“隨著串行數(shù)據(jù)速率達到每通道100多Gbps,帶寬增加引起的信號損傷促使采用PAM4或4級脈沖幅度調(diào)制。” “與NRZ(不歸零)相比,PAM4通過在每個符號中傳輸兩位來將給定數(shù)據(jù)速率的帶寬減半。這允許在通道中加倍比特率而不會使所需帶寬加倍。例如,使用PAM4信令,56-Gbps比特率以28 GBauds傳輸,并具有14 GHz的奈奎斯特頻率。利用NRZ信令,56 Gbps比特率以56 GBauds傳輸,奈奎斯特頻率為28 GHz。

但有一個權(quán)衡。“多個符號級別使PAM4對振幅噪聲比NRZ更敏感,”他解釋說。“與NRZ相比,PAM4引入了9.6dB的損耗,工作在相同的奈奎斯特頻率。然而,在這些高頻率下,以NRZ奈奎斯特頻率的一半運行的能力使PAM4成為低損耗替代方案。與NRZ一樣,PAM4信號受抖動,信道損耗和符號間干擾的影響。此外,三個眼圖的測量因新的接收器行為而變得更加復(fù)雜,例如三個限幅器閾值,單個限幅器時序偏移,均衡以及時鐘和數(shù)據(jù)恢復(fù)。不出所料,PAM4信號分析從為分析NRZ的抖動和噪聲而開發(fā)的技術(shù)中借鑒了很多。此外,許多NRZ技術(shù)適用于PAM4。

另一個復(fù)雜因素是高速設(shè)計越來越容易受到電磁串?dāng)_問題的影響,ANSYS半導(dǎo)體業(yè)務(wù)部產(chǎn)品營銷經(jīng)理Annapoorna Krishnaswamy指出。

電磁交叉耦合問題變得越來越重要的一些關(guān)鍵因素包括:

隨著時鐘速度的提高,先進的封裝類型以及減小面積的壓力,設(shè)計和驗證高速IC設(shè)計的傳統(tǒng)方法已不再足夠。

設(shè)計的所有方面 - 高速信號/時鐘線,詳細的電源和接地布線,無源器件,甚至封裝層都需要進行詳細建模和驗證。需要對片內(nèi)寄生效應(yīng)進行精確建模,包括自感和互感(RLCk),以完全捕獲從DC到毫米波頻率的電氣行為(適用于5G應(yīng)用)。這對于分析由于通過電源/接地,基板或封裝層的耦合而影響多個鄰近區(qū)域的一個信號的不需要的電磁干擾是至關(guān)重要的。“

這就是為什么準確捕獲電磁(EM)現(xiàn)象(包括電流分布,皮膚和鄰近效應(yīng))對于降低EM串?dāng)_引起的性能降低和高速和低功耗片上系統(tǒng)故障的風(fēng)險至關(guān)重要的原因。EM感知設(shè)計流程有助于減少過度設(shè)計,面積和成本,同時確保設(shè)計的卓越性能,質(zhì)量和可靠性。

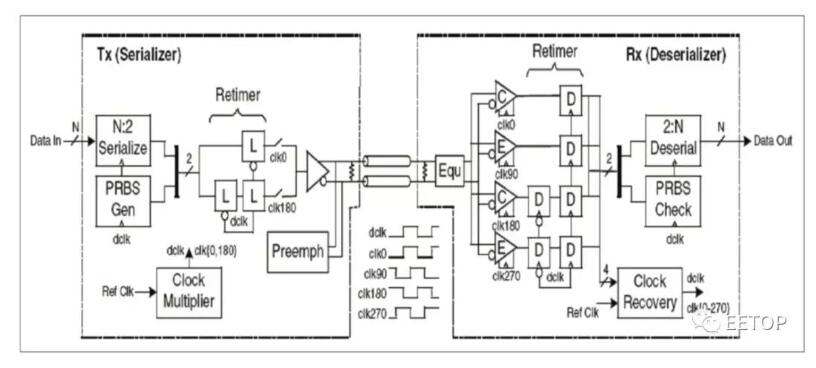

圖1:典型的高速I/O架構(gòu)

設(shè)計挑戰(zhàn)

Adesto的工程師Martin Hujer表示,對于高速SerDes,挑戰(zhàn)通常圍繞功耗,時鐘分配(模擬時鐘樹),所用封裝類型以及寄生效應(yīng)。“然后,PCB上有布線,支持測試模式和測試模式,以及快速數(shù)字邏輯。此外,還需要一種符合更高級別串行協(xié)議的數(shù)字控制器。在集成到定制芯片中時,必須考慮所有這些挑戰(zhàn)。根據(jù)應(yīng)用和客戶要求,可能存在替代解決方案的潛力,您可以在一個或多個高速串行通道和速度較慢但仍然很快的并行總線之間進行權(quán)衡。“

Rambus的Bhardwaj說,與此同時,隨著頻率的增加,每種類型的抖動,ISI,振鈴,串?dāng)_,接地反彈,電源噪聲的損失都會更加嚴重。“因此,信號完整性(SI)現(xiàn)在是系統(tǒng)架構(gòu)無可否認的關(guān)鍵方面。專業(yè)SI工程師在整個設(shè)計周期中定期與系統(tǒng)架構(gòu)師,電路設(shè)計師和系統(tǒng)工程師進行交互。為了滿足當(dāng)今高性能系統(tǒng)的需求,必須制作整個鏈路的SI模型,包括發(fā)射器,接收器,時鐘和通道。反過來,全面的鏈路分析會影響一系列設(shè)計架構(gòu),包括均衡,時鐘,時序校準,以及編碼和/或糾錯。“

此外,他還必須仔細實施封裝設(shè)計,以滿足高頻率和嚴格的電氣性能要求。“必須特別注意封裝中的高速I / O和模擬電源,使用電磁(EM)模擬器設(shè)計封裝基板,以驗證封裝設(shè)計是否滿足各種要求,包括所有交叉通話隔離,阻抗和S參數(shù),以及電源電感。“

與此同時,工程團隊希望他們的IP具有已知的故障率和壽命,以便在汽車和其他安全關(guān)鍵應(yīng)用中提供可靠的服務(wù)。“隨著CMOS和finFET技術(shù)穩(wěn)步發(fā)展到更小的特征尺寸,隨機元件的變化和布局中的系統(tǒng)偏移變得更加重要,” Silicon Creations業(yè)務(wù)開發(fā)副總裁Andrew Cole說。“我們必須仔細檢查電路可靠性故障模式和網(wǎng)表的蒙特卡羅模擬,通過包括更精細的布局寄生效應(yīng)來實現(xiàn)更大的響應(yīng)。因此,即使智能網(wǎng)表減少,我們也看到設(shè)計驗證CPU時間從28nm增加到5nm,增加了兩個數(shù)量級。“

換句話說,高性能SerDes的設(shè)計挑戰(zhàn)類似于轉(zhuǎn)移到finFET的設(shè)計挑戰(zhàn),尤其是在成品率、可靠性、大型網(wǎng)表和長仿真時間方面。除了我們之前討論過的finFET挑戰(zhàn),SerDes對高速信號也有ESD要求。對于靜電放電,F(xiàn)inFET器件的魯棒性不如平面晶體管。因為它們的三面被氧化物包圍,所以它們也不會散熱。這為在高級節(jié)點中實現(xiàn)非常高的數(shù)據(jù)速率帶來了另一個困難的設(shè)計挑戰(zhàn)。

今天的finFET工藝并未顯著提升晶體管性能。真正的改進是在芯片上的可用空間中。但是,持續(xù)的功能縮減確實使設(shè)計這些設(shè)備變得更加困難,并且必須創(chuàng)建新的電路架構(gòu)來應(yīng)對這些挑戰(zhàn),Analog Bits執(zhí)行副總裁Mahesh Tirupattur指出。

“另一個重大挑戰(zhàn)是為EM設(shè)計,”Tirupattur說。“這些導(dǎo)線的電阻更大。因此,導(dǎo)線的載流能力大大降低。為高性能設(shè)計提供電源仍然是布局布線拓撲中的一個挑戰(zhàn)。”

汽車應(yīng)用中的SerDes

由于如此多的關(guān)注轉(zhuǎn)向汽車應(yīng)用,環(huán)境壓力也在SerDes功能中發(fā)揮作用。不同的操作條件可能會不同地影響設(shè)

人們將在數(shù)據(jù)中心使用的技術(shù)節(jié)點(7nm到5nm),與他們可能用于汽車應(yīng)用的技術(shù)節(jié)點不同。” Mentor的Tegethoff說。“在汽車應(yīng)用中,首先要取決于它是否是一個安全項目,然后開發(fā)人員將對它做各種額外的事情。但如果一個人只是在做IP,他們必須確保把所有這些都考慮進去,因為他們不一定能控制它的發(fā)展方向。他們希望能夠?qū)P推廣到不同的地方。”

他指出,由于對設(shè)計的可靠性和魯棒性有如此多的附加要求,不同的設(shè)計團隊將根據(jù)安全標準或客戶的要求遵循不同的協(xié)議。“例如,(電路)老化將用于任何通常用于汽車功能安全類型應(yīng)用的任何東西。像意法半導(dǎo)體(STMicroelectronics)或安森美半導(dǎo)體(ON Semiconductor)這樣的公司希望確保如果事情惡化,它們會優(yōu)雅地降級并且不會引起問題。也就是說,沒有一個簡單的答案。根據(jù)應(yīng)用的不同,它會有所不同。“

先進節(jié)點下的SerDes

當(dāng)涉及到將SerDes移動到更先進的技術(shù)節(jié)點時,會發(fā)生很大的變化。

“對于7nm的SerDes,設(shè)計工程師遇到的最頭疼的問題之一就是工藝復(fù)雜性。自180nm以來,層數(shù)增加了5倍,“Tegethoff說。“設(shè)計規(guī)則也成為一項挑戰(zhàn)。在模擬設(shè)計方面,模擬電路是否與數(shù)字電路一樣可擴展?你能依靠你對模擬數(shù)字化的經(jīng)驗法則嗎?并不是的。如果你看一下從180nm到7nm的數(shù)字縮放,它大概是660比1,相同技術(shù)比較的模擬縮放大約是10比1,所以它的擴展幾乎沒有那么多。“

同樣困擾SerDes設(shè)計人員的是先進節(jié)點中的互連,它影響電路中的信號傳輸和模擬時間。“你需要對所有電容和電阻進行完整的模擬提取,”他說。“然后你必須仿真模擬設(shè)備噪音,確保它在所有工藝角運行,還要進行蒙特卡羅仿真等待。總之設(shè)計人員最終會運行大量仿真,并且耗費大量的時間。“

并不是所有這些都可以通過工具來完成。與許多工程挑戰(zhàn)一樣,對高性能SerDes最真實的優(yōu)化是結(jié)合使用自動化工具的設(shè)計人員的專業(yè)知識。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章