“化圓為方”,CoPoS先進(jìn)封裝技術(shù)賦能AI芯片設(shè)計

2024-12-16 10:57:45 周菊香,EETOP晶圓,是圓形的;芯片,是方形的。業(yè)內(nèi)人士對此,可謂是常識性的認(rèn)知。

晶圓設(shè)計為圓形,而非方形,跟它的生產(chǎn)方式密不可分。晶圓是通過直拉法(Czochralski process)從高純度的硅棒中生長出來的。在直拉法中,硅材料在籽晶上旋轉(zhuǎn)生長,形成圓柱形的單晶硅棒,然后切割成圓形的晶圓。圓形是給定周長下面積最大的形狀,這意味著在晶圓上可以切割出更多的方形芯片,從而提高材料的利用率。

隨著摩爾定律的停滯和先進(jìn)制造與封裝工藝成本的顯著攀升,圓形晶圓的面積浪費問題被提上日程。那么,化圓為方,是否可行?

近日,Manz亞智科技在蘇州召開了技術(shù)論壇,論壇以“‘化圓為方’解鎖高效封裝 ? CoPoS賦能芯未來”為主題。會上,Manz集團(tuán)亞洲區(qū)總經(jīng)理林峻生、 Manz集團(tuán)亞洲區(qū)銷售副總經(jīng)理簡偉銓、Manz集團(tuán)亞洲區(qū)研發(fā)部協(xié)理李裕正博士聯(lián)合分享,介紹了先進(jìn)封裝市場趨勢、化圓為方技術(shù)核心,以及Manz亞智科技的優(yōu)勢和機(jī)會。

大芯片和異構(gòu)集成

從傳統(tǒng)封裝到先進(jìn)封裝,行業(yè)經(jīng)歷了從引線框架封裝到倒裝芯片封裝,再到晶圓級封裝的演變。

l打線封裝Wire-Bond:一種傳統(tǒng)的半導(dǎo)體封裝技術(shù),使用細(xì)金屬線(如金絲、銅絲或鋁絲)通過熱、壓力、超聲波能量將半導(dǎo)體器件芯片表面的電極引線與基板或引線框架外引線相連接起來,實現(xiàn)芯片與基板間的電氣互連和芯片間的信息互通的技術(shù)。

l覆晶封裝Flip-Chip:一種先進(jìn)的半導(dǎo)體封裝技術(shù),將芯片的有源面(即邏輯面)朝下,通過在芯片的I/O pad上沉積凸塊(bump),然后將芯片翻轉(zhuǎn)過來使凸塊與基板直接連接。盡管Flip-Chip技術(shù)并非新技術(shù),但它仍然保持著高達(dá)19%的年復(fù)合成長率,顯示出其在封裝市場中的強勁動力。

l扇出型晶圓級封裝 / 扇出型面板級封裝FOWLP/ FOPLP:兩種先進(jìn)的封裝技術(shù)。FOWLP是一種在傳統(tǒng)晶圓級芯片尺寸封裝(WLCSP)基礎(chǔ)上發(fā)展起來的封裝技術(shù),它允許重布線層(RDL)延伸至芯片邊緣之外,可提供更高的I/O密度和布線靈活性;FOPLP是一種在2015年由Fraunhofer IZM研究所的Tanja Braun所研究的前沿技術(shù),它基于重新布線層(RDL)工藝,將芯片分布在大面板上進(jìn)行互連,使得芯片成品的高度更低,且不需要基板,從而降低了成本并提高了設(shè)計的靈活性;

l2.5D(CoWoS)/3D封裝:通過在垂直方向上堆疊芯片來實現(xiàn)更高的集成度和性能。2.5D封裝通常涉及將芯片放置在硅中介層(interposer)上,通過導(dǎo)電凸塊或TSV(Through Silicon Via)技術(shù)將組件堆疊在中介層上;3D封裝技術(shù)允許在不改變封裝體尺寸的前提下,在同一個封裝體內(nèi)垂直方向疊放兩個以上芯片。

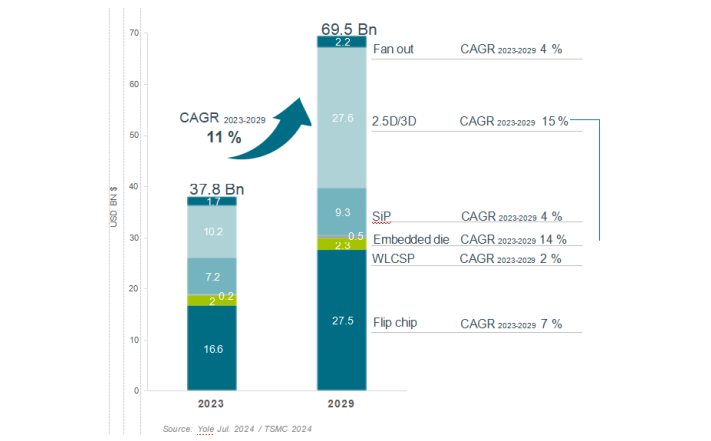

Yole Intelligene數(shù)據(jù)顯示,2023-2029年先進(jìn)封裝市場規(guī)模會從378億美元擴(kuò)增至695億美元,CAGR年復(fù)合增長率11%。Yole也明確了包括flip-chip芯片倒裝、Fan-out扇出型封裝、2.5D/3D等先進(jìn)封裝的發(fā)展前景。先進(jìn)封裝以其增強功能、性能,降低成本的優(yōu)勢正在推動半導(dǎo)體領(lǐng)域的創(chuàng)新。

隨著人工智能(AI)和數(shù)字化的加速部署,對高性能計算和數(shù)據(jù)處理的需求不斷增長。大模型訓(xùn)練任務(wù)所需的算力每3.43個月翻一倍,遠(yuǎn)超過摩爾定律的增長速度。與此同時,隨著摩爾定律的放緩,單純依靠提升工藝來提升芯片性能的方法已經(jīng)無法充分滿足時代的需求。這些由AI、HPC、汽車和AI PCs所驅(qū)動的應(yīng)用場景給處理器帶來了非常大的工作負(fù)載,算力需求更是呈指數(shù)級增長。行業(yè)領(lǐng)導(dǎo)者正越來越多地采用大芯片和異構(gòu)集成策略,使用先進(jìn)封裝來補充前端擴(kuò)展。這已成為制造廠、OSAT、IDMs和芯片設(shè)計關(guān)注的焦點。

CoWoS產(chǎn)能吃緊,CoPoS力當(dāng)先鋒

隨著高性能計算和人工智能領(lǐng)域的需求增長,CoWoS技術(shù)因其高集成度和優(yōu)異性能而受到越來越多的關(guān)注。CoWoS(Chip-on-Wafer-on-Substrate)技術(shù)是臺積電為了克服摩爾定律即將面臨的物理限制,于2013年開發(fā)出的一種先進(jìn)封裝技術(shù)。但由于成本較高,初期只有少量采用Xilinx。

隨著時間的推移,CoWoS技術(shù)得到了進(jìn)一步的發(fā)展與應(yīng)用。2016年,臺積電發(fā)布了第二代CoWoS方案,硅中介層尺寸大約是1.5倍reticle limit,并包含4個HBM2,總?cè)萘繛?6GB。2019年,臺積電開發(fā)的第四代CoWoS裝有一個邏輯芯片和6個HBM2,總?cè)萘繛?8GB(384Gbit),是第三代容量的3倍。2021年,臺積電發(fā)布第五代CoWoS技術(shù),其晶體管數(shù)量是第三代的20倍。CoWoS-S5通過將插層尺寸擴(kuò)大到3倍reticle limit(2500 mm2),可在單個插層上集成3個或更多邏輯芯片組和8個HBM。

目前AI芯片封裝以臺積電的CoWoS技術(shù)為主。臺積電正在擴(kuò)大CoWoS封裝產(chǎn)能以應(yīng)對市場需求。到2024年底,臺積電CoWoS月產(chǎn)能約3.5萬片;全年產(chǎn)出約30-32萬片;預(yù)期2025年CoWoS月產(chǎn)能提升至6萬片以上。

不過,臺積電CoWoS的產(chǎn)能增長,預(yù)計仍然無法滿足市場的需求。自2022年11月,Open AI發(fā)布ChatGPT一來,人工智能、生成式AI需求在全球范圍內(nèi)就呈爆發(fā)式增長。2023年全球人工智能芯片市場營收為202.8億元,預(yù)計2024至2033年復(fù)合增長率為38.16%。這一增長,也引發(fā)了AI芯片的短缺問題。而AI芯片的短缺,主要就是CoWoS先進(jìn)封裝產(chǎn)能不足導(dǎo)致的。

DIGITIMES Research指出,由于云端AI加速器需求的強勁增長,預(yù)計到2025年,全球?qū)oWoS及類似封裝產(chǎn)能的需求可能會上升113%。臺積電CoWoS產(chǎn)能限制及AI芯片需求激增,AI芯片廠商正積極探索替代方案。

作為板級RDL方案產(chǎn)業(yè)化的領(lǐng)導(dǎo)者之一,Manz亞智科技認(rèn)為,在當(dāng)前CoWoS產(chǎn)能欠缺下,CoPoS(Chip-on-Panel-on-Substrate)技術(shù)概念是驅(qū)動先進(jìn)封裝進(jìn)階的趨勢。

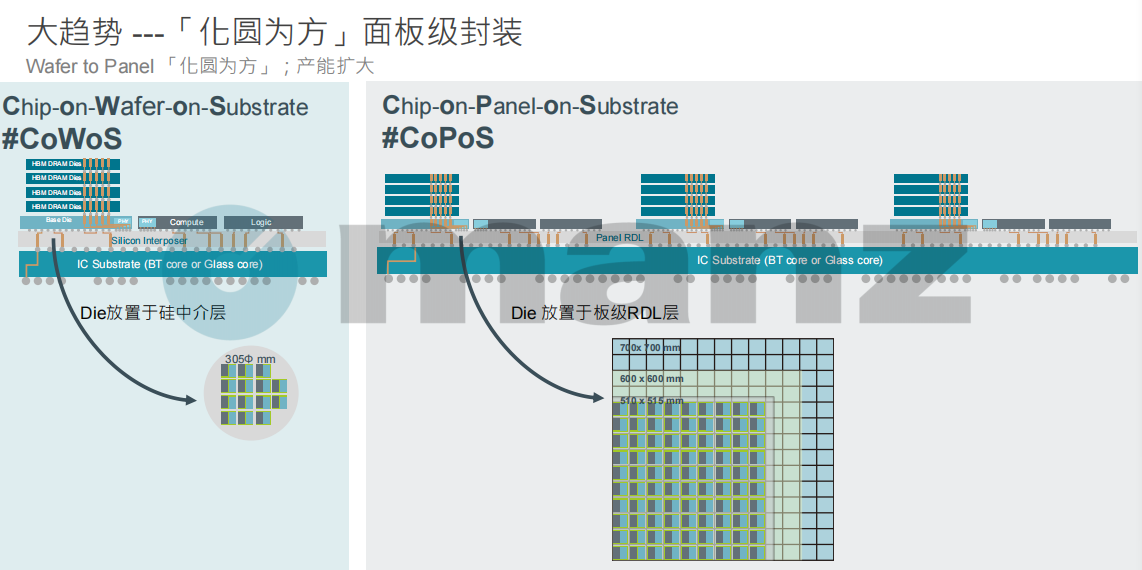

CoPoS 是CoWoS的面板化解決方案。作為2.5D封裝的另外一種選擇,其硅中介層替換成有機(jī)材料中介層,BT基板替換成玻璃基板,在各種互連架構(gòu)中實現(xiàn)的再分配層,包括RDL interposer (CoWoS-R/ CoWoS-L)和玻璃芯基板上的RDL(玻璃版的FC-BGA)——這也是當(dāng)前業(yè)界形成的共識,以應(yīng)對下一代更高密度的AI芯片。

李裕正博士介紹說:“傳統(tǒng)的wire bond(引線鍵合)、QFN,甚至flip-chip BGA封裝方式發(fā)生了改變,走向了板級封裝。CoPoS就是將中介層進(jìn)行'面板化',做到所謂Panel RDL;或者說將die放到'板級RDL層'之上。”

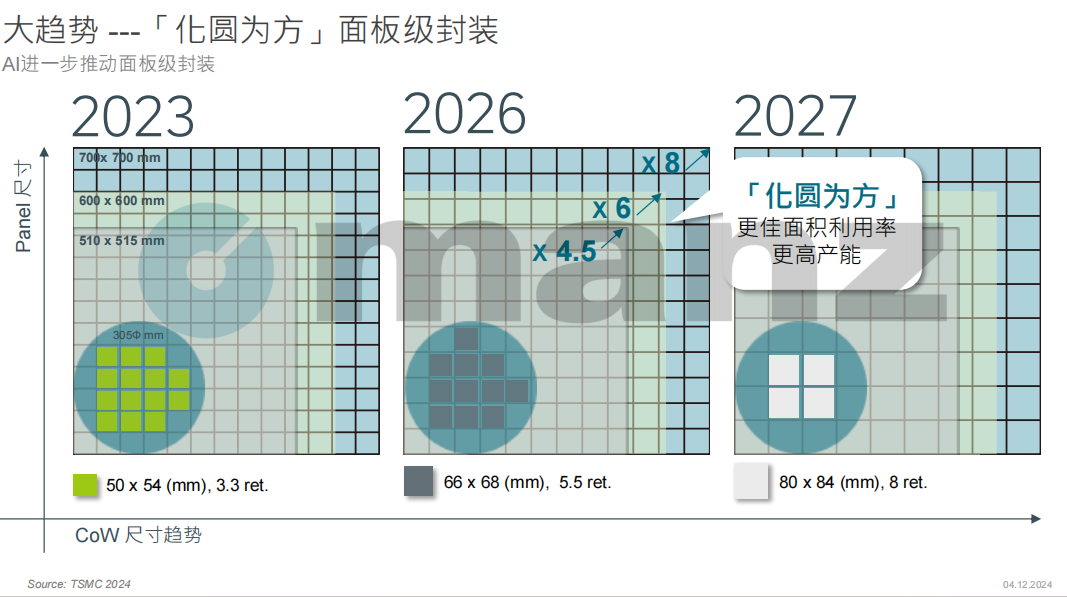

基于CoWoS方式進(jìn)行封裝,按照AI芯片未來可能會達(dá)到80x84mm的大型die size的趨勢,12寸晶圓只能放下4片這樣的die;再加上良率問題,單片芯片的成本會顯著提升。如果將“W”換成“P”,自然能達(dá)成更高的面積利用率及顯著提升的產(chǎn)能。即便是510x515mm的面板,可容納的die數(shù)量也有300mm晶圓的數(shù)倍之多。

相對于CoWoS技術(shù),CoPoS技術(shù)具有更高的靈活性、可擴(kuò)展性和成本效益。這種“化圓為方”的封裝革新,有助于提高封裝效率和加速芯片產(chǎn)能的釋放。

先進(jìn)板級封裝市場

半導(dǎo)體行業(yè)發(fā)展的驅(qū)動力是降低芯片生產(chǎn)成本,而板級封裝(FOPLP) 突破硅片面積的限制,在芯片尺寸變大的趨勢下,應(yīng)用方型基板以增加產(chǎn)能,無疑是實現(xiàn)降本增效的關(guān)鍵解決方案之一。

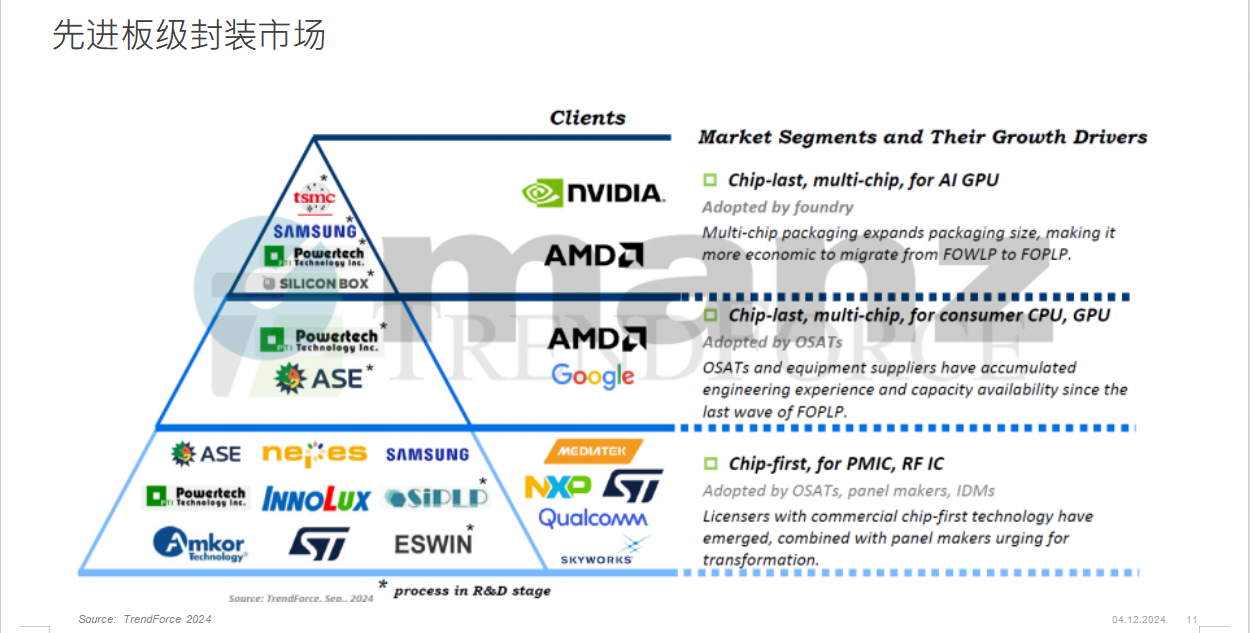

板級封裝市場的主要參與者包括半導(dǎo)體OSAT(外包半導(dǎo)體組裝測試廠商)、IDM(集成器件制造商)和晶圓代工廠(Foundry),以及跨界參與的面板廠。簡偉銓詳細(xì)介紹了目前板級封裝的市場應(yīng)用情況。

如上圖,最下層,是板級封裝技術(shù)目前最廣泛的應(yīng)用,主要是PMIC, RF IC等芯片類型,線寬線距約在10μm-10μm或15μm-15μm左右(chip-first是指先放芯片,再構(gòu)建RDL層;chip-last則與之相反)。目前,包括OSAT封測廠、面板制造商、IDM等市場角色已經(jīng)在相對廣泛地應(yīng)用該技術(shù)。圖片中間層則指向消費級CPU、GPU,這是技術(shù)要求更高的產(chǎn)品類型。林峻生特別提到,這部分市場雖然目前也存在良率挑戰(zhàn),但在5μm~2μm線寬線距級別的產(chǎn)品已經(jīng)在“小批量生產(chǎn)”。最上層則是面向HPC市場的諸如AI GPU等高端芯片類型。這類芯片的特點是芯片面積更大,故而晶圓級封裝的短板更明確的暴露;或者說板級封裝在成本和效率方面的優(yōu)勢會體現(xiàn)得更明確。

扇出板級封裝(FOPLP)是扇出晶圓級封裝技術(shù)的一種延伸和發(fā)展,將多個芯片、無源組件和互連集成在一個封裝內(nèi),并以重新布線層(RDL)工藝,將芯片重新分布在具有面積利用率優(yōu)勢的方形基板上進(jìn)行互連,是具備產(chǎn)能優(yōu)勢的先進(jìn)封裝技術(shù)。它們的主要區(qū)別在于載板:晶圓級封裝使用的是圓形的晶圓作為基板;而板級封裝則轉(zhuǎn)換為使用大尺寸的方形面板作為基板。

不過,雖然晶圓級封裝工藝流程與板級封裝本身沒有太大差異,但由于載體不同,需要獨立開發(fā)生產(chǎn)設(shè)備及相應(yīng)系統(tǒng)。林峻生表示:“在‘化圓為方’的過程中,畢竟‘圓’已經(jīng)發(fā)展了幾十年,要變?yōu)椤健膊⒉皇悄敲慈菀住?/span>板級封裝在實現(xiàn)上還存在挑戰(zhàn)。無論是材料,還是設(shè)備選取,做到更細(xì)的線寬線距還是需要更進(jìn)一步的驗證和實現(xiàn)。”

玻璃基板正在成為先進(jìn)封裝的關(guān)鍵

基板材料是半導(dǎo)體封裝的重要材料 ,為芯片提供電連接、保護(hù)、支撐和散熱等功能。在半導(dǎo)體封裝技術(shù)的早期,陶瓷封裝基板占據(jù)了主導(dǎo)地位。到20世紀(jì)80年代,塑料封裝基板應(yīng)運而生,取代了成本高、加工難度大的陶瓷封裝基板。進(jìn)入20世紀(jì)90年代,第三代封裝技術(shù)面陣式封裝開始流行。隨著半導(dǎo)體技術(shù)的進(jìn)步,對于封裝基板的要求也越來越高。近年來,隨著多芯片封裝技術(shù)的興起,第四代封裝基板也應(yīng)運而生。這種封裝方式采用硅中介層作為子板,將多個裸芯片安裝在上面,并通過凸塊將配備有外部電極的主板連接至中介層。

隨著大算力需求的不斷增長,業(yè)界一致認(rèn)為玻璃基板將幫助芯片行業(yè)達(dá)到新的高度!玻璃基板技術(shù)作為有機(jī)RDL中介層的潛在繼任者,提供了更好的電氣性能、更精細(xì)的RDL能力和更低的熱膨脹系數(shù)(CTE)。各大企業(yè)正積極布局玻璃基板,以應(yīng)對未來高性能計算和AI芯片的需求。2023年9月,英特爾推出了基于下一代先進(jìn)封裝的玻璃基板開發(fā)的最先進(jìn)處理器。英特爾預(yù)計到2030年末,半導(dǎo)體行業(yè)可能會達(dá)到其使用有機(jī)材料在硅封裝上縮放晶體管的極限。此外,臺積電也已組建專門的團(tuán)隊探索FOPLP技術(shù),并大力投資玻璃基板研發(fā)。

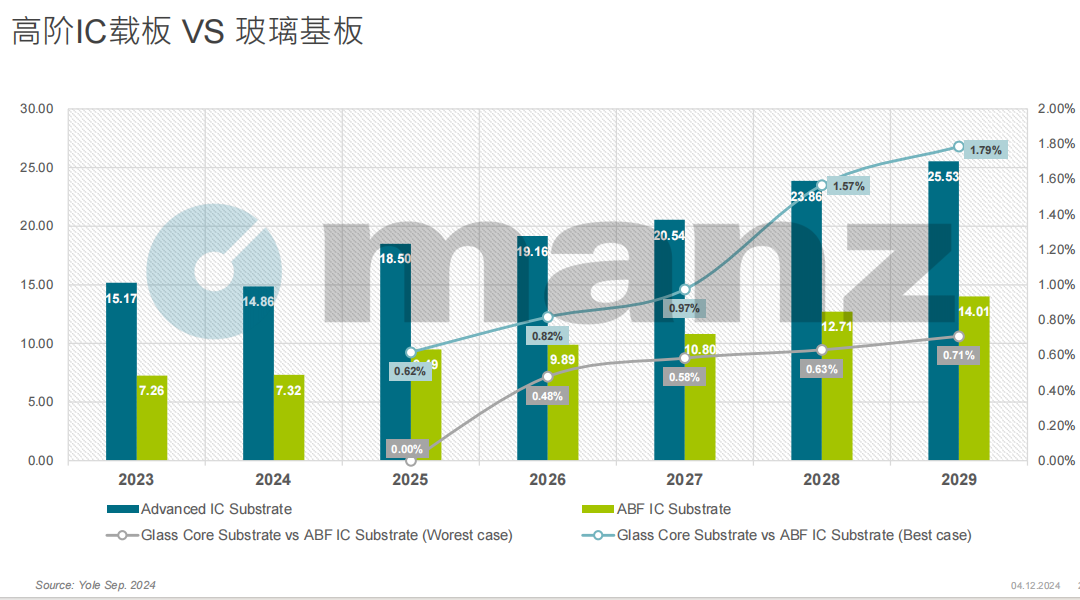

李裕正博士分享說:“先進(jìn) IC 載板市場選擇玻璃和具有挑戰(zhàn)性的有機(jī)基板以增加效能。相對于有機(jī)載板,玻璃基板適用于需要更大體積封裝、更高速度的應(yīng)用和工作負(fù)載,如數(shù)據(jù)中心、AI、繪圖處理芯片等。且玻璃載板耐熱性好,可承受高溫,具有更佳的熱穩(wěn)定性和機(jī)械穩(wěn)定性,其功耗低,適合長時間高效運行。”

Manz亞智科技認(rèn)為玻璃基板是其未來。隨著中介層/有機(jī)基板將切換成玻璃, Manz亞智科技也將RDL工藝實現(xiàn)于510mm x 515mm的玻璃基板,實現(xiàn)高帶寬、高密度的D2D互連。這一特性在AI計算中尤為關(guān)鍵,能夠有效滿足數(shù)據(jù)傳輸與處理的迫切需求。另外,針對不同類型、不同厚度的玻璃達(dá)成內(nèi)接導(dǎo)線金屬化制程與TGV(Through Glass Vias)制程技術(shù),滿足高縱深比的直通孔、高真圓度等制程需求,也是Manz亞智科技的優(yōu)勢所在。

憑借在RDL領(lǐng)域的優(yōu)勢布局,針對RDL增層工藝搭配有機(jī)材料和玻璃基板的應(yīng)用,Manz亞智科技已經(jīng)成功向多家國際大廠交付了300mm、510mm、600mm及700mm等不同尺寸的板級封裝RDL量產(chǎn)線,涵蓋洗凈、顯影、蝕刻、剝膜、電鍍及自動化設(shè)備。同時,為跨領(lǐng)域客戶快速集成工藝技術(shù)和設(shè)備生產(chǎn),積極助力板級封裝為基礎(chǔ)的未來玻璃基板應(yīng)用于人工智能芯片,讓這一愿景變成現(xiàn)實。

結(jié)束語

隨著中國半導(dǎo)體的崛起,先進(jìn)封裝成為本土最具國際競爭力和先導(dǎo)性的產(chǎn)業(yè)之一。板級封裝成本優(yōu)勢明顯,與晶圓級封裝實現(xiàn)互補,板級封裝是先進(jìn)封裝助力下一代AI芯片的前鋒。頭部先進(jìn)封裝廠憑借先發(fā)優(yōu)勢深度布局了2.5D、及FOPLP產(chǎn)線進(jìn)入大規(guī)模建設(shè)和量產(chǎn)階段,頭部光電顯示面板廠正在轉(zhuǎn)型玻璃基板的研發(fā)試產(chǎn)。

林峻生指出:“面板級封裝將是下一代封裝的新勢頭, Manz從 300mm 到 700mm的 RDL生產(chǎn)制造設(shè)備擁有豐富的經(jīng)驗。Manz亞智科技憑借本土技術(shù)和經(jīng)驗提供定制化解決方案,目前Manz亞智科技單板型PLP RDL技術(shù)已通過L/S 15μm/15μm 的驗證,并處于量產(chǎn)階段;輸送機(jī)類型(直列式)PLP RDL技術(shù)已通過L/S 5μm/5μm 的驗證,也適用于小批量生產(chǎn);CoPoS技術(shù)中針對RDL增層工藝搭配有機(jī)材料和玻璃基板的應(yīng)用生態(tài)系統(tǒng)正在建設(shè)中。未來將繼續(xù)發(fā)揮自身在技術(shù)和市場方面積累的優(yōu)勢,迎接板級封裝和TGV市場的快速成長,并積極推動板級封裝實現(xiàn)產(chǎn)業(yè)化落地,在整個產(chǎn)業(yè)生態(tài)建設(shè)貢獻(xiàn)力量。”

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章