GDDR7規(guī)范重磅發(fā)布!深度解讀

2024-03-10 11:12:32 EETOPJEDEC 董事會主席 Mian Quddus 表示:“JESD239 GDDR7 標(biāo)志著高速內(nèi)存設(shè)計的重大進(jìn)步。隨著向 PAM3 信號的轉(zhuǎn)變,內(nèi)存行業(yè)有了一條新的途徑來擴(kuò)展 GDDR 設(shè)備的性能并推動圖形和各種高性能應(yīng)用的不斷發(fā)展。”

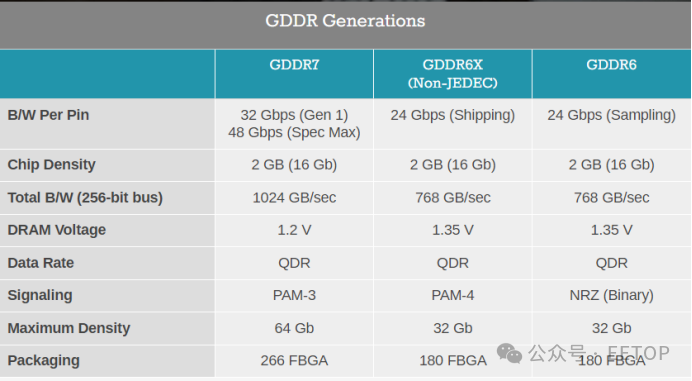

GDDR7 最大的技術(shù)變化是內(nèi)存總線上的兩位不歸零 (NRZ) 編碼轉(zhuǎn)換為三位脈沖幅度調(diào)制 (PAM3) 編碼。這一變化允許 GDDR7 在兩個周期內(nèi)傳輸 3 位數(shù)據(jù),比在相同時鐘速度下運(yùn)行的 GDDR6 多傳輸 50% 的數(shù)據(jù)。因此,GDDR7 可以支持更高的總體數(shù)據(jù)傳輸速率,這是使每一代 GDDR 連續(xù)比其前身更快的關(guān)鍵組件。

第一代 GDDR7 的數(shù)據(jù)傳輸速率預(yù)計約為 32 Gbps/pin,而內(nèi)存制造商此前曾表示,最高可達(dá) 36 Gbps/pin。然而,GDDR7 標(biāo)準(zhǔn)本身為更高的數(shù)據(jù)傳輸速率(高達(dá) 48 Gbps/pin)留出了空間,JEDEC 甚至在其新聞稿中宣稱 GDDR7 內(nèi)存芯片“每臺設(shè)備的速率高達(dá) 192 GB/s [32b @ 48Gbps]” 。值得注意的是,這比 PAM3 信號本身帶來的帶寬增長要高得多,這意味著GDDR7的設(shè)計中有多個級別的增強(qiáng)。

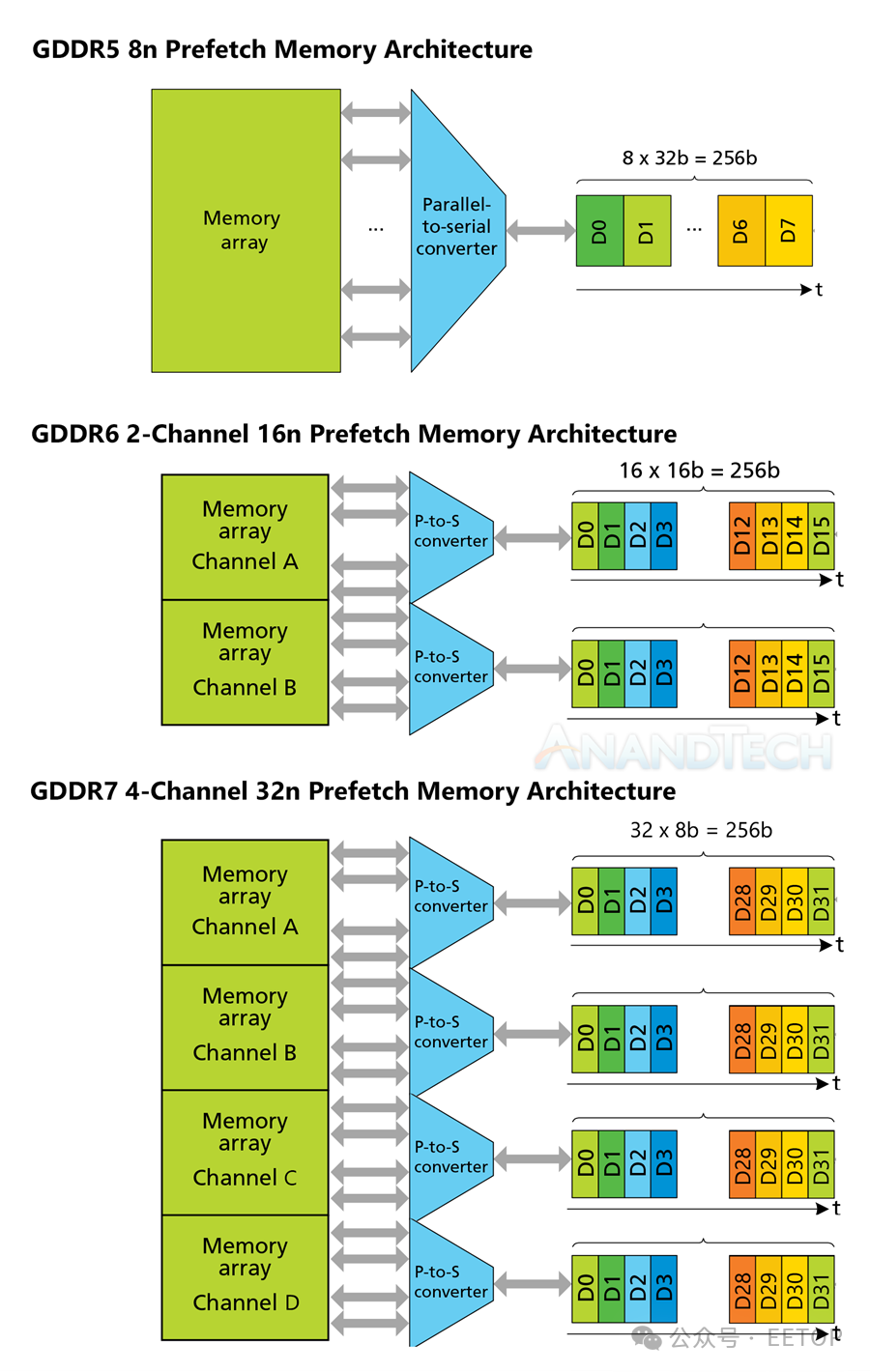

深入研究規(guī)范,JEDEC還再次將單個32位GDDR內(nèi)存芯片細(xì)分為更多的通道。GDDR6提供了兩個16位通道,而GDDR7將其擴(kuò)展到四個8位通道。從終端用戶的角度來看,這種區(qū)別有些武斷——它仍然是一個32位芯片,運(yùn)行速度為32Gbps/pin——但它對芯片內(nèi)部的工作方式有很大的影響。特別是JEDEC保留了GDDR5和GDDR6每通道256位預(yù)取,使GDDR7成為32n預(yù)取設(shè)計。

GDDR 通道架構(gòu)

所有這些的最終影響是,通過將通道寬度減半但保持預(yù)取大小相同,JEDEC 有效地將 DRAM 單元每個周期預(yù)取的數(shù)據(jù)量增加了一倍。這是擴(kuò)展 DRAM 內(nèi)存帶寬的非常標(biāo)準(zhǔn)的技巧,本質(zhì)上與 JEDEC 在 2018 年對 GDDR6 所做的事情相同。但它提醒我們,DRAM 單元的速度仍然非常慢(在數(shù)百兆赫的數(shù)量級上)并且速度并沒有變得更快。因此,提供更快內(nèi)存總線的唯一方法是一次性獲取越來越多的數(shù)據(jù)。

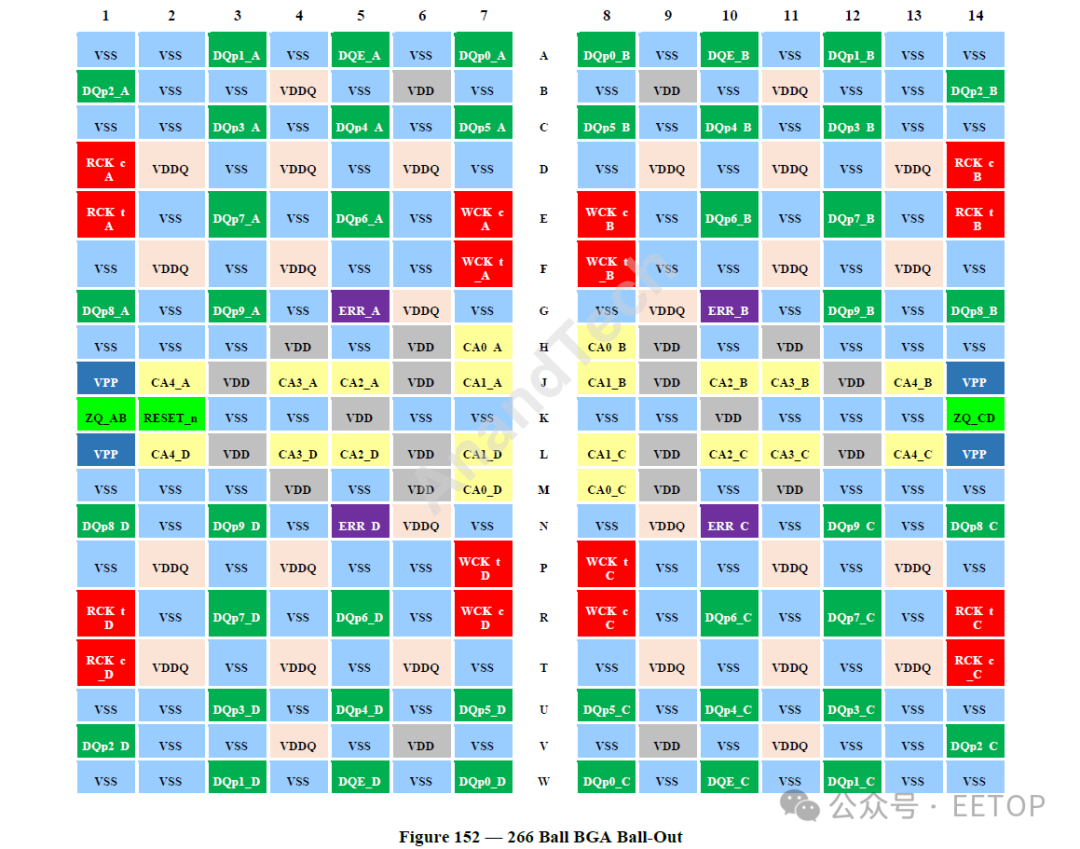

每個內(nèi)存芯片通道數(shù)量的變化也對多通道“clamshell”模式如何適用于更高容量的內(nèi)存配置有輕微影響。雖然GDDR6在clamshell配置中從每個芯片訪問單個內(nèi)存通道,但GDDR7將訪問兩個通道- JEDEC稱之為雙通道模式。具體來說,這種模式從每個芯片讀取通道A和C。它實際上與GDDR6的clamshell模式完全相同,這意味著盡管最新一代內(nèi)存仍然支持clamshell配置,但除了不斷增加的內(nèi)存芯片密度之外,沒有任何其他技巧可以用來提高內(nèi)存容量。

在這方面,GDDR7 標(biāo)準(zhǔn)正式增加了對 64Gbit DRAM 設(shè)備的支持,是 GDDR6/GDDR6X 32Gbit 最大容量的兩倍。此外,還繼續(xù)支持非雙功率容量,允許使用 24Gbit 和 48Gbit 芯片。對更大內(nèi)存芯片的支持進(jìn)一步將理論上采用 384 位內(nèi)存總線的高端顯卡的最大內(nèi)存容量推高到 192GB 內(nèi)存,在大型語言人工智能模型時代,這一發(fā)展無疑會受到數(shù)據(jù)中心運(yùn)營商的歡迎。不過,盡管如此,我們?nèi)匀唤?jīng)常看到當(dāng)今的存儲卡使用 16Gbit 內(nèi)存芯片,盡管 GDDR6 支持 32Gbit 芯片。再加上三星和美光已經(jīng)透露,它們的第一代 GDDR7 芯片也將分別以 16Gbit/24Gbit 為上限,可以肯定地說,64Gbit 芯片現(xiàn)在還很遙遠(yuǎn)。

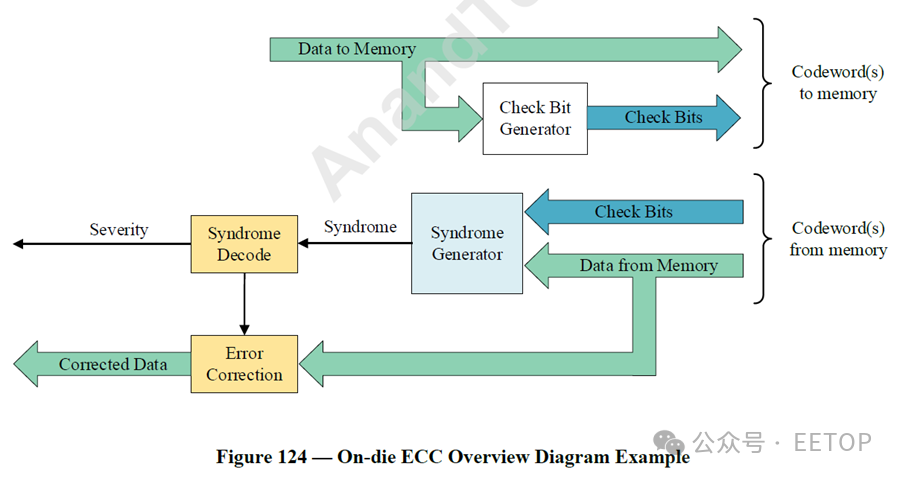

對于其最新一代的內(nèi)存技術(shù),JEDEC還包括一些新的GDDR內(nèi)存可靠性功能。最值得注意的是,片上ECC功能,類似于我們在引入DDR5時所看到的。雖然我們還沒有從JEDEC那里得到官方評論,說明為什么他們現(xiàn)在選擇包括ECC支持,但考慮到DDR5的可靠性要求,它的包含并不奇怪。簡而言之,隨著存儲芯片密度的增加,越來越難以生產(chǎn)出沒有缺陷的“完美”芯片;因此,添加片上ECC使內(nèi)存制造商能夠在面對不可避免的錯誤時保持其芯片的可靠運(yùn)行。

在內(nèi)部,GDDR7 規(guī)范要求每 256 位用戶數(shù)據(jù)至少 16 位奇偶校驗數(shù)據(jù) (6.25%),JEDEC 給出了 9 位單糾錯碼 (SEC) 和 7 位循環(huán)冗余校驗 (CRC) 的示例實現(xiàn)。總體而言,GDDR7 片上 ECC 應(yīng)該能夠糾正 100% 的 1 位錯誤,并檢測 100% 的 2 位錯誤——在極少數(shù) 3 位錯誤的情況下,檢測率降至 99.3%。有關(guān)內(nèi)存錯誤的信息也通過JEDEC所說的片上ECC透明協(xié)議提供給內(nèi)存控制器。雖然在技術(shù)上與ECC本身是分開的,但GDDR7還引入了另一個內(nèi)存可靠性功能,即命令地址與命令阻塞(CAPARBLK)的奇偶校驗,旨在提高命令地址總線的完整性。

此外,雖然加入片上 ECC 對消費(fèi)類顯卡的影響不會超過對 DDR5 內(nèi)存和消費(fèi)類平臺的影響,但這對工作站和服務(wù)器顯卡意味著什么還有待觀察。工作站和服務(wù)器顯卡供應(yīng)商在無保護(hù)內(nèi)存上使用軟 ECC 已經(jīng)有好幾代了;GDDR7 顯卡大概也會如此,但與 CPU 領(lǐng)域相比,軟 ECC 的常規(guī)使用會讓事情變得更加靈活。

最后,GDDR7 還引入了一系列其他與可靠性相關(guān)的功能,主要與幫助 PAM3 運(yùn)行有關(guān)。這包括具有眼圖掩蔽和錯誤計數(shù)器的核心獨(dú)立 LFSR(線性反饋移位寄存器)訓(xùn)練模式。LFSR 訓(xùn)練模式用于測試和調(diào)整接口(以確保效率),眼圖掩蔽評估信號質(zhì)量,錯誤計數(shù)器跟蹤訓(xùn)練期間的錯誤數(shù)量。

撇開技術(shù)問題不談,此次發(fā)布公告包括了來自多方所有常規(guī)參與者的支持聲明,其中包括 AMD 和 NVIDA,以及美光/三星/SKhynix 三巨頭。不言而喻,鑒于 GDDR7 將帶來的內(nèi)存容量和帶寬提升,各方都熱衷于使用或銷售 GDDR7--尤其是在這個任何針對 AI 市場的產(chǎn)品都熱銷的時代。

目前尚未公布具體產(chǎn)品,但由于三星和美光此前已宣布打算在今年推出 GDDR7 內(nèi)存,因此我們應(yīng)該會在今年晚些時候看到新的內(nèi)存,以及與其配對的新 GPU。

來源:EETOP編譯自anandtech

參考鏈接:

https://www.anandtech.com/show/21287/jedec-publishes-gddr7-specifications-pam3-ecc-higher-density

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章