里程碑!PCIe 6.0完整草案發(fā)布!已獲得測試芯片驗證

2020-11-05 14:13:05 EETOP

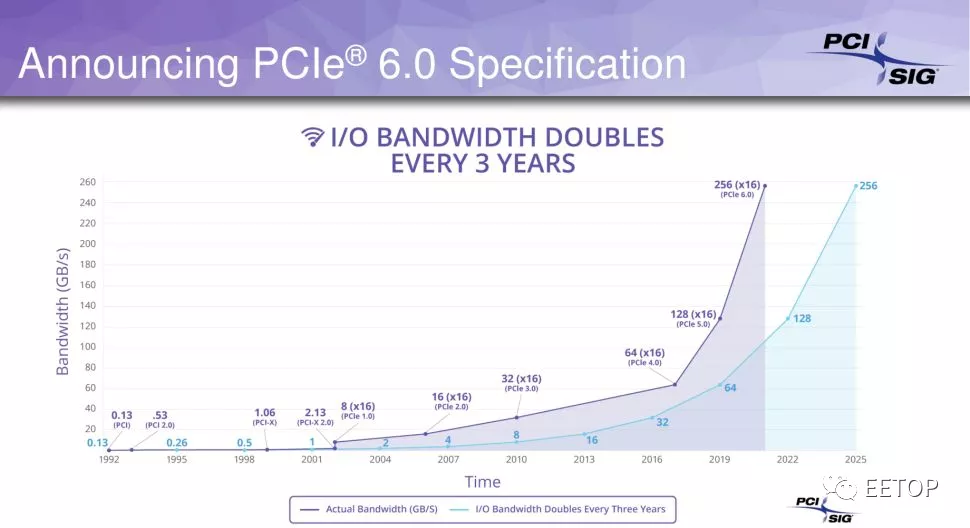

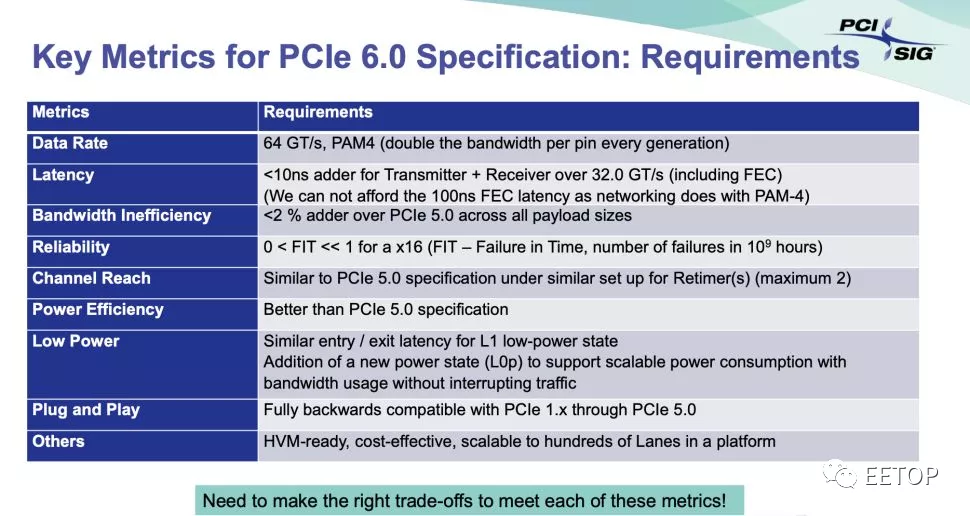

PCIe 6.0 會將數(shù)據(jù)傳輸速率提高到64 GT/s,高于PCIe 5.0的32GT/s和PCIe 4.0的16 GT/s。為了提高數(shù)據(jù)傳輸速率和帶寬,新接口采用了具有四個級別(PAM4)信號的脈沖幅度調(diào)制,該接口也用于InfiniBand和GDDR6X內(nèi)存等高端網(wǎng)絡(luò)技術(shù)。此外,PCIe 6.0使用低延遲前向糾錯(FEC)來確保高效率。 總的來說,PCIe 6.0是PCIe接口的一大進步,由于它引入了許多創(chuàng)新,為了按時將其推向市場,需要在標準開發(fā)上非常嚴謹?shù)貓?zhí)行。

PCIe 6.0規(guī)范0.7版本的發(fā)布是一個特別重要的版本,因為在這個版本發(fā)布之后,不能再增加新的功能,而且該技術(shù)的電氣規(guī)格已經(jīng)用測試芯片進行了驗證。事實上,在現(xiàn)階段,各家公司可能已經(jīng)準備好了新總線的實際實現(xiàn)方案(但不一定會公布)。

每個PCI Express規(guī)范(就像PCI-SIG設(shè)計的其他規(guī)范一樣)都有五個主要的小版本。

0.3版:概念。這個草案描述了一般的目標和將用于實現(xiàn)這些目標的方法。就PCIe 6.0而言,這些一般的東西是64 GT/s數(shù)據(jù)傳輸速率、PAM4信令和FEC。

0.5版本:第一稿。這個版本必須完全解決0.3草案中設(shè)定的目標,它還包括所有的架構(gòu)方面和要求。此外,它還包含了來自各相關(guān)方的反饋意見,此時PCI-SIG的成員可以將功能添加到正在制定的規(guī)范中。

0.7版本:完整草案。這個版本必須有一套完整的功能需求和方法定義,因為在這個版本之后不能再增加新的功能。此外,電氣規(guī)范必須已經(jīng)使用測試芯片進行了驗證。在這一點上,PCI-SIG成員可以提出新接口的不同實現(xiàn)。

0.9版本:最終草案。此時,PCI-SIG成員正在對技術(shù)進行內(nèi)部審查,以確保其知識產(chǎn)權(quán)和專利。同時,不允許進行功能上的修改。

版本1.0:最終版本。從這個版本開始,所有的更改和增強都必須通過勘誤文檔和和工程更改通知(ECN)。

PCI-SIG在大約八個月前的二月下旬發(fā)布了PCIe 6.0規(guī)范的0.5版。如果一切按計劃進行,那么新技術(shù)將在2021年下半年完成。不過不要指望新接口會很快上市。PCI-SIG 于2019年5月下旬發(fā)布了PCIe 5.0的最終版本,但是AMD和Intel等公司將支持該技術(shù)的首批平臺將在2021年下半年問世。也就是說,如果PCI-SIG在2021年下半年最終確定PCIe 6.0技術(shù)(推測),預(yù)計支持的平臺將在2023年底或2024年的某個時候出現(xiàn)。

來源:EETOP編譯自tomshardware

關(guān)鍵詞: pcie6 pciexpress PAM4 InfiniBand

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章