最新超級結MOSFET技術還能否與第三帶半導體一教高下?

2021-08-14 12:15:21 TechInsightsTechInsights 的電源專家一致認為 (SiC) 和氮化鎵 (GaN) 產品具有廣泛的系統設計應用,例如:

碳化硅 (SiC) 和氮化鎵 (GaN) 產品與硅 (Si) 技術

我們最近分析了東芝最新的“DTMOS VI”超級結 (SJ) MOSFET,即采用開爾文源的 TOLL 封裝的 TK065U65Z。該器件的額定電壓為 650 V,25°C 時的電流為 38 A,東芝引述的導通電阻 (R DSON ) 為 51 mΩ。將其轉換為我們的芯片測量中的特定導通電阻 (R DSON *A),結果為 16.81mΩ.cm2。

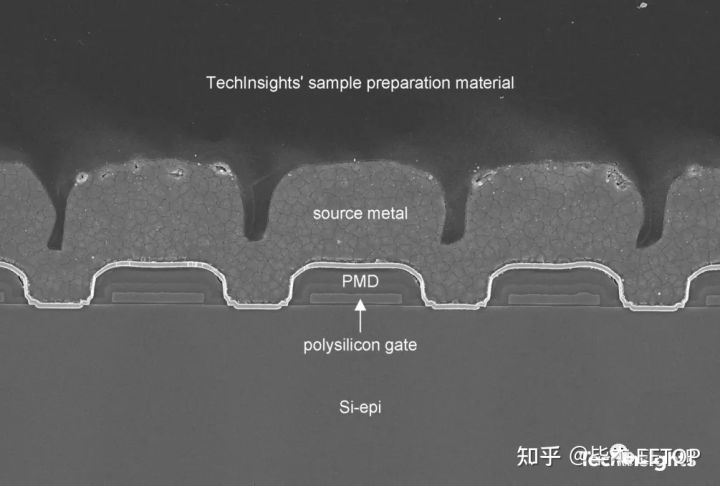

東芝 DTMOS VI' 超級結 (SJ) MOSFET、TK065U65Z 顯微圖像和規格

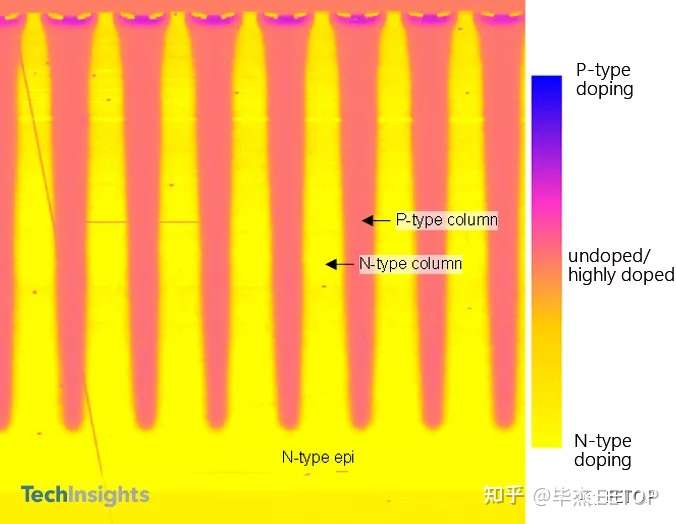

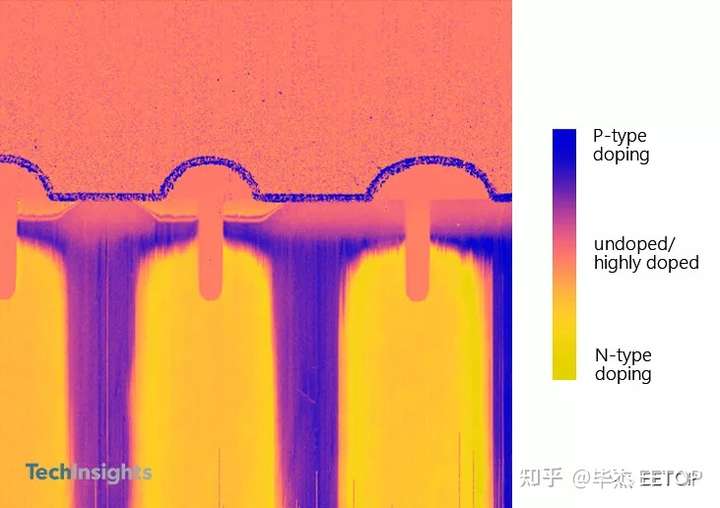

圖1顯示了器件MOSFET陣列的橫截面,這看起來像一個標準的垂直MOSFET設計。只有在觀察顯示相對摻雜物濃度的圖2時,才能觀察到SJ結構。

與 DTMOS IV 的比較

2013 年,我們也在 PowerEssentials 報告中分析了來自 DTMOS IV 代的東芝 TK31J60W 600 V、31 A、25°C SJ-MOSFET。我們對該器件的裸片測量得出的 R DSON *A 為 18.54 mΩ.cm2,比新器件高約 10%。

盡管結構上大體相似,但代際之間最明顯的兩個差異是:

圖3 顯示了DTMOS IV器件的柵極通過p型孔突出到N型漂移區,通道是沿著p型孔的界面垂直形成的溝槽。

在DTMOS VI的情況下,柵極位于Si芯片的頂部,與P型柱的邊緣重疊,沿表面形成一個水平通道。

這里有幾個對比鮮明的變化。

顯然東芝已經決定平面布局更合適。DTMOS VI 確實具有較低的R DSON *A,因此在這種情況下,單元布局必須取代由溝槽設計實現的封裝密度。他們選擇這個的確切原因很難確定,但可能有幾個因素在起作用:

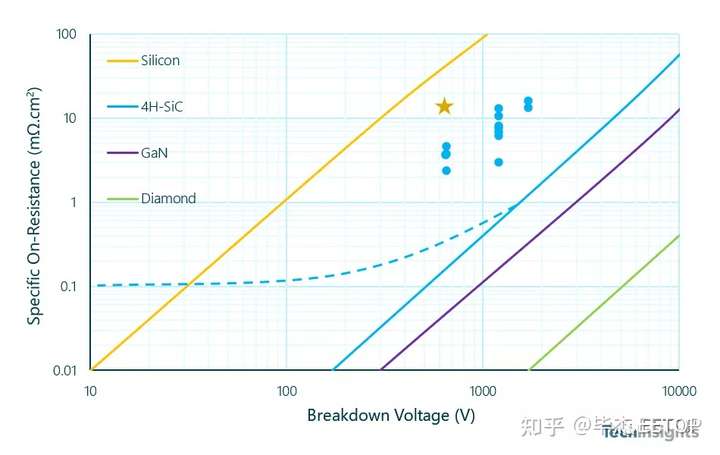

與寬禁帶(WBG)半導體的競爭力

650V級別的功率半導體器件的競爭非常激烈,而且會變得更加激烈。汽車市場的機遇意味著每一種材料和制造商都在試圖通過獨特的解決方案獲得優勢。雖然SiC和GaN很自然地處于這個電壓等級,但SJ使硅達到了這個水平。在反向偏壓下,電荷平衡柱抵消了MOSFET漂移區的電荷,允許在漂移區進行更多的摻雜,從而使R DSON值更低,更具競爭力。

那么東芝 DTMOSVI的 R DSON *A 與 WBG 的競爭對手相比如何呢?圖 4 顯示了 R DSON *A 與擊穿電壓的關系圖。黃色星形器件是 DTMOS VI,藍色圓圈代表各種額定電壓的 SiC MOSFET。

顯然在這個指標上它無法競爭,我們已經觀察到 600 V SiSJ-MOSFET 的電阻低至 14 mΩ.cm2,很難設想任何SJ-MOSFET會低于10 mΩ.cm2,這些器件的擴展正接近極限。

硅仍然可以真正保持競爭力的地方在于成本。這些器件通常在8吋甚至12吋晶圓上制造。SiC 仍然只能在 6吋襯底上進行批量生產,而且起始材料和器件制造成本都更高。因此,雖然 WBG 在性能競賽中領先,但要真正讓硅的未來受到質疑,還需要器件制造的成本等效。