英特爾10nm被超越!三星最新路線圖:5nm成為三星首個(gè)超過英特爾10nm的工藝節(jié)點(diǎn)

2019-10-20 14:50:15 EETOP7nm工藝的產(chǎn)品已經(jīng)遍地開花,Intel的10nm處理器也終于在市場登陸,不過,對于晶圓巨頭們來說,制程之戰(zhàn)卻越發(fā)膠著。

在日前一場技術(shù)交流活動(dòng)中,三星重新修訂了未來節(jié)點(diǎn)工藝的細(xì)節(jié)。

三星稱,EUV后,他們將在3nm節(jié)點(diǎn)首發(fā)GAA MCFET(多橋通道FET)工藝。由于FinFET的限制,預(yù)計(jì)在5nm節(jié)點(diǎn)之后會(huì)被取代。實(shí)際上,5nm在三星手中,也僅僅是7nm LPP的改良,可視為導(dǎo)入第二代EUV的一代。7nm LPP向后有三個(gè)迭代版本,分別是6nm LPP、5nm LPE和4nm LPE。

相較于年初的路線圖,三星6LPP只是簡單地引入SDB,從而提供了1.18倍的密度改進(jìn)。另一個(gè)改變是刪除4LPP節(jié)點(diǎn),在路線圖上只留下4LPE。最后,三星將3 GAAE和3 GAAP更名為3 GAE和3 GAP。

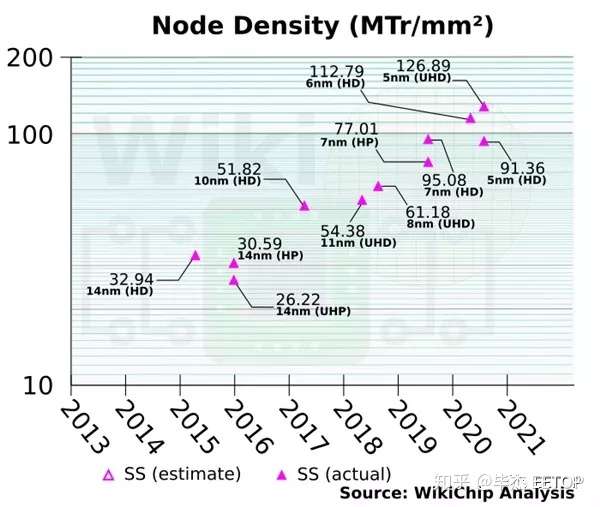

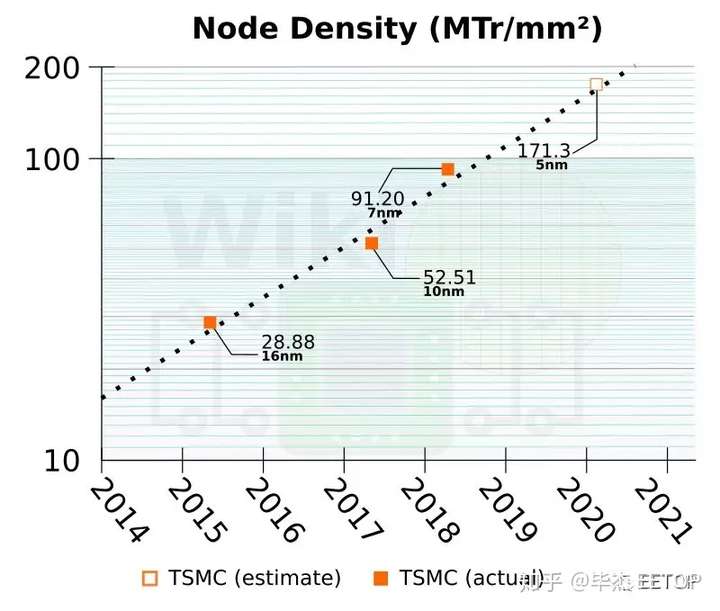

外媒wikichip分析:關(guān)于工藝核心指標(biāo),5nm LPE雖然沿用7nm LPP的晶體管和SRAM,但性能增強(qiáng)了11%,UHD下的密度會(huì)接近130MTr/mm²,相比英特爾的10納米密度為100MTr/mm²,臺積電7nm密度91MTr/mm²,終于成為三星第一個(gè)超過了Intel 10nm和臺積電7nm的工藝節(jié)點(diǎn)。不過值得一提的是,明年年初,臺積電將升級其N5節(jié)點(diǎn),該節(jié)點(diǎn)的密度比三星提供的任何產(chǎn)品都要高,密度預(yù)計(jì)為171MTr/mm²。

在4nm LPE上(2021年推出),三星可以做到137 MTr/mm²的密度,接近臺積電5nm。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章