使用基于Raspberry Pi的DDS信號發生器實現精確RF測試

2023-06-08 11:17:24 EETOP在涉及射頻(RF)的硬件測試中,選擇可配置、已校準的可靠信號源是其中最重要的方面之一。本文提供了基于Raspberry Pi的高度集成解決方案,其可用于合成RF信號發生器,輸出DC至5.5 GHz的單一頻率信號,輸出功率范圍為0 dBm至-40 dBm。所提出的系統基于直接數字頻率合成(DDS)架構,并對其輸出功率與頻率特性進行了校準,可確保在整個工作頻率范圍中,輸出功率保持在所需功率水平的±0.5 dB以內。

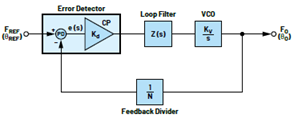

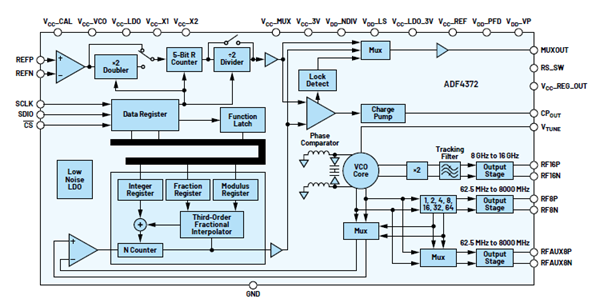

RF信號發生器,尤其是微波頻率的RF信號發生器,以前通常是基于鎖相環(PLL)頻率合成器1來構建。PLL支持從低頻參考信號生成穩定的高頻信號。圖1顯示了一個基本PLL模型。該模型由反饋系統(其中包括一個包括一個電壓控制振蕩器(VCO)用于改變輸出頻率)、誤差檢測器(用于比較輸入參考頻率和輸出頻率)以及分頻器組成。當分頻器的輸出頻率和相位等于輸入參考的頻率和相位時,環路被認為處于鎖定狀態。2–5

圖1.基本PLL模型

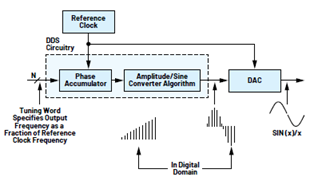

根據應用的不同,DDS架構作為頻率合成器可能比PLL提供了一種更好的替代方案。。圖2顯示了一個典型的基于DDS的信號發生器。調諧字應用于相位累加器,由后者確定輸出斜坡的斜率。累加器的高位經過幅度正弦轉換器,最終到達DAC。與PLL相比,DDS的架構具有明顯的優勢。例如,DDS數字相位累加器可實現比基于PLL的頻率合成器更精細的輸出頻率調諧分辨率。

圖2.基于DDS的典型信號發生器

PLL切換時間是其反饋環路建立時間和VCO響應時間的函數,由于自身性質的限制,其速度較慢,而DDS僅受數字處理延遲的限制,因此具有更快的切換速度。在電路板尺寸方面,DDS的面積更小,便于系統設計,許多硬件RF設計難題也迎刃而解6。

下一部分將討論CN0511。一款基于DDS架構的完整DC至5.5 GHz正弦波信號發生器的總體系統設計。接下來將討論矢量信號發生器架構及其規格。而后將重點討論系統時鐘,包括時鐘參考要求以及時鐘管理單元和矢量信號發生器之間的電路連接。也會涉及電源架構和系統布局,并進一步說明整體系統如何實現高功率效率和合理的散熱性能。隨后的“軟件架構和校準”部分將圍繞系統軟件控制和校準展開討論。該部分將解釋軟件提供的靈活控制以及如何校準輸出功率。最后一部分將說明整體系統性能,包括系統相位噪聲、校準輸出功率和系統的熱性能。

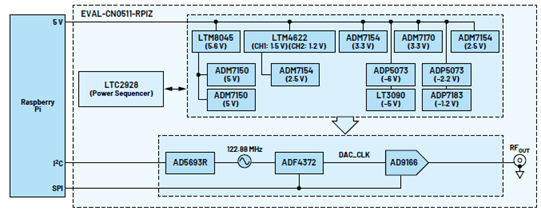

圖3所示系統是基于DDS架構的完整DC至5.5 GHz正弦波信號發生器。四開關DAC核心和集成輸出放大器在整個工作頻率范圍內提供極低的失真,并配有50Ω的輸出匹配終端。

板載時鐘解決方案包括參考振蕩器和PLL,因而無需外部時鐘源。所有電源均來自Raspberry Pi平臺板,其具有超高電源抑制比(PSRR)穩壓器和無源濾波功能,可使大幅減小電源轉換器對RF性能的影響。

圖3.CN0511:基于RPI的頻率合成RF信號發生器

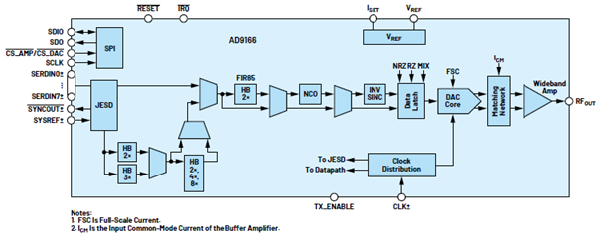

圖4.所用矢量信號發生器(AD9166)的功能框圖

圖5.ADF4372 RF8x輸出級

圖3所示架構可用于雷達、自動測試、任意波形發生器和單音信號發生器等各種應用。而本文中實現了單音信號發生器應用。以下小節將討論CN0511包含的主要集成器件。

如圖4所示,所使用的DC至9 GHz矢量信號發生器包含一個6 GSPS(1倍不歸零模式)DAC、8通道、12.5 Gbps JESD204B數據接口以及一個具有多個數控振蕩器(NCO)的DDS。同時該器件是高度可配置的數字數據路徑,包括插值濾波器、反SINC補償和數字混頻器,支持靈活的頻譜規劃。

圖4所示系統利用DAC的48位可編程模數NCO以非常高的精度(43 μHz頻率分辨率)實現了信號的數字頻移。該DAC的NCO僅需要SPI寫入接口速度達到100 MHz即可快速更新頻率調諧字(FTW)。SPI還支持配置和監控該DAC中的各種功能模塊。本設計未使用JESD通道,器件僅在NCO模式下使用。

圖4中的矢量信號發生器集成了單端、50 Ω匹配的輸出RF放大器,因此無需采用復雜的RF輸出電路接口。表1顯示了AD9166的主要規格和在各種條件下的性能。

表1.AD9166主要規格

參數 | 值 | 條件 |

頻帶平坦度 | DC至9 GHz | |

SFDR | –83 dBc | 51 MHz信號音 |

-66 dBc | 451 MHz信號音 | |

-38 dBc | 4051 MHz信號音 | |

功耗 | ~4 W | 5000 MHz信號音 |

相位噪聲 | -134.8 dBc/Hz | 3600 MHz信號音;10 kHz偏移 |

封裝 | 324引腳BGA (15 mm × 15 mm) |

圖2中的系統使用了ADF4372 PLL(見圖5),這是一款集成VCO的寬帶頻率合成器,當與外部環路濾波器和外部參考頻率一起使用時,可以作為小數N分頻或整數N分頻頻率合成器。此外,VCO頻率可進行1、2、4、8、16、32或64分頻,因此用戶可以在RF8x產生低至62.5 MHz的RF輸出頻率。

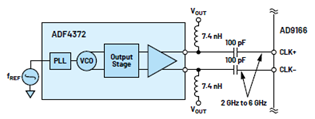

時鐘源的質量(例如其相位噪聲和雜散特性)以及其與高速DAC時鐘輸入的接口,會直接影響交流性能。因此,相位噪聲和其他頻譜內容將會被直接調制到輸出信號上。為實現最佳整數邊界雜散和相位噪聲性能,ADF4372使用了單端參考輸入信號,然后將其倍頻以產生用于高速DAC的時鐘,如圖6所示。

圖6.ADF4372和AD9166之間的電路連接

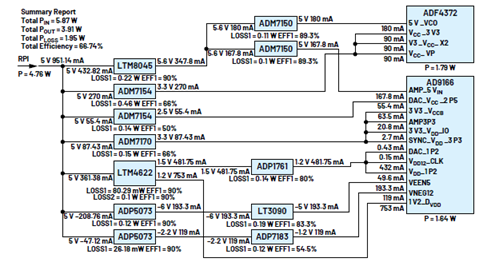

CN0511的系統電源樹如圖7所示,基于系統負載要求將其效率提高到90%,分別使用了LTM8045、LTM4622和ADP5073開關穩壓器,。并選用ADM7150、ADM7154和ADP1761等低壓差線性穩壓器(LDO)來為DAC、放大器、PLL和VCO供電,其有超低噪聲和高PSRR性能,可實現最佳相位噪聲性能。

使用電源時序控制器LTC2928來確保高速DAC按正確順序上電,避免損壞其內部電路。該電源時序控制器IC可監測和管理四個電壓軌,并具有控制各電壓軌的上電時間和其他監控功能,其中包括欠壓和過壓監控與報告功能。

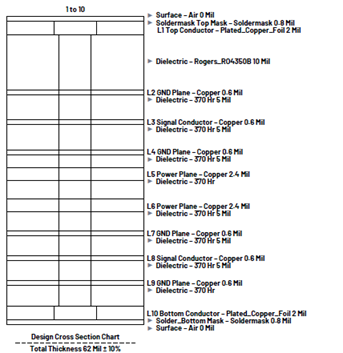

對于這種需要極高性能和較高輸出頻率的應用,PCB(印刷電路板)材料的選擇會對結果有很大影響。圖8顯示了推薦的CN0511 PCB疊層,它在包含RF走線的層上使用Rogers 4350電介質材料,最大程度上減少3GHz以上的信號衰減,并確保在RF輸出處獲得最佳的信號完整性。

圖8.推薦的PCB橫截面和疊層

熱性能與PCB設計和工作環境直接相關。為改善設計的散熱性能,在PCB散熱焊盤上打了散熱通孔。

圖7.系統電源樹

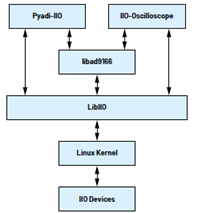

在任何涉及信號發生器的應用都希望能夠輕松靈活地控制儀器設備。因為它只需要將一張帶有Kuiper Linux鏡像的SD卡插入Raspberry Pi,因而可以認為CN0511是即插即用的。Kuiper Linux鏡像包含控制信號發生器所需的所有必要軟件。有兩種方法可改變輸出功率和頻率:使用PyADI-IIO模塊寫入代碼,或使用IIO-Oscilloscope圖形用戶界面(GUI)輸入所需的輸出。

PyADI-IIO是ADI硬件的Python抽象模塊,帶有工業輸入/輸出(IIO)驅動程序。此模塊為控制硬件提供了簡單易用的Python方法和屬性。通過非常簡單的Python代碼行即可控制該板,這些代碼可以在本地或遠程運行。可以使用簡單的for循環和一些延遲來創建任何頻率掃描,用于測試其他設備。

IIO-Oscilloscope是一個跨平臺GUI應用程序,需要用戶輸入輸出功率幅度和頻率作為參數。

PyADI-IIO和IIO-Oscilloscope這兩個模塊均提供了結溫傳感器的輸出:一個在PLL IC內,另一個在矢量信號發生器IC內。圖9展示了這兩個軟件模塊以及與CN0511板通信所需的其他組件(libAD9166、LibIIO和Linux內核)。圖9中顯示的libAD9166是在Kuiper鏡像上預裝的另一個庫,用于準確控制輸出功率,包含輸出校準功率所需的C++代碼,并特定使用于該板。關于如何實現校準的理論將在B節:輸出功率校準中繼續討論。

圖9.通過PyADI-IIO和IIO-Oscilloscope與設備通信所需的軟件組件框圖

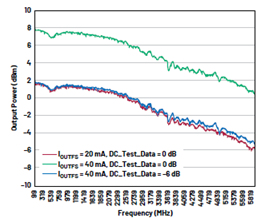

在信號發生器應用中,頻帶平坦度是一個關鍵參數。在該系統中,輸出功率與頻率的關系特性主要由矢量信號發生器的輸出決定。隨著頻率提高,輸出阻抗從其直流值開始減小。輸出阻抗的這種變化以及負載處的任何阻抗失配都會直接影響輸出功率。此外,可預測的sinc滾降也會影響輸出功率的頻率響應。圖10討論并顯示了測得的未校準輸出功率與頻率的關系。為了克服這些不利因素,我們對輸出功率與頻率的關系進行了軟件校準。

用于校正輸出功率的旋鈕包含了AD9166的兩個寄存器:設置滿量程電流的10位寄存器Ioutfs_reg(地址0x42和0x41)和設置滿量程電流的16位寄存器Iout_reg(地址0x14E和0x14F)。這兩個寄存器負責控制AD9166 DAC的輸出電流,這也是AD9166放大器的輸入(圖3)。

Ioutfs_reg提供大約10 dBm的輸出功率動態范圍,這是用于調整圖10所示不必要特性的理想值。

圖10.輸出功率與頻率的關系:未校準的輸出功率

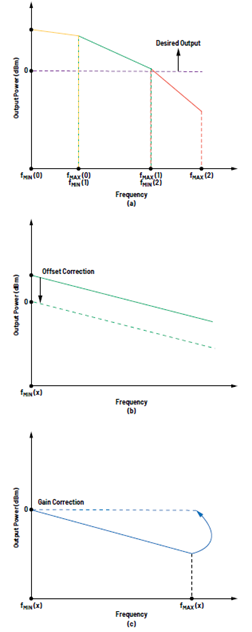

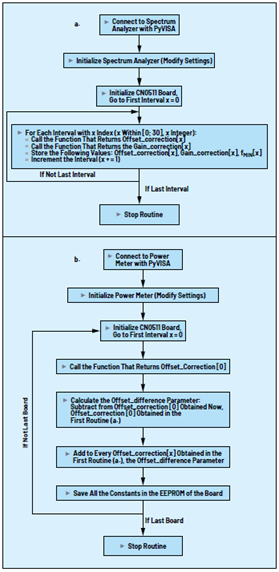

從測量結果來看,每個PCB樣片都顯示出圖10所示的相同形狀特性,只是偏移存在差異。考慮到這一點,我們開發了兩個校準例程。第一個校準程序只需執行一次,用于獲取校準整個形狀所需的參數,使其平坦化,;第二個程序則用于校正不同板之間的偏移誤差,并作為每片板的生產測試運行。兩個校準例程均通過輸出測量、計算和基于計算的寄存器調整來完成。

第一個校準例程的主要設計思路如圖11所示。首先,圖10中的整個特性曲線被分成多個頻率區間,這些區間可以用從fmin[x]到fmax[x]的線段來近似表示,其中x是區間的索引,x ∈ [0, 31],并且x為正整數。實際設計選擇了31個區間,但為了更好地舉例說明,圖11a中只顯示了三個區間。對于每個區間,需要獲得兩個常數:一個是用于偏移校正的Offset_correction(圖11b);一個是用于增益校正的Gain_correction(圖11c)。還需要存儲參數fmin[x]以跟蹤區間。

圖11.校準例程的可視化舉例:(a) 將特性曲線分成多個部分;(b) 對每個部分進行偏移校正;(c) 對每個部分進行斜率校正。

圖12a為第一個校準例程的工作原理偽代碼流程圖。為完成此算法,需要使用非常精確的頻譜分析儀來測量輸出功率(使用Keysight E5052B/R&S FSUP)。第一個例程(圖12a)產生的參數用于第二個校準例程,如圖12b所示。

圖12.偽代碼流程圖:(a) 只運行一次的第一個校準例程;(b) 在每個CN0511板上運行的第二個校準例程。

第二個校準例程(圖12b)是針對生產測試中每個PCB樣片運行的,并為每個區間的Offset_correction參數增加同一常數。在第二個例程結束時,對于每個區間,修改的參數Offset_correction[x]、Gain_correction[x] 和fmin[x]都將存儲在電路板的EEPROM中。當電路板工作時,這些參數將在軟件中進一步使用。

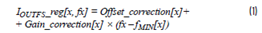

為設置校準輸出功率,軟件使用公式1來計算調整頻率fx處的輸出功率的Ioutfs_reg寄存器值,以。fx是區間x內的頻率:fx ∈ [Fmin[x], fmax[x]),fx為實正數,fmin[x]是索引為x的區間的最小頻率。

如公式1所示,電路板上必須為每個x區間存儲三個參數,以便進行輸出校正:即Offset_correction[x]、Gain_correction[x]和fmin[x]。

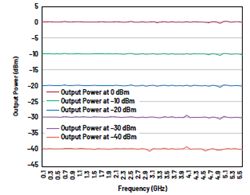

圖13顯示了CN0511在幾種不同輸出功率水平下的寬帶補償頻帶平坦度。對于設置在0 dBm和-40 dBm之間的任何輸出功率,從DC到5.5 GHz的整個頻帶內的精度為±0.5 dBm。

圖13.校準輸出功率與頻率的關系

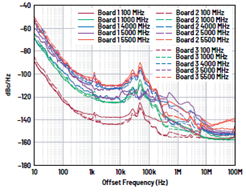

時鐘源的質量以及其與AD9166時鐘輸入端的接口會直接影響相位噪聲性能。在指定頻率偏移處的相位噪聲和雜散會被直接轉為輸出信號。圖14顯示了經過測量的單邊帶(SSB)相位噪聲與頻率偏移的關系。所有數據都是在輸出功率設置為滿量程的情況下收集的。使用板載122.88 MHz CMOS壓控晶體振蕩器用作系統時鐘參考。

圖14.系統相位噪聲性能

根據應用和配置,高速DAC的功耗可能接近4 W。該器件使用裸露芯片封裝來降低熱阻并允許芯片直接散熱。使用帶風扇的機械散熱器來散發封裝的熱量。在安裝散熱器的情況下,LTM4622在25°C的環境溫度下顯示出的最高溫度讀數約為60.6°C。

本文提出了一種高頻、低失真、低噪聲的信號源。所介紹的系統是一種采用基于高速DAC的DDS架構的低成本RF信號頻率合成器解決方案,通過使用基于DDS技術的矢量信號發生器,該系統較之簡單PLL的有多項優勢,例如簡單化、低失真、高分辨率調諧、近乎瞬時的跳頻、相位和幅度調制。

DDS架構的多項優勢使得調整和校準輸出功率以及微調輸出頻率成為可能。在系統中添加校準例程可為用戶提供從DC到5.5 GHz的輸出參考信號音,精度為±0.5 dBm,動態范圍為0 dBm到-40 dBm。對于實驗室儀器而言,這是一種近乎理想的解決方案。