臺(tái)積電啟動(dòng) 2納米 MPW 服務(wù)!

2024-08-29 15:39:40 EETOP臺(tái)積電計(jì)劃于9月推出新一輪CyberShuttle原型制造服務(wù)。據(jù)中國臺(tái)灣《工商時(shí)報(bào)》報(bào)道,按照慣例,客戶每年有兩次提交項(xiàng)目的機(jī)會(huì),分別在3月和9月。據(jù)報(bào)道,本次服務(wù)的亮點(diǎn)將是2納米工藝,為領(lǐng)先企業(yè)提供了搶占先機(jī)的機(jī)會(huì)。

臺(tái)積電的2納米技術(shù)進(jìn)展順利,新竹寶山新廠預(yù)計(jì)將于明年實(shí)現(xiàn)量產(chǎn)。此前有傳言稱,蘋果正考慮在2025年采用2納米芯片,iPhone 17系列有望成為首批使用這些芯片的設(shè)備。

據(jù)報(bào)道,臺(tái)積電的N2P和A16技術(shù)都預(yù)計(jì)將在2026年下半年進(jìn)入量產(chǎn)階段,這將在能效和芯片密度方面帶來改進(jìn)。

盡管首批2納米試產(chǎn)的客戶意向尚未確定,但ASIC公司仍積極參與此次CyberShuttle服務(wù)。然而,這項(xiàng)技術(shù)可能會(huì)維持臺(tái)積電在先進(jìn)工藝方面的領(lǐng)先地位,確保其未來的技術(shù)優(yōu)勢。

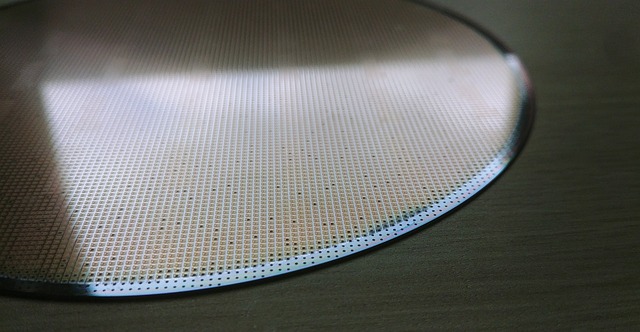

CyberShuttle(晶圓共乘)或稱MPW(多項(xiàng)目晶圓),是指將不同客戶的芯片同時(shí)放在同一片測試晶圓(Test Wafer)上,不僅可共同分擔(dān)光罩的成本,并能快速完成晶片試產(chǎn)和驗(yàn)證,強(qiáng)化客戶的成本優(yōu)勢與經(jīng)營效率。

市場初估,目前臺(tái)積電3納米制程每片晶圓約2萬美元,2納米報(bào)價(jià)大概2.4萬~2.5萬美元,是中小型IC設(shè)計(jì)業(yè)重沉重的負(fù)擔(dān)。

ASIC(特定應(yīng)用集成電路)相關(guān)業(yè)者透露,隨著技術(shù)發(fā)展,納米級(jí)光罩成本每一代制程價(jià)格呈指數(shù)級(jí)成長; 納米時(shí)代,創(chuàng)新和速度是成功因素的重要關(guān)鍵。使用傳統(tǒng)的ASIC流程進(jìn)行原型設(shè)計(jì),驗(yàn)證會(huì)花費(fèi)大量的時(shí)間和金錢,容錯(cuò)空間逐步被壓縮,多數(shù)晶圓代工業(yè)者,提供MPW或Cypershuttle計(jì)劃,透過多項(xiàng)目分擔(dān)光罩成本、NRE成本也能顯著降低。

臺(tái)積電指出,現(xiàn)階段的Cyper Shuttle服務(wù)涵蓋最廣泛的技術(shù)范圍(從0.5um到3nm),每個(gè)月最多能提供10個(gè)Shuttles服務(wù)。而目前5納米以下項(xiàng)目多于Fab 18進(jìn)行,涵蓋3納米FinFET。

臺(tái)積電的CyberShuttle原型制造服務(wù)還可以驗(yàn)證IP、標(biāo)準(zhǔn)單元庫和I/O的子電路功能和工藝兼容性,將原型制造成本降低高達(dá)90%。

臺(tái)積電的2納米技術(shù)預(yù)計(jì)將于9月首次亮相,為測試芯片提供機(jī)會(huì)。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章