EDA基本準(zhǔn)就緒!臺(tái)積電:2 納米芯片開(kāi)發(fā)生態(tài)系統(tǒng)即將完成!

2023-10-17 11:13:58 EETOP本文由EETOP編譯整理自anandtech

臺(tái)積電設(shè)計(jì)基礎(chǔ)設(shè)施管理主管Dan Kochpatcharin 在阿姆斯特丹舉行的OIP 2023 會(huì)議上表示:“對(duì)于 N2,我們可以提前兩年與他們合作,因?yàn)榧{米片是不同的。EDA工具必須提前準(zhǔn)備就緒。我們擁有一支龐大的工程團(tuán)隊(duì)來(lái)與EDA 合作伙伴、IP合作伙伴和以及其他合作伙伴合作。”

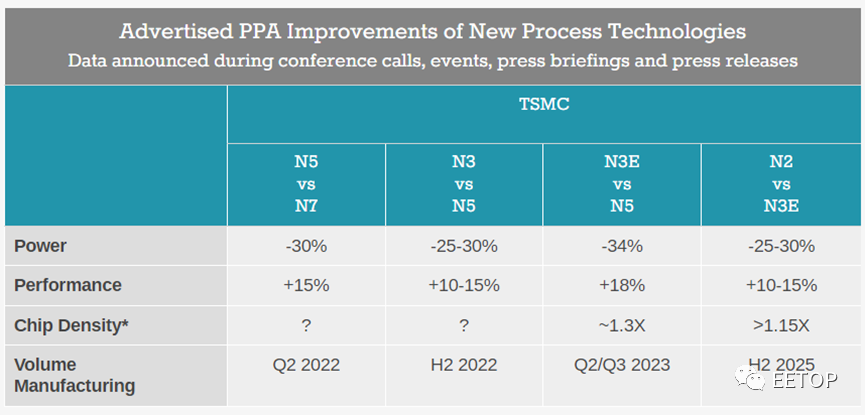

注:*臺(tái)積電公布的芯片密度反映了"混合 "芯片密度,包括 50% 邏輯、30% SRAM 和 20% 模擬。

原定于 2025 年下半年某個(gè)時(shí)間開(kāi)始生產(chǎn) N2 芯片的準(zhǔn)備工作很早就開(kāi)始了。納米片 GAA 晶體管的行為與熟悉的 FinFET 不同,因此 EDA 和其他工具和 IP 制造商必須從頭開(kāi)始構(gòu)建他們的產(chǎn)品。這就是臺(tái)積電開(kāi)放創(chuàng)新平臺(tái)(OIP)展示其實(shí)力的地方,使臺(tái)積電的合作伙伴能夠提前開(kāi)始開(kāi)發(fā)他們的產(chǎn)品。

目前,Cadence、Synopsys的主要EDA工具以及Ansys、西門(mén)子的很多EDA工具都已經(jīng)通過(guò)了臺(tái)積電的認(rèn)證,芯片開(kāi)發(fā)商已經(jīng)可以使用它們來(lái)設(shè)計(jì)芯片。此外,Cadence和 Synopsys的 EDA 軟件已準(zhǔn)備好進(jìn)行模擬設(shè)計(jì)遷移。此外,Cadence的 EDA 工具已經(jīng)支持 N2P 的背面供電網(wǎng)絡(luò)。

對(duì)于預(yù)構(gòu)建的 IP 設(shè)計(jì),會(huì)花費(fèi)更長(zhǎng)的時(shí)間。TSMC 的基礎(chǔ)庫(kù)和 IP,包括標(biāo)準(zhǔn)單元、GPIO/ESD、PLL、SRAM 和 ROM,已準(zhǔn)備好用于移動(dòng)和高性能計(jì)算應(yīng)用。同時(shí),一些PLL 存在于硅前開(kāi)發(fā)套件中,而其他PLL 則經(jīng)過(guò)硅驗(yàn)證。最后,根據(jù)臺(tái)積電的PPT,非易失性存儲(chǔ)器、接口 IP 甚至芯片組 IP 等區(qū)塊尚未面世,這也是某些芯片設(shè)計(jì)的瓶頸所在,但Alphawave、Cadence、Credo、eMemory、GUC 和 Synopsys等公司正在積極開(kāi)發(fā)或計(jì)劃開(kāi)發(fā)這些區(qū)塊。最終,用于設(shè)計(jì)2 納米芯片的工具和庫(kù)生態(tài)系統(tǒng)正在逐步完善,但還不是全部。

Kochpatcharin說(shuō):“開(kāi)發(fā)以納米片晶體管的IP并不難,但它確實(shí)需要更多的周期時(shí)間。其中一些IP供應(yīng)商也需要接受培訓(xùn),因?yàn)檫@是不同的。從平面晶體管到FinFET,并不難,你只需要知道如何做FinFET。這是一樣的,你只需要知道如何去做。所以,訓(xùn)練確實(shí)需要一些時(shí)間,但當(dāng)你接受訓(xùn)練時(shí),這很容易。這就是為什么我們開(kāi)始得很早。”

雖然芯片的許多主要構(gòu)件都已具備 N2-就緒條件,但在臺(tái)積電 2 納米級(jí)工藝技術(shù)投入量產(chǎn)之前,許多公司仍有許多工作要做。傾向于自行設(shè)計(jì)(或聯(lián)合設(shè)計(jì))IP 和開(kāi)發(fā)工具的大公司已經(jīng)在開(kāi)發(fā) 2 納米芯片,到 2025 年下半年開(kāi)始量產(chǎn)時(shí),他們的產(chǎn)品應(yīng)該已經(jīng)準(zhǔn)備就緒。由于臺(tái)積電及其合作伙伴的 2納米準(zhǔn)備工作進(jìn)展順利,其他公司也可以啟動(dòng)設(shè)計(jì)引擎。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章