芯動兼容UCIe標準的最新Chiplet技術解析

2023-08-16 19:03:50 芯動科技近日,芯動科技高速接口IP三件套之明星產品--Innolink? Chiplet互連解決方案,相繼亮相第二屆中國互連技術與產業大會、智東西Chiplet公開課。芯動科技技術總監高專分享了兩場專業演講,就行業Chiplet技術熱點和芯動Innolink? Chiplet核心技術,與騰訊、阿里、中興、百度、是得科技等知名企業,以及中科院物理所、牛津大學、上海交大等學術科院領域名家交流分享,共同助推Chiplet互連技術的創新與應用。

多晶粒Chiplet技術是通過各種不同的工藝和封裝技術,讓多個模塊芯片與底層基礎芯片有機結合,形成一個大帶寬、高密度的系統芯片,突破單晶圓性能和良率瓶頸,以更具性價比的路線滿足產業界日益增長的對芯片性能的需求,是技術發展大勢所趨。芯動作為在高速接口互連技術深耕十多年的賦能者,響應客戶和市場需求,早于兩年前就推出了適用多個應用場景、在先進工藝量產驗證成功的自主Chiplet IP解決方案。該方案也是首套物理層兼容UCIe國際標準的Chiplet解決方案,跨工藝跨封裝,目前已在全球范圍內實現廣泛兼容并成功商用落地,在硅基板、MCM封裝基板、化合物基板以及PCB級等互聯場景率先產業化,發揮Chiplet多晶粒技術的成本和性能優勢,助力芯片設計企業和系統廠商實現產品成功。

Chiplet發展的技術背景和優勢前景

Chiplet(芯粒)通俗來講是對大芯片系統的拆分和重組,是系統級芯片(SoC)集成發展到后摩爾時代后,持續提高集成度和芯片算力的重要途徑。Chiplet通過分解手段,將SoC中CPU、加速器等資源解耦,甚至將同種資源也拆分為更細粒度的模塊,使得芯粒能夠在多種設計中重用。在芯粒生態中,用戶可以根據自己的需求,從各種供貨商提供的芯粒中挑選自己想要的芯粒,然后組合為個性化系統。因其能夠有效降低芯片開發門檻,使得芯片開發“降本增效”,業內眾多巨頭都在大力投入Chiplet技術的研發和落地。

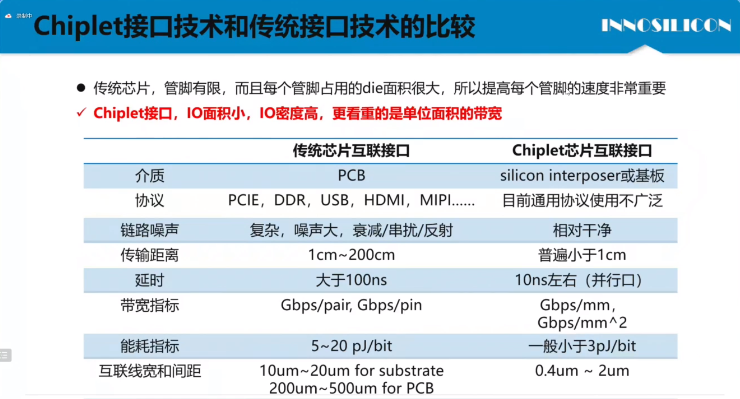

▲Chiplet接口技術和傳統接口技術比較

對CPU/GPU等芯片廠商而言,Chiplet可以縮小單die縮小尺寸、降低復雜度,實現芯片設計復雜度及設計成本的下降;在當前先進工藝場景下,Chiplet“模塊化剖分”的思路更有利于提高大型芯片良率、降低芯片制造成本,同時縮短開發周期和難度,便于部分模塊的迭代和優化,突破die size上限。對芯片系統集成商而言,不同芯片的自由組合也將帶來產品生態的開放繁榮,優勢集合,構建差異化產品。對于芯片制造商Foundry而言,Chiplet的不同工藝組合將帶來更多高端工藝客戶和die集成業務。所以說,Chiplet優勢明顯,前景一片大好。

與此同時,Chiplet互連也有諸多實現難點及痛點。Chiplet互連技術對帶寬需求更大,要求更低的延時和功耗,多應用場景還需要實現跨工藝、跨封裝互聯,同時Chiplet線寬和間距小,互聯密度極高,因此技術實現更具挑戰性。此外,無廣泛使用的統一接口標準、片間互聯導致在PCB上測試和debug困難,這些也是Chiplet應用量產亟待解決的問題。

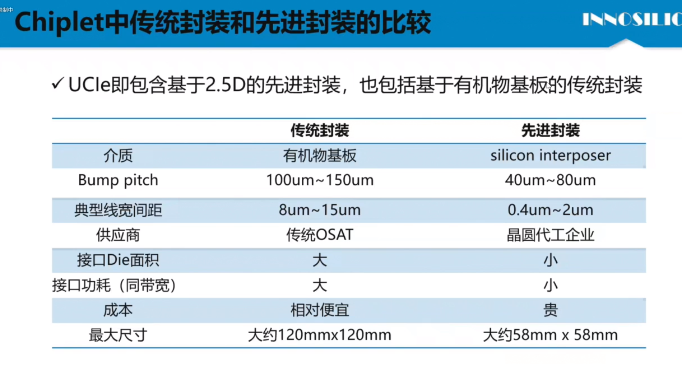

▲Chiplet中傳統封裝和先進封裝的比較

我們所說的Chiplet互聯優勢主要區別于傳統互聯技術。傳統芯片主要基于PCB介質,支持傳輸距離1~200cm,管腳有限,而且每個管腳占用的die面積很大,所以提高每個管腳的速度非常重要。Chiplet接口則可用于silicon interposer或基板,傳輸距離普遍小于1cm,對低延時要求高,IO面積小,IO密度高,更看重的是單位面積的帶寬,另外Chiplet在傳統封裝和先進封裝上的間距、功耗、die面積、帶寬、成本、尺寸需求也不一樣。

芯動UCIe Chiplet解決方案

基于前期在DDR、SerDes等高速接口技術的自主創新和先進工藝的量產驗證,集十多年IP前后端、工藝定制、封測量產全流程之經驗能力,芯動科技專門針對Chiplet互聯推出了Innolink? 互連解決方案。

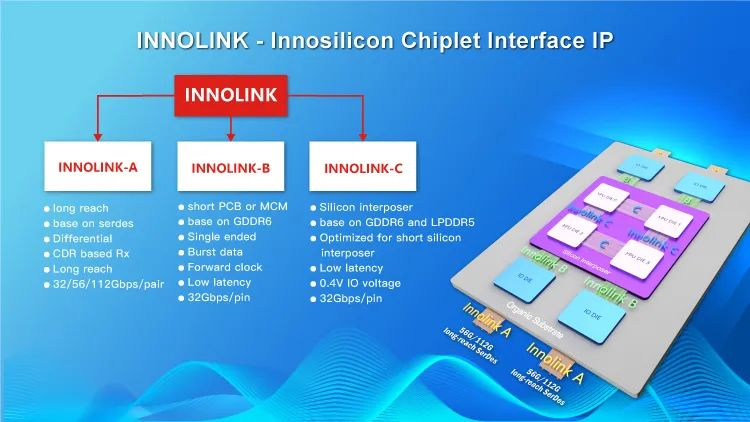

這是首個物理層兼容UCIe國際標準Chiplet超高速通訊解決方案,跨工藝、跨封裝,已完成主流先進工藝開發驗證并授權多個項目成功量產。該方案包括INNOLINK-A/B/C三種規格,支持硅基板、普通基板和PCB板3種互連模式,在Die to Die、Chip to Chip、Package to Package、Board to Board各種不同應用場景下,具備低延時、低功耗、高帶寬密度以及高性價比、高可靠性的優勢,可全棧式協助芯片設計企業和系統廠商提高SoC研發效率,降低風險,為數字時代算力需求升級提供有力支持。

▲Innolink? Chiplet A/B/C實現方法

值得一提的是,芯動兼容UCIe國際標準的Chiplet解決方案幾乎是在UCIe標準發布同一時間發布的。據高專介紹,芯動在Chiplet技術領域積累了大量的客戶應用需求經驗,幾年前就開始了Innolink? Chiplet的研發工作,率先明確InnolinkB/C基于DDR的技術路線,并于2020年的Design Reuse全球會議上首次向業界公開Innolink A/B/C技術。得益于正確的技術方向和超前的布局規劃,INNOLINK-B/C的架構和方案與UCIe基本一樣,都是針對標準封裝和先進封裝單獨定義IO接口,都是單端信號,forward clock、sideband通道、datavalid信號、burst首發、Idle低功耗等均方向一致。

具體而言,INNOLINK-A是基于SerDes的互聯技術,適用于較長的傳輸距離和較大信號衰減,可實現板卡到板卡之間的互連,支持32/56/112Gbps/pair傳輸速率。INNOLINK-B對應UCIe標準中的標準封裝,基于DDR技術單端信號,可支持短距PCB或MCM,同時兼容Die to Die和Chip to Chip,支持32Gbps/pin傳輸速率。INNOLINK-C則對應UCIe標準中的先進封裝,結合了GDDR和LPDDR的技術特點,針對Silicon Interposer做了優化,IO電壓可低至0.4V,支持32Gbps/pin傳輸速率。

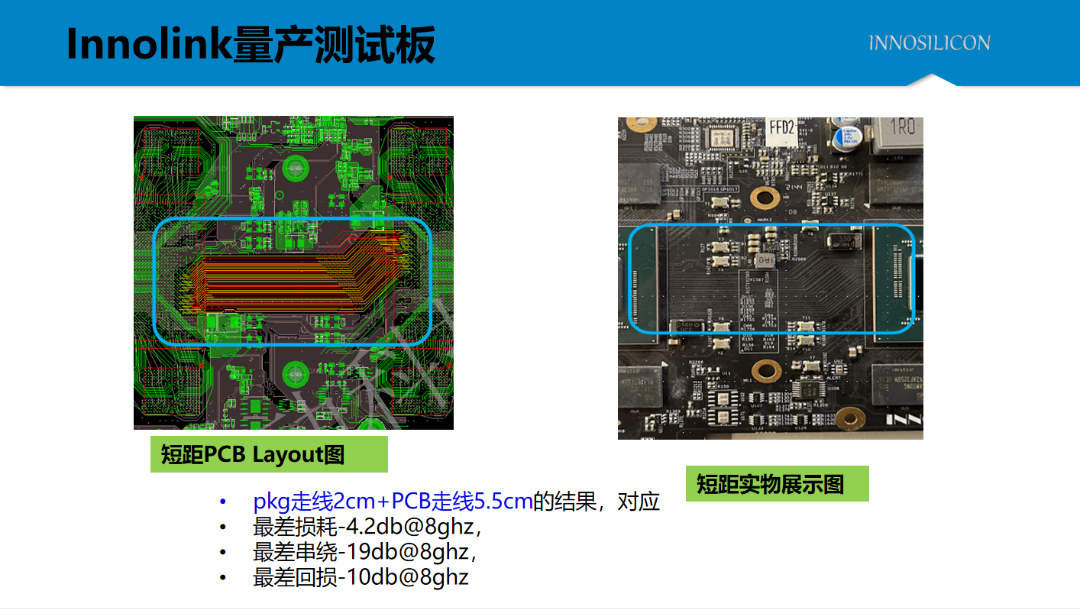

▲Innolink? Chiplet量產測試板

芯動Innolink? Chiplet可提供物理層方案,客戶自主構建協議層,也可提供PHY&Controller打包方案,這兩種方案均已授權客戶量產測試。圍繞著Innolink? Chiplet技術,芯動同時還提供封裝設計、可靠性驗證、信號完整性分析、DFT、熱仿真、測試方案等全棧式服務,使得芯片設計企業和系統廠商能夠快速便捷地實現多Die、多芯片之間的互連,有效簡化設計流程。

芯動的Chiplet也與其全系高端DDR、32/56/112G SerDes共同構成了芯動高速接口IP三件套,在全球范圍內具備核心競爭力。芯動的一站式高性能、高可靠IP具有三大優勢:支持最新的接口協議,諸如GDDR6/6X、HBM3/2e、LPDDR5X/5、UCIe Chiplet、HDMI2.1、USB4.0等,全面覆蓋通用高速接口協議;支持最先進的FinFET工藝,在各大代工廠和各級別工藝制程全面布局;先進接口IP在先進工藝上擁有大量的量產記錄和客戶群,流片驗證超過200次,為IP質量提供了可靠保證。

▲芯動高速接口IP三件套解決方案

作為全球一站式IP和芯片定制提供商,芯動一直堅持合規化、商業化、專業化運營,堅持以質量和口碑為發展生命線,深耕高速接口IP十七年,擁有專業知識和經驗豐富的開發團隊,是業界極富口碑的IP和定制服務老牌廠商。17年來,芯動服務了AMD、微軟、亞馬遜、高通、安盛美等全球數百知名企業,未來還將持續為全球客戶提供極具競爭力的全棧式解決方案,客戶至上、需求驅動,助力設計企業迅速抓住關鍵市場。