亮相DAC!芯華章發布新一代高速仿真器GalaxSim Turbo 助力千億門超大規模芯片敏捷驗證

2023-07-12 09:44:54 EETOP從填補國內空白,到自信亮相國際行業盛會,將產品發布的舞臺搬到世界頂級EDA公司和芯片、系統廠商面前。這背后折射出的不僅僅是芯華章自己的進步,也是國產EDA行業整體的前進。GalaxSim Turbo這款差異化創新產品的發布,打破了傳統邏輯仿真器的驗證容量限制,可以幫助千億門超大規模設計在RTL階段就提早進行系統級驗證,填補了傳統邏輯仿真器和硬件仿真器之間的空白。

7月12日,在一年一度的全球電子設計自動化盛會DAC 2023(Design Automation Conference)上,面向來自世界各地的頂級EDA公司和芯片、系統廠商,國內領先的系統級驗證EDA解決方案提供商芯華章,隆重推出新一代高速仿真器GalaxSim Turbo,并以指數級的數字仿真加速優勢、千億門級的超大驗證容量,收獲現場專業用戶的廣泛青睞。

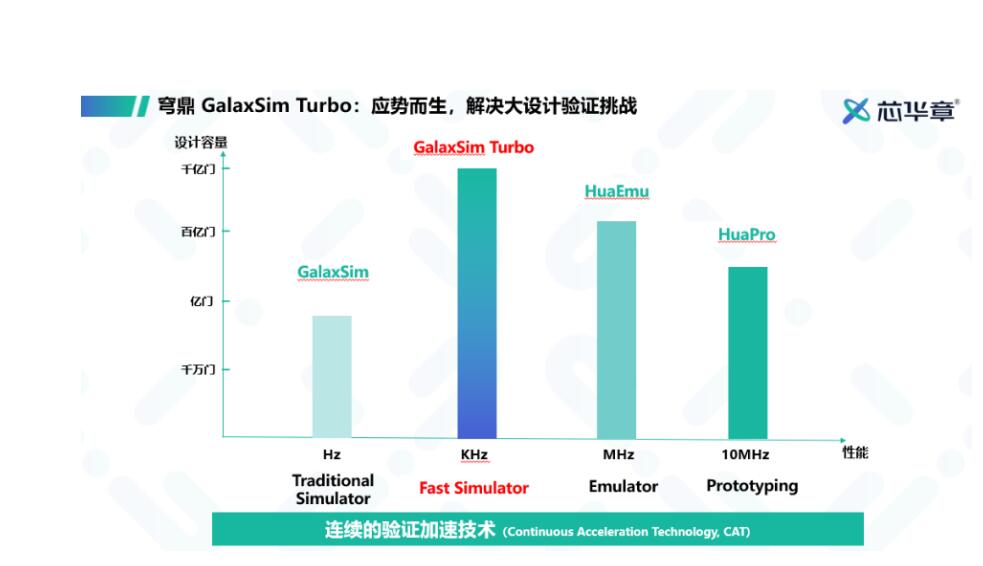

基于超大規模分布式仿真技術,GalaxSim Turbo通過打造多種仿真引擎,實現多核、多服務器并行算力,在大幅提高運行速度的同時,可以有力支持千億門級的超大規模芯片敏捷驗證與開發。這一技術的應用,對于打破傳統邏輯仿真器的驗證容量限制,在芯片設計早期引入系統級驗證,實現芯片設計和驗證的持續集成及設計(CICD)具有至關重要的作用,填補了傳統邏輯仿真器和硬件仿真器(emulator)之間的空白。

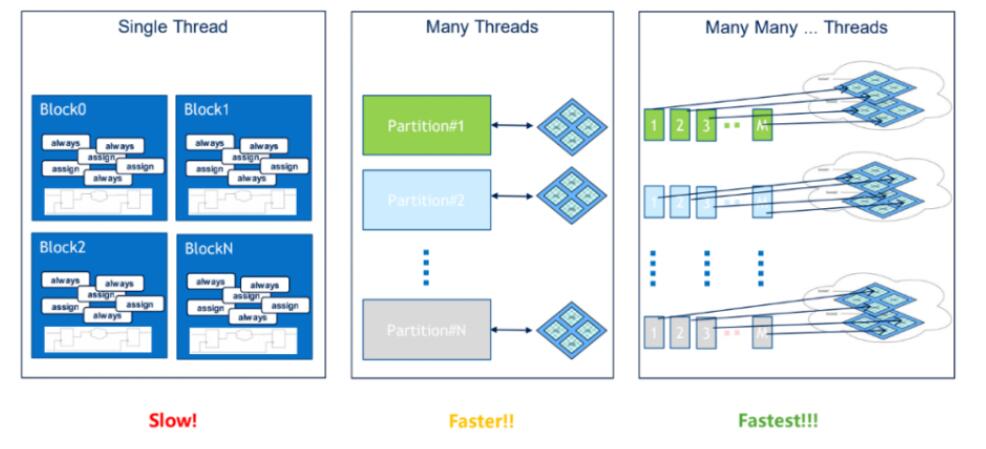

日益細分的應用場景需求、緊迫的研發創新周期、規模大而復雜的系統級芯片,都在呼喚著EDA行業帶來更多的顛覆和革新。作為芯片驗證必不可少的一個環節,仿真主要是通過計算機結合測試激勵來模擬芯片在真實環境下的運行狀況,幫助工程師來判斷運行結果是否符合預期, 并提供仿真數據以便進一步調試。傳統的邏輯仿真器產品,在很多場景下受限于事件的異步行為,設計的分割(partition)和線程同步有較大的限制,往往無法支持高速的并行仿真,從而大大限制了驗證的場景和規模。RTL驗證也成為了整個驗證流程中耗時最多,人力成本投入最大的環節。

2021年,芯華章率先發布支持國產服務器架構的數字仿真器穹鼎GalaxSim,全面支持IEEE1800 SystemVerilog語法、IEEE1364 Verilog 語法以及IEEE1800.2 UVM方法學。針對敏捷驗證需求,芯華章本次推出數字仿真器系列創新之作——GalaxSim Turbo高速仿真器(Fast Simulator),解決傳統邏輯仿真器無法滿足的超大規模系統級驗證需求。

產品亮點:

? 自帶事件級(Event-based)和周期級(Cycle-based)仿真引擎

? 支持SystemVerilog等多種設計與驗證語言,對IEEE最新UVM標準提供原生態支持

? 支持超大規模集成電路設計,最高可支持千億門

? 智能編譯分割技術、自動化分布式仿真技術,充分發揮多服務器多核并行算力

? 提供開放架構,支持與其他仿真器、原型系統和硬件加速器進行聯合仿真

? 提供靈活的交互式仿真模式以及完整的調試方案

通過自有專利支撐的邏輯分割和分布式仿真解決方案,GalaxSim Turbo融合CAT技術(Continuous Accelerating Technology),具備傳統仿真器沒有的并行計算能力,帶來更快的仿真速度,將邏輯仿真器的應用場景拓展到了系統級層面,可以幫助大規模設計在RTL階段就提早進行系統級驗證,實現高效率、高效益的迭代,從而幫助客戶大大提高驗證效率。

在大算力芯片設計的實測中,完全同等條件下,傳統仿真器進行典型測試需7天的時間,GalaxSim Turbo使用了400多個計算線程,將仿真時間縮短到2小時以內,取得相較于傳統仿真器近百倍的突破性效率提升。

智能汽車計算芯片引領者黑芝麻智能創始人兼CEO單記章表示,“為了滿足智能網聯汽車的差異化需求,新一代車規芯片的開發需要滿足大算力、高集成以及更快的迭代要求,服務整車主機廠商實現更高的性價比以及更快的產品上市需求。芯華章GalaxSim Turbo獨有的智能分割以及分布式仿真技術,幫助我們優化了驗證資源的投入,通過提前引入軟硬件協同的系統級驗證,極大地縮短了開發周期,降低了研發成本和各項安全風險,從而更快將產品推向市場。”

GalaxSim Turbo在用戶項目中的各項數據表現

芯華章科技董事長兼CEO王禮賓表示,“我們很高興能夠助力黑芝麻完成智能汽車計算芯片設計和大規模量產的突破。隨著集成電路設計規模日趨龐大,SoC級芯片驗證復雜性不斷提升,對于敏捷驗證和創新效率的要求也日益增高。基于自主知識產權的高性能數字仿真技術,芯華章致力于幫助芯片設計及系統公司不斷提高研發創新效率。未來,我們希望繼續與黑芝麻緊密合作,助力汽車智能化發展,賦能社會經濟數字化轉型高質量發展。”