臺積電與多家EDA公司合作,加快設計流程

2023-05-05 12:03:15 EETOP臺積電正在與多家知名 EDA 公司合作,包括Cadence、 Synopsys、Ansys 和 Keysight(是德科技),以加速從汽車到超大規模計算應用的芯片 設計流程。

這些合作既解決了各種應用的技術挑戰,同時也為臺積電提供了將其各種工藝技術從 3nm到 3DFabric 的功率、性能和面積 (PPA) 提升的機會。

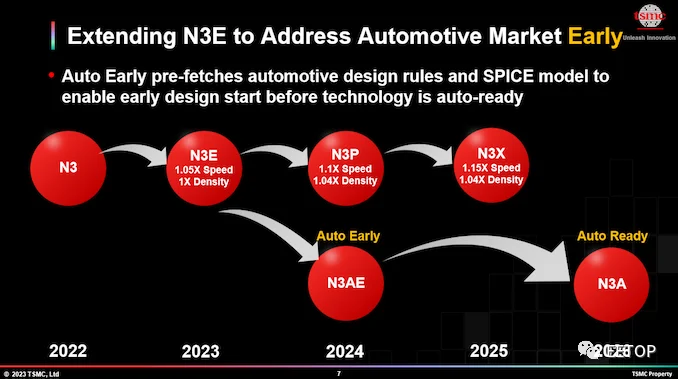

臺積電在 2023 年北美技術研討會上宣布了其瞄準汽車行業 的意向,并宣布了N4AE 和 N3AE(分別為 4 納米和 3 納米汽車工藝的早期)工藝節點,它們是臺積電 4 納米和 3 納米工藝節點的變體。

該公司希望解決汽車制造商面臨的獨特挑戰:汽車芯片的可靠性和安全性標準更高,以及由于滿足這些標準需要額外的開發時間而導致的芯片技術滯后。這意味著用于車輛的芯片可能落后于尖端技術好幾代。

N3AE 和N4AE 的工藝設計套件預計將分別于 2023 年和 2024 年推出,并且可以讓供應商有機會開發消費級芯片設計,以期在2025 年推出 N3A 和 N4A(3nm 和 4nm 汽車工藝)。臺積電希望這種循序漸進的方法將使早期參與者能夠比當前工藝快兩年完成更堅固耐用的芯片設計。

Synopsys、Ansys和 Keysight Technologies 正在與 TSMC 合作,為高級射頻 (RF) 和毫米波(mmWave) 系統創建新的設計流程。此次合作將為使用 TSMC 的 16nm FinFET 緊湊型技術 (16FFC) 的 79 GHz 集成電路提供設計參考流程。16FFC于2016年由臺積電率先投產,背后已有數年打樣。

通過降低噪聲和提高功率轉換效率,該設計過程將有利于需要高可靠性的應用,例如自治系統、5G 連接和安全系統。

Synopsys正在提供其定制的編譯器設計環境;Ansys 將貢獻其多物理場signoff 分析工具套件(VeloceRF、RaptorX、Exalto和 Totem);是德科技將使用其 Pathwave RFPro 和RFIC 設計工具進行電磁分析和電路仿真。

與此同時,Cadence 和臺積電在不止一個方面展開合作。Cadence已經使用 TSMC 的N3E 和 N2 工藝節點設計規則手冊對其數字和定制/模擬流程進行了認證。

此次合作旨在通過更高效的 IC 布局改進設計流程,例如基于網格的結構化設備布局、改進的模擬遷移、布局重用功能以及signoff-quality物理驗證的功能。特別是,相對于手動遷移,此過程可以使TSMC 工藝節點之間的設計遷移更快。它還將使移動設備、人工智能和超大規模計算應用的芯片設計人員受益。

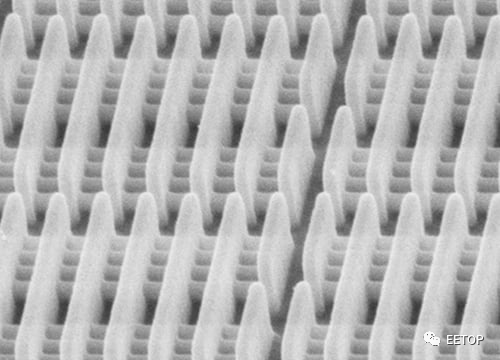

N3E是臺積電的3nm增強制程節點(二代3nm),而N2則是其2nm制程節點。基于N3E的芯片計劃在2023年下半年進入量產,而基于N2的芯片預計最快在2025年進入量產。

此外,Cadence還推出了3D-IC平臺支持 TSMC 的 3DFabric產品,例如集成扇出 (InFO)、基板上晶圓芯片 (CoWoS) 和系統級集成芯片 (TSMC-SoIC) 。這旨在加快物聯網、5G 和移動應用中使用的多芯片封裝的開發。3D-IC 提供系統規劃、封裝和系統級分析,并使用 3Dblox 1.5 規范。

來源:EETOP編譯自allaboutcircuits