模擬IC布局自動(dòng)化

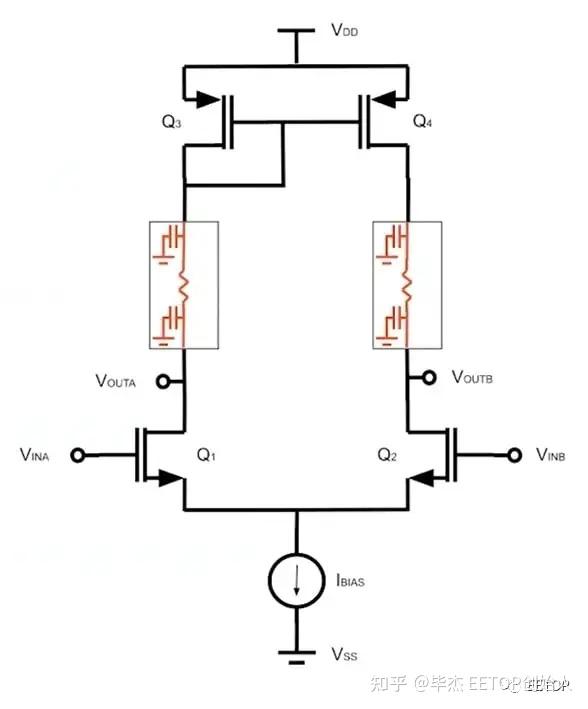

2022-03-15 12:51:42 EETOP舉例說明,對(duì)于差分對(duì)放大器,有許多特定的要求來確保魯棒的性能,例如:

差分對(duì)原理圖

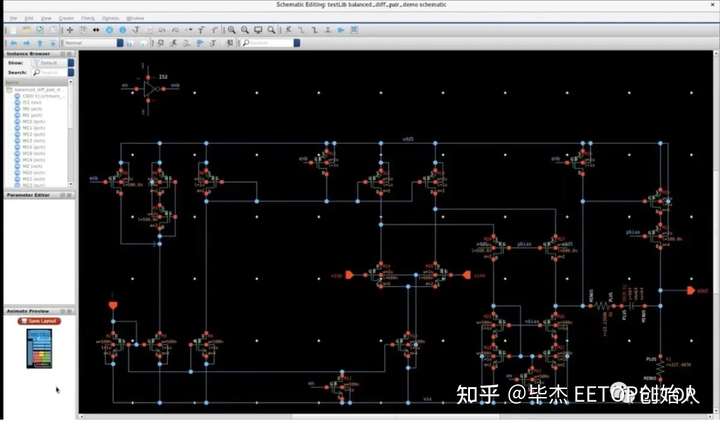

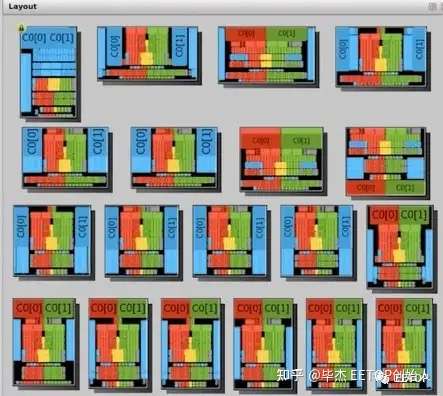

Paul 展示了 Animate Preview 插件如何在 Cadence Virtuoso 環(huán)境中工作,以及它會(huì)自動(dòng)識(shí)別當(dāng)前鏡像和差分對(duì)等原理圖結(jié)構(gòu),然后像熟練的 IC 布局設(shè)計(jì)師手動(dòng)操作一樣限制布局放置。您可以在一分鐘左右的時(shí)間內(nèi)快速看到多個(gè)布局方案,每個(gè)布局都已經(jīng)通過構(gòu)建完成了DRC clean,從而節(jié)省了更多的時(shí)間。

單擊第一個(gè)自動(dòng)生成的布局將顯示"動(dòng)畫預(yù)覽"對(duì)話框,其中顯示以下窗口:層次結(jié)構(gòu)、原理圖、布局、結(jié)果和約束。"布局"窗口顯示九個(gè)生成的布局地形。在"結(jié)果"窗口中,有針對(duì)九個(gè)布局中每個(gè)布局的分析,例如寬高比、寬度、高度和面積。"原理圖"中自動(dòng)生成的每個(gè)約束都將列在約束窗口中。

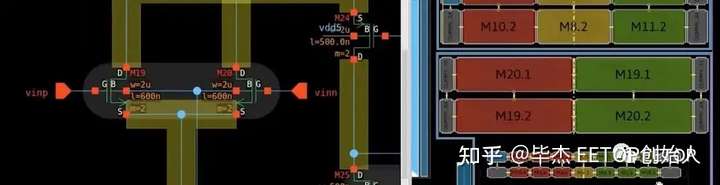

Animate 從原理圖中識(shí)別了差分對(duì),通過放大原理圖,您可以查看晶體管布局的布局選項(xiàng),例如使用的布局行數(shù)。單擊原理圖中的任何內(nèi)容都將交叉探測(cè)并在布局窗口中突出顯示該設(shè)備。

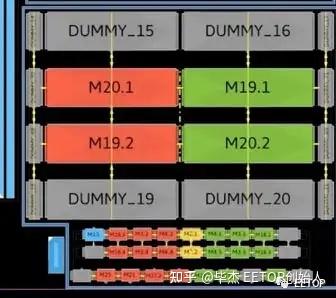

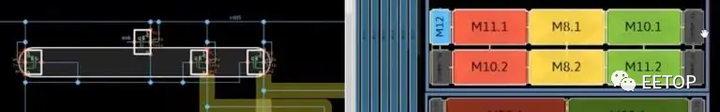

原理圖中的晶體管M19和M20定義了差分對(duì),布局顯示了這些器件如何放置在稱為公共質(zhì)心的常規(guī)行和列中,這有助于最大限度地減少工藝變化,并且在垂直和水平方向上也具有匹配的間距。多邊形頭的定義方向與匹配的一部分相同。

為了進(jìn)一步優(yōu)化此布局并改進(jìn)垂直匹配,通過選擇菜單選項(xiàng),在設(shè)備 M19 和 M20 的上方和下方添加了一個(gè)新的虛擬行:

還可以在 Animate 中查看金屬布線詳細(xì)信息,同時(shí)僅查看多邊形、金屬 1、金屬 2、金屬 3、金屬 4 和金屬 5 層,以便您可以確認(rèn)差分對(duì)中的互連是相同且平衡的。對(duì)源節(jié)點(diǎn)和漏極節(jié)點(diǎn)的路由進(jìn)行了直觀比較,并且它們是平衡的。

還顯示了四個(gè)當(dāng)前鏡設(shè)備的通用質(zhì)心布局:M8,M10,M11,M12。根據(jù)設(shè)計(jì),電流鏡和差分對(duì)之間的路由也是最小化和對(duì)稱的。檢查電流鏡和差分對(duì)之間的路由表明,金屬層確實(shí)是對(duì)稱且相同的。

差分對(duì)的輸出連接到另外兩個(gè)器件,甚至這些器件的放置和路由也是平衡的。約束選項(xiàng)已從基本模擬更改為鏡像基本模擬,以顯示如何控制左側(cè)(紅色)和右側(cè)(綠色)設(shè)備的對(duì)稱布局。蝴蝶布局選擇可以在下面看到:

總結(jié)

在過去的模擬集成電路設(shè)計(jì)中,電路設(shè)計(jì)師先畫出原理圖,然后再為布局版圖工程師添加一些注釋或注釋,然后把原理圖扔給版圖工程師。版圖工程師閱讀了注釋,做了一些位置和路線,然后把布局扔回給電路設(shè)計(jì)師。最后,電路設(shè)計(jì)者將檢查IC布局的對(duì)稱性和匹配性,并要求改進(jìn),創(chuàng)建一個(gè)循環(huán)迭代,直到滿足匹配約束。

Pulsic的新方法使電路設(shè)計(jì)師能夠在幾分鐘內(nèi)快速創(chuàng)建一個(gè)平衡和對(duì)稱的布局,而不是幾天,這完全歸功于 Animate 中固有的自動(dòng)化設(shè)計(jì)。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章