取代GAA的下一代晶體管技術--CasFET(級聯(lián)場效應晶體管)

2021-09-22 12:46:03 EETOP普渡大學電氣與計算機工程系 Katherine Ngai Pesic 和 Silvaco 研究助理教授蒂爾曼·庫比斯 (Tillman Kubis) 表示,這項研究是在晶體管小型化難度增加的情況下進行的,近年來,晶體管小型化的難度不斷增加,成本也在不斷攀升。

"晶體管需要足夠高的導通電流和足夠低的關斷電流,在這兩者之間進行切換的差異要足夠小,"Kubis說。"這些挑戰(zhàn)在過去八年左右大大減緩了晶體管的縮小速度,使得推出更強大的幾代CPU越來越困難。" 這種困難的一個比較明顯的案例是英特爾向10納米和7納米工藝的過渡,其中出現(xiàn)了一些延遲,這有助于AMD在CPU領域 "毫不客氣地 "重新崛起。

三星正在其 3nm 工藝中采用 GAAFET(Gate All Around Field EffectTransistor)技術,預計今年將實現(xiàn)量產(chǎn)。該技術是FinFet的后繼者,它重新設計了晶體管,使其在通道的四個側面都有柵極。這提供了與其相鄰單元更好的晶體管絕緣,限制了電壓泄漏,并允許在相同的開關效果下應用更低的電壓。這反過來又使更多的晶體管可以更緊密地部署在一起,提高密度。三星表示,這種方法可以將晶體管設計的尺寸縮小 35%(與 5nm FinFET 相比)。然而,預計GAAFET技術將比FinFET更快地枯竭的。

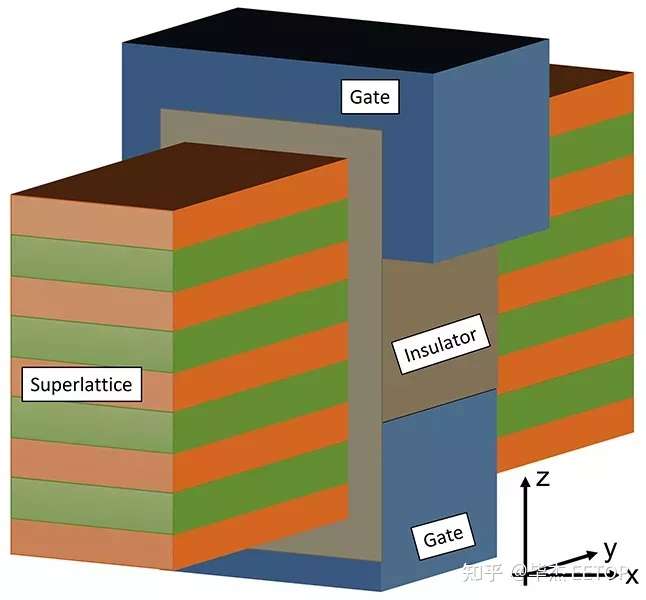

CasFET 的開發(fā)是晶體管制造設計的下一個可能步驟,它部署了垂直于晶體管傳輸方向的超晶格結構,允許可切換的級聯(lián)狀態(tài)。這實際上利用了從量子級聯(lián)激光器中學到的效應,并且基本上允許更細粒度的電壓控制。這是半導體縮放的限制因素之一。

該團隊目前正在開發(fā)第一個CasFET原型,并仍處于整體結構和材料的設計階段,試圖在成本、材料可用性、從典型的晶體管制造過渡的便利性和性能之間找到正確的平衡。就目前而言,該原型并沒有提供他們所尋找的性能特征。然而,這項工作很有希望,普渡大學已經(jīng)向美國專利和商標局申請了專利保護。

關鍵詞: GAA FinFET CasFET 級聯(lián)場效應晶體管

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導體創(chuàng)芯網(wǎng) 快訊

相關文章