Intel:未來封裝的巨變

2019-07-15 10:13:50 semiwiki 翻譯:半導體百科然而,至少對我來說,并不清楚的是,這些產品會被多迅速的接受,以及客戶會如何激進的擴大設計架構的多芯片整合空間。最近,我有機會參加由英特爾舉辦的高級封裝研討會,會后我認為:業界對高級MCP設計的計劃將急劇加速。

在研討會上,關于這項技術發展最引人注目的跡象,是英特爾封裝/測試技術開發(ATTD)副總裁Ram Viswanath的發言,他說 "我們開發了獨特的3D和2.5D封裝技術,并且我們渴望與客戶分享。產品架構師現在有能力追求具有前所未有的規模和功能多樣性的MCP。"這是出人意料的發言, 一些會員甚至要求Ram給予確認。毋庸置疑,世界上最大的半導體IDM正熱情地與客戶一起尋求MCP設計合作。

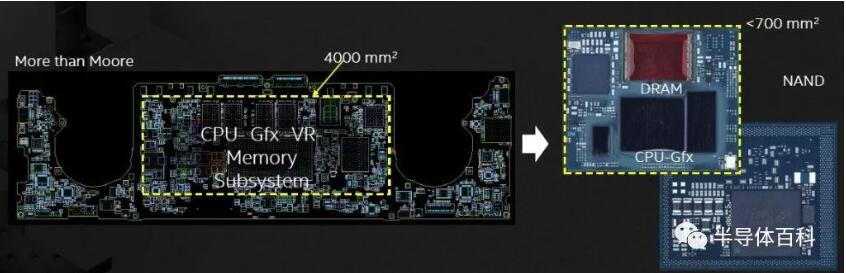

例如,下面的概念圖呈現了把CPU,GPU,VR加速器和存儲器架構封裝到一個僅占原獨立元件封裝方法六分之一大小的空間,原封裝的尺寸有可能很大 - 會高達100mm x 100mm。(英特爾Xeon系列的Cascade Lake服務器模塊是一個76mm x 72.5mm的MCP,包含兩個"全刻度尺寸"處理器芯片。)

對于保守的讀者來說,這與前段時間英特爾宣布剛剛起步的代工廠服務帶來的感覺是完全不同的。這里傳達了一個清晰的,簡明扼要的信息 - 新興的數據驅動應用程序將利用多芯片封裝集成技術(圍繞英特爾CPU或FPGA),英特爾ATTD業務部門會致力于支持這些獨特的客戶設計。

下面將介紹一些英特爾MCP的歷史,和2.5D和3D封裝技術的細節,以及一些正在進行中的對未來封裝技術的研究

MCP History

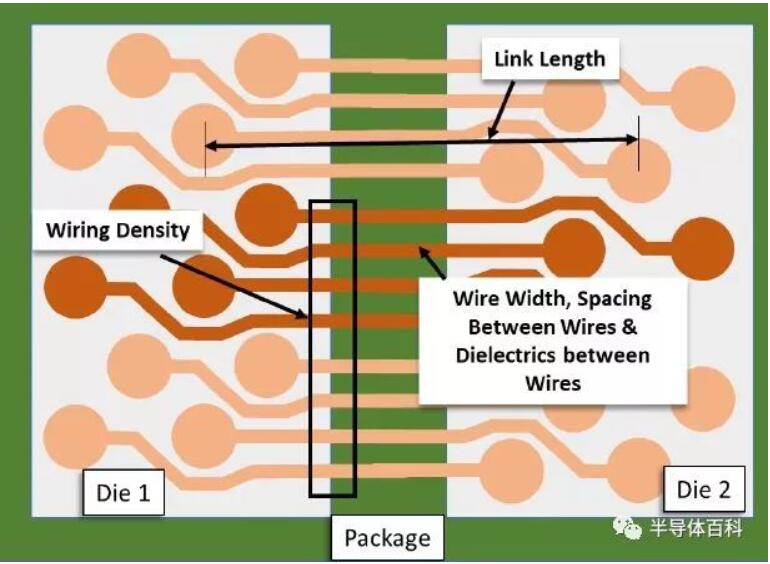

研討會結束后,我隨訪了Ram V.,,他對英特爾MCP技術的研發有豐富的見解。他說,"英特爾在多芯片封裝方面擁有大量的經驗。例如,我們正在推出一項獨一無二的嵌入式硅橋技術,用于芯片間封裝連接,已經研發了十多年。這種技術能做到芯片間寬接口連接,且具有低pJ/位功耗,以及芯片間低信號損耗和低成本的特性。"下圖描繪了相鄰芯片邊緣的bump塊之間的互連跡線- 一個關鍵指標是 (bump的密度和平均die周長內可繞線的跡線長度)

“技術開發的重點是將硅橋嵌入基于面板的有機封裝組裝流程中。橋接線的位置和角度要求非常苛刻。“,Ram繼續說道。

Ram展示了采用嵌入式橋接器的帶有HBM內存的Stratix FPGA模塊的示例。“此產品路線圖始于英特爾在收購之前制造Altera FPGA時的幾個SKU。自那時以來,FPGA應用已經大幅增長 - 現在整個Stratix產品線都有MCP產品。“他還展示了(未封裝的)最近宣布的帶有外部GPU的Kaby Lake CPU模塊的示例,利用芯片之間的嵌入式橋接器。

"對于來源于不同代工廠的芯片是否有明顯的封裝或可靠性問題?",我問道

"這項技術本就是與供應商合力開發的成果"他指著各種MCP模塊中的不同芯片繼續說,"這個是來自臺積電,這個是來自GF,這些是來自SKHynix的HBM內存堆棧。我們與全部的供應商都密切合作,制定了bump冶金規格和材料體積,BEOL介電材料特性,芯片厚度和翹曲度,所有這些芯片的都被證明是合格的。"

EMIB

嵌入式多管芯互連橋(EMIB)是用一小塊硅在MCP中的兩個管芯的相鄰邊緣之間提供自由的互連性。 EMIB目前集成了四個金屬化平面--2個信號和2個電源/地(主要用于屏蔽,但也可用于芯片之間的P / G分配)。

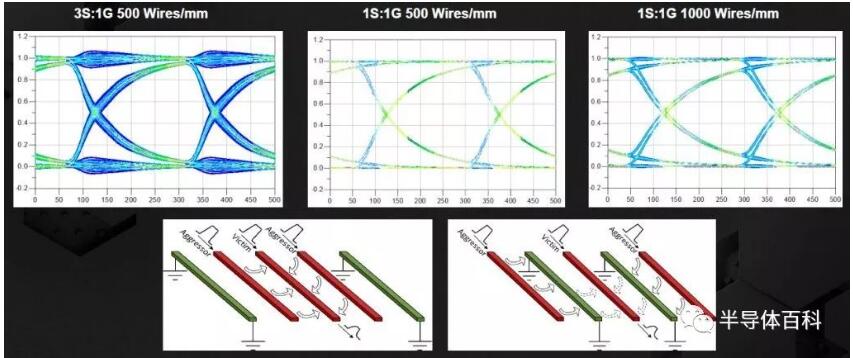

此外,英特爾的Si團隊分析了不同長度的信號和接地走線的不同互連拓撲的信號損耗 -請參見下圖。

英特爾研究員Ravi Mahajan提供了有關EMIB的其他技術信息。他指出EMIB平面的金屬厚度介于硅片RDL層和封裝跡線之間,實現了互連間距和損耗特性之間的平衡。“我們現在是2um的線寬和2um線間距,并朝著1um 線寬和 1um線間距努力。我們對EMIB的Si分析表明,長達8mm的長度仍能提供足夠的眼圖余量。從概念上講,EMIB可以達到~200平方毫米。“(例如,相鄰芯片邊緣之間的距離為25 mm,寬度為8 mm)

目前,橋接器的設計和制造由英特爾ATTD完成 - 本身沒有外部設計套件。“在ATTD上嵌入式橋接器的相鄰芯片的I / O焊盤平面圖的開發是一項協作努力。”,Ram表示。“在VDD IO和GND IO的設計上也考量了從整個封裝到EMIB周圍及芯片上的周邊bump陣列的電壓傳輸。英特爾ATTD還對復合封裝設計進行了熱和機械完整性分析。由于MPC新興市場的散熱水平可能很高,并且由于芯片與EMIB硅和有機基板之間的熱膨脹系數不同,因此bump接觸面的熱與機械性能分析至關重要。

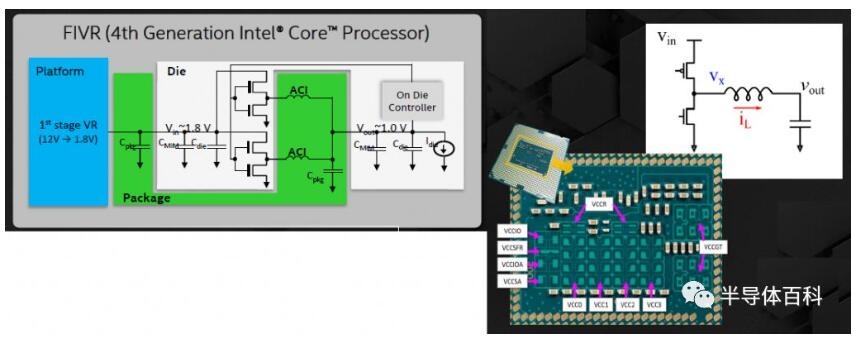

顯而易見但值得一提的是,封裝中EMIB硅的存在不會干擾將表面貼裝無源元件添加到整個組件的傳統工藝(例如,去耦帽)。在研討會上,對背面封裝金屬環電感器和SMT帽的支持得到了強調 - “自22nm工藝節點以來,英特爾CPU封裝集成了電壓調節和電壓域控制。封裝上的電感和電容元件是穩壓器設計中使用的降壓轉換器的一部分。“,Ram指出。和英特爾合作設計MCP的客戶也可以獲得此功能支持。

基于EMIB的設計的特性與使用硅中介層的2.5D封裝產品有很大不同。一方面,由于介質層跨越整個組件,因此Si介質層賦予了芯片間連接更大的靈活性。(較新的2.5D產品提供“縫合”光罩曝光之間的連接跡線工藝,以提供大于1X最大光罩場尺寸的介質層設計。)相反地,EMIB方法專注于相鄰芯片邊緣(寬,平行)連接。在研討會中提到,將多個橋接器集成到傳統封裝組件和最終封裝流程中使得100mmx100mm 介質層尺寸在500mm×500mm有機基板面板上成為可能。具有有機基板的EMIB實現了可觀的成本優化

3D “Foveros”

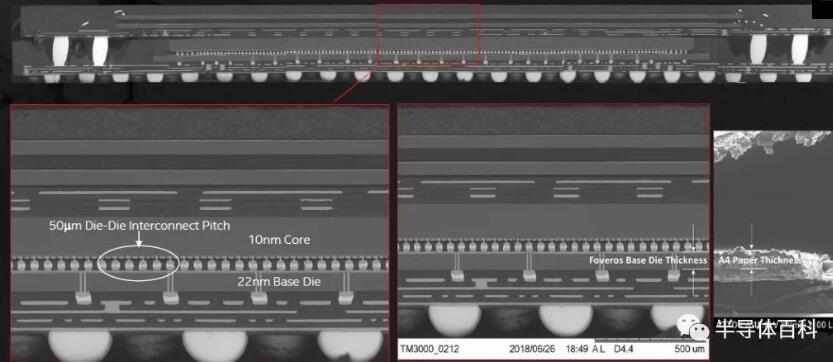

借助Lakefield CPU產品系列,英特爾推出了采用硅通孔的3D芯片堆疊封裝產品。下圖說明了3D芯片堆棧。

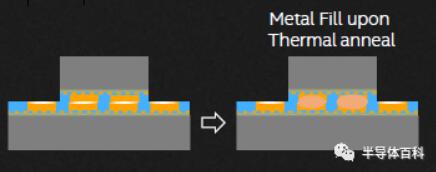

高級封裝研發的重點是減少TSV和微凸起的節距大小 - 目前的節距為50um,目標是為30-35um。這將需要從熱壓粘合轉變為獨特的“混合粘合”工藝 - 見下圖。

熱壓結合利用壓力和溫度來融合兩個模面上的裸露焊盤冶金,而混合結合始于(有些深奧的)拋光工藝,以在模具表面提供具有幾納米精確控制的“凹陷”的焊盤金屬。結合步驟利用(親水的,極端平面的)模具表面之間的范德華力,然后在退火過程中使金屬膨脹以產生焊盤連接。

另一個關鍵的3D封裝研發關注重點是壓縮芯片厚度- 高級3D封裝的目標是極力壓縮最終組件的厚度。“堆疊芯片的薄化加劇了裝配和可靠性問題。”,Ravi M.強調說。他舉了一個有趣的視覺例子,“考慮到比一張A4紙更薄的芯片的操作和翹曲要求。”(起始300mm晶圓厚度:~775um; A4紙張厚度:~50um)

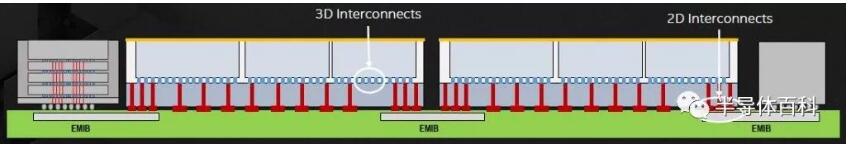

在不久的將來,將多個3D芯片組合作為大型2.5D拓撲的一部分的能力將被提供,配置Intel ATTD表示為“co-EMIB”。下圖說明了3D堆疊芯片與堆疊之間嵌入式橋接的組合概念。

Chiplets, KGD’s, and AIB

MCP技術的加速采用將依賴于廣泛的芯片組供應,其方式類似于SoC中的硬IP功能。如上所述,英特爾ATTD團隊已經解決了主要硅源的物理材料問題,以確保高組裝/測試產量和可靠性。然而,小芯片I / O之間的電氣和功能接口定義需要在整個行業范圍內集中精力進行標準化,以確保芯片級的互操作性。

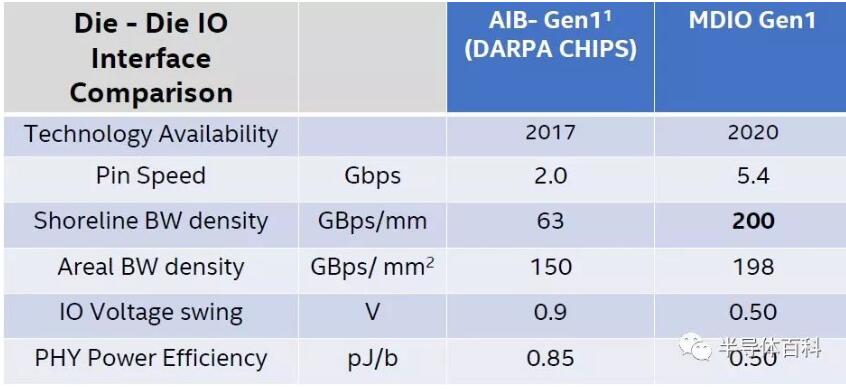

英特爾已發布了AIB規范,并且是DARPA“CHIPS”計劃的積極參與者,以推廣芯片級標準。(DARPA鏈接,AIB鏈接 - 需要注冊)有些令人驚訝的是,IEEE似乎沒有積極參與這項標準活動 - 很快,毫無疑問。

在研討會上,英特爾ATTD團隊表示,下一代芯片級接口規范(MDIO)正在進行內部活動,目標是將數據速率從2Gbps提高到5.4Gbps(在較低的電壓擺幅下優化功率)。

MCP產品設計將繼續進行,但采用的增長需要一個明確的標準 - “用于小芯片互連的以太網”,正如DARPA的Andreas Olofsson所描述的那樣。

基于芯片的設計還有另一個方面,在研討會上進行了簡要討論。 MCP的最終后燒入測試產率將取決于已知良好裸片(KGD)小芯片的測試和可靠性特征。 ATTD團隊表示,英特爾已對生產ATE設備開發進行了長期(內部)投資。突出的一個特定功能是能夠在晶圓級執行加速溫度循環測試,快速識別/分類早期失效– 以避免運送到封裝組裝的KGD在最終老化后不會產生大的良率損失。小芯片“IP”的供應商當然也需要以低測試成本解決如何提供高可靠性芯片的問題。

Futures

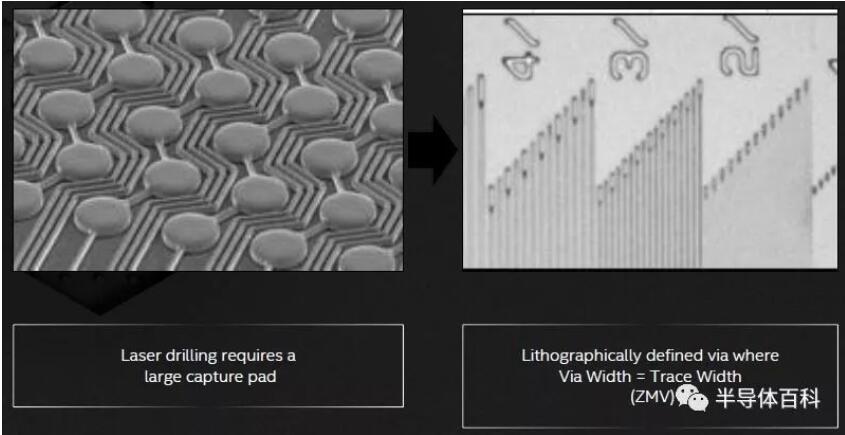

最后的研討會演講來自英特爾研究員Johanna Swan,他介紹了一些正在進行的高級封裝研發。最引人注目的機會是把跡線連接變成到通孔連接的工藝。不是上圖中描繪的大的通孔焊盤到跡線尺寸差異,“零未對準通孔”將使互連密度顯著改善。下圖說明了當前封裝跡線-通孔拓撲,以及2-4um走線寬度的新ZMV跡線連接。

目前基于環氧樹脂的封裝面板采用激光鉆孔 - 實現ZMV,一項新技術正在研究中。(Johanna表示,聚酰亞胺系列的可光成像材料可提供足夠高的通孔密度,但材料,工藝和成本限制要求使用環氧樹脂面板– 這就需要獨特的環氧樹脂工藝。)如果ZMV技術轉換對于生產,MCP互連(連線+空間)跡線密度將大幅增加- 當與微凸塊間距的改進相結合時,在大型MCP中實現的系統級功能將是非常令人印象深刻的。

Summary

研討會有三個關鍵要點。

•異構多芯片(芯片和/或小芯片)封裝將為系統架構師提供巨大的機會來追求功率/性能/面積+體積/成本優化。

•與采用硅中介層的2.5D封裝相比,裸片接口處的英特爾EMIB互連橋提供了一組獨特的成本/尺寸/復雜性權衡。

•英特爾ATTD團隊致力于為尋求數據驅動市場獨特產品解決方案的客戶提供先進的2.5D,3D和合并(co-EMIB)技術支持。

坦率地說,在最近的微電子學史上,現在應當是產品架構師工作最有趣的時期。