小芯片互連標準呼之欲出

2019-06-27 13:08:24 BRIAN BAILEY實際上,使用它們的唯一方法是使用專有接口和協議控制接口的兩端。唯一的例外是HBM2的定義,它使大量第三方DRAM能夠連接到具有高帶寬且功耗顯著低于芯片到芯片連接的邏輯器件。

小芯片的概念其實很簡單,就是硅片級別的重用。設計一個系統級芯片,以前的方法是從不同的IP供應商購買一些IP,軟核(代碼)或硬核(版圖),結合自研的模塊,集成為一個SoC,然后在某個芯片工藝節點上完成芯片設計和生產的完整流程。未來,對于某些IP,你可能不需要自己做設計和生產了,而只需要買別人實現好的硅片,然后在一個封裝里集成起來,形成一個SiP(System in Package)。所以chiplet也是一種IP,但它是以硅片的形式提供的。

這與設計和制造印刷電路板(PCB)的方式非常相似,只有一切都在一個封裝內發生。當所有裸片由同一公司設計和制造并且可以對所有裸片進行修改時,這被稱為3D設計。

如果沒有標準,市場將無法實現。"你必須擁有芯片和SoC之間連接所必需的行業標準,” eSilicon戰略和產品副總裁Hugh Durdan說。“除非有標準,否則你將永遠不會在小芯片和人們想要的其他SoC之間擁有必要的互操作性。HBM是芯片到芯片封裝內接口的一個很好的例子,并且非常成功。"

這些接口會是什么樣子?Netronome的硅架構程序管理主管Bapi Vinnakota說:“它們位于板和模上接口之間。”“它具有板式接口的一些特性,比如必須有傳輸大量數據的機制,但需要像on-die接口那樣具有低延遲。該接口是在板級和裸片級工作的混合。”

選擇接口

Marvell于2015年推出了模塊化芯片(MoChi)架構,這是一種基于Kandou總線接口的小芯片模型,并且它一直在內部使用該方法用于自己的產品。

“我們遇到的第一個問題是選擇接口 - 什么是運行芯片間通信的最佳IP,”Marvell的網絡CTO Yaniv Kopelman說。“我們想要在有機基板上運行而不是內插器或者是InFO(臺積電的集成扇出)類型的封裝,因為我們不想要高成本封裝,我們不希望與單個供應商綁定。第二個問題是架構。使用小芯片,您必須在中間劃分IP。問題是在哪里切割以及如何開發架構,以便你可以在需要時切換CPU。為此,你必須查看組件的延遲并處理邏輯實現。第三個挑戰是將這一切投入生產。在一個演示中構建IP很容易,但從那里到生產有價值的東西還有很長的路要走。“

現在,在專用新接口出現的同時,正在使用通常為其他目的定義的現有接口。CadenceIP Group的高級產品管理集團總監Rishi Chugh 提供了一些例子。“ 芯片互聯網論壇(OIF)有針對小芯片和JEDEC委員會的舉措。還有像英特爾這樣的組織,它擁有高級接口總線(AIB),而英特爾則愿意提供規范。“

新的CEI-112G-XSR(超短距離)項目也旨在實現OIF項目旨在實現光學引擎內部或芯片之間的封裝內互連,具有高吞吐量密度和低標準化功率,最大可達50 mm。系統級封裝(SIP)設計導致需要在有機封裝襯底上的多個芯片之間支持多達50mm的跡線長度。以支持混合技術,特別是用于構建光學引擎。封裝基板。

英特爾的AIB是一種芯片到芯片的PHY級標準,它采用模塊化方法進行系統設計,并具有芯片級知識產權(IP)模塊庫。

“AIB使用時鐘轉發的并行數據傳輸機制,類似于DDR DRAM接口,”Chugh解釋說。“它與工藝和封裝技術無關,可以利用英特爾的嵌入式多模互連橋(EMIB)或臺積電的CoWoS(晶片對基板的晶片)等技術。”

Intel現在免費提供了AIB接口許可,以實現廣泛的小芯片,設計方法或服務提供商,代工廠,封裝和系統供應商的生態系統。

Synopsys的 DesignWare IP子系統產品營銷總監Mick Posner說:“英特爾有很大的優勢,因此,AIB是一個明顯的初始贏家。”如果您深入研究AIB或其他建議的接口,它們每個都有不同領域的弱點,無論是性能還是功能。如今所指定的AIB具有性能限制,可以在下一代輕松解決。沒有必要提供額外的性能和低延遲。沒有明顯的贏家。“

每個都有自己的優勢。“OIF擁有小芯片的衍生產品,他們稱之為XSR超短距離,”Chugh補充道。“這針對封裝中的裸片或芯片到芯片互連。因此,該行業正在推進標準化IP。我認為我們今天沒有最好的解決方案,因為這是第一次努力,但這是朝著正確方向邁出的一步。標準并不總是最好的,但你必須邁出第一步。“

實現這一目標的好處是大大縮短了上市時間并降低了開發成本。“我們的客戶有時可能希望將我們的ASIC解決方案與單個封裝中的其他組件結合在一起,然后可以選擇將可靠性認證納入一個封裝,而不是單獨對所有元件進行認證,” Olivia Slater,Adesto Technologies的運營和物流經理。“根據正在開發的SiP,這可以使認證和最終測試解決方案不那么復雜。”

性能

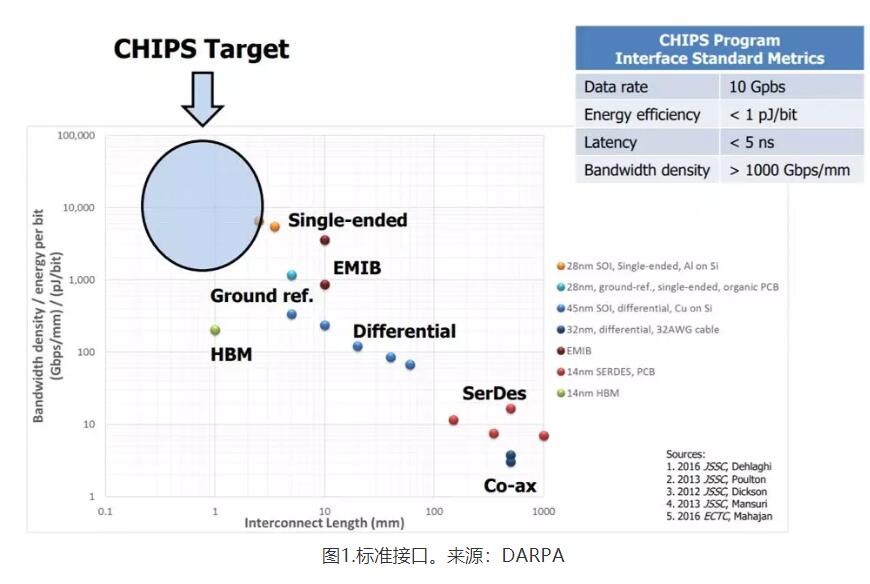

一些組織正在嘗試定義這些新的接口,包括DARPA的一個名為通用異構集成和IP重用策略(chip)的項目。DARPA在圖1中定義了目標性能空間。

圖1.標準接口。來源:DARPA

性能需求受到關鍵物理元素的約束。“當發送數據時,人們尋找的兩個標準是功率效率和帶寬,”Chugh解釋說。“從裸片的邊緣開始,你能在不浪費面積的情況下發送的最大數據是多少?” 在裸片的邊緣,每毫米我可以傳輸多少數據。效率是人們將其測量為pJ / bit的功率方面。將每個數據位從一個芯片發送到另一個芯片消耗了多少功率。“

“追蹤的數字是品質因數(FOM),”Vinnakota補充道。“只要你在裸片之間連線,就會面臨beachfront 問題。你不得不從一個芯片邊緣將這些引線從芯片上取下,你可能會燒掉焊盤。FOM是邊緣上的線性密度(1 TB / mm),然后移動數據需要多少皮焦耳。"

多層

小芯片接口與任何其他類型的接口一樣,往往是多層的,具有物理,鏈接,傳輸和其他層,所有這些都旨在確保穩健的通信。ODSA發布了一個圖表,顯示了圖2中可能需要考慮的一些層。

物理層

物理層基本上可以是并行或串行的。“串行的優勢在于,您通常最終會使用更少的連線,但成本會增加設計復雜性,”Vinnakota解釋道。“并聯通常可以在較低的速度下運行。”

但選擇比這更復雜。“并行接口(例如AIB)的優點是延遲非常低,功耗和面積非常低 - 所以它從架構的角度來檢查所有的盒子,” Durdan說道,“主要缺點是它確實需要硅插入器或類似的芯片封裝技術,這會增加成本。“

但選擇比這更復雜。“像AIB這樣的并行接口的優點是它具有極低的延遲、極低的功耗和區域—所以它從架構的角度檢查所有的框,”Durdan說。“主要的缺點是,它確實需要硅插入器或一些類似的封裝技術,這增加了很大的成本。串行接口的缺點是,對于某些應用,您不能容忍與SerDes相關的延遲。”

在此應用中,SerDes可能比芯片到芯片解決方案更簡單,更快速。“我看到有人試圖使用SerDes進行連接,但是它們的體積更小,功耗更低,利用了你只通過非常短的通道進行通信的事實,”Durdan說。“這些是同一封裝內的多個芯片,而不是整個電路板或背板。”

AIB是一種并行接口,包括以1或2GHz運行的線束。“AIB有2000條線,幾乎強制使用硅插入器或橋接器,”Vinnakota補充道。“如果你是一家小公司,你可能買不起插入器。相反,您可能需要一種基于有機基板的產品,這意味著您需要一種更少連線的技術。內插器可能的線密度比有機基板的線密度高許多倍。“

時鐘是兩種接口類型之間的主要區別。“通過并行接口,你需要做時鐘轉發等事情,”Chugh說。“使用SerDes,時鐘和數據合并在一起。通過兩個設備維持數據的并行性,并且時鐘轉發保持兩個設備之間的時鐘驅動器的健全性。它使它成為一種模塊化設計,你可以在假設中思考,“如果你有一個裸片并且裸片上有一個數據路徑,你就可以在整個數據路徑上將裸片切成兩塊。” 現在你有兩個芯片,你試圖在同一個封裝中將它們拼接在一起,并且這個IP連接了并行數據通路。"

數據路徑之外還有其他一些注意事項。“你需要考慮諸如集成自檢之類的東西,一個集成的1149邊界掃描機制,當它嵌入到封裝內時,可以到達芯片,所以它不僅僅是跨越數據傳輸接口,“Vinnakota警告說。

其他問題也仍不明朗。西門子企業Mentor的Calibre DRC營銷總監約翰•弗格森(John Ferguson)表示:“關于在芯片中使用ESD保護的必要性存在一些爭議。”“一旦你做到了這一點,它們就會被封裝起來,因此沒有機會與人體互動。”其中一些會消失,但還有其他的電沖擊可能會變得更有問題。這很難說。已經有一些協會對它們進行了調查,大多數都提出了最佳實踐。”

PCIe出現在PHY ODSA列表中,如圖2所示,因為它已經得到了大量產品的支持。它被認為是一種無需修改就能將帶有PCIe接口的芯片轉換成芯片的快速方法。

“服務器和高端設備中的大多數芯片已經具有PCIe接口,” ArterisIP營銷副總裁Kurt Shuler說。“隨著您添加PCIe附帶的更多即插即用功能,您會增加堆棧的復雜性。因此,您可以從低級別接口轉變為強大的軟硬件標準。“

超越PHY

PHY標準的出現是不夠的。這不允許真正的功能分離。“在PHY層上已經做了很多工作,用于將小芯片組合在一起,但是要使它們作為單個產品工作,您需要一個體系結構接口。”Vinnakota解釋說。“ODSA希望在開放的PHY層之上建立一個開放的接口。”

如果您有一組小芯片,您希望它們像單個芯片一樣一起工作。Vinnakota補充說:“協同工作的定義應該是呈現某種語義,這樣運行在任何一個模塊上的軟件都認為所有組件在邏輯上是一個整體。”芯片之間的接口可以遵循I/O語義或內存語義。我們認為正確的答案是內存語義。在頂部有三種類型的內存移動。一個是連貫的數據移動。狀態在所有處理元素之間一致地共享。其次,您需要非相干數據移動,因為相干性非常昂貴,尤其是當您希望相干性的區域變得更大時。你要么以時鐘速度為代價,要么以延遲為代價來實現一致性。也許你有一個統一的內存空間,但是留給程序員來管理非一致的內存。”

一致性增加了軟件的簡單性。Shuler說:“我們的想法是能夠設計這些,假設有一個CCIX連接,它將能夠連接到任何其他具有CCIX接口的芯片。”“仍然存在一些問題。在設計這兩個芯片時,仍然需要在開始時考慮整個系統架構和內存層次結構的上下文。在未來,也許不需要。但是如果你看一下規范,它仍然是一個相當底層的接口。有一些交易正在進行,但你仍然必須對另一個小片如何工作做出很多假設。可以使用不同級別的CCIX連接,當您達到更高級別時,更多的連接會得到處理。夢想是在兩個芯片上實現CCIX連接。把他們的身體掛在一個裸片或板上,它只是工作。但今天情況并非如此。”

不過,要想成功,這需要一個系統級的解決方案。Shuler指出:“你永遠無法避免有人必須查看整個系統。”“你要做的是獲取多個處理元素,每個元素都需要訪問內存,你希望它們之間有一個共同的視圖。這不僅關系到連接級別,而且關系到芯片的總體架構。這可能是架構指導方針必須被創建——需要連接到芯片內部的什么,才能符合這個即插即用標準。即使是在軟件方面,也可能需要一些標準來解釋如何與這些類型的芯片進行通信。”

傳輸信息

在短期內,某些信息可能必須以舊有方式傳輸。“今天使用IP,您可以獲得指定時間和功率的信息,當您談論裸片時,您將開始擁有更多信息,因為它們處于不同的工藝和不同的金屬堆疊和厚度,”Ferguson說。“在某個地方,所有這些細節都需要定義,以便他們知道如何將它們組合在一起。”

可能還需要新的型號。Shuler說:“有一點是不同的,那就是他們想要一個模型,而且可能是在不同的抽象層次上,讓其他chiplets的不同部分與他們自己的部分結合起來,能夠滿足性能需求,處理能力和系統的其他方面。”“有翻轉晶體管的觀點,還有連接的物理效應。這將不僅僅是一個數據表的共享。這是我的一組模型,你甚至可能需要其中一些用于預售。”

也可能需要新型號。“有一點不同的是,他們需要一個模型,并且可能需要在其他小芯片的不同部分的不同抽象層次上與其自身結合,并能夠滿足性能要求,處理功率和系統的其他方面,“Shuler說。“存在翻轉晶體管的場景,然后還有連接的物理效應。將共享不僅僅是數據表。”

IP供應商可能需要開發新技能。“純粹的IP玩家在這方面已經有點掙扎,因為他們沒有設計芯片或封裝的技能,”Durdan說。“芯片間的互連和裸片間的互連與其他IP的最大區別在于,封裝是解決方案中不可或缺的一部分。”

結論

雞和蛋問題正在慢慢解決。標準響應市場,但沒有必要的標準,市場就不會發展。

專有接口正在解決如何連接芯片的難題,盡管最終可能是昂貴的解決方案,但是板級標準也提供了一條快速路徑。

但即使這些問題沒有得到解決,一些公司也永遠不會回到單一的解決方案。不可能確切知道什么級別的即插即用是正確的。