10nm FinFET的設計流程取得大進展

2015-07-07 07:39:51 日經BP  |

| 臺積電的Willy Chen發表演講。 《日經電子》拍攝。 (點擊放大) |

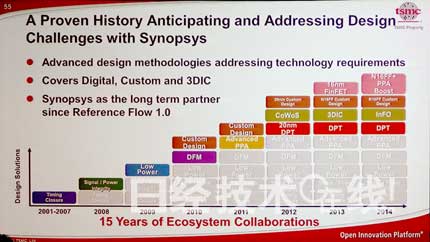

本次演講是在新思科技、ARM、臺積電借第52屆設計自動化會議之機,于2015年6月8日聯合舉辦的“Collaborating to Enable Design with 16-nm and 10-nm FinFET”上發表。演講人是臺積電設計暨技術平臺副處長Willy Chen(圖)。

關于16nm FinFET+工藝的設計流程,在2014年,臺積電發布了在參考流程中提供的支持(圖1)。16nm FinFET+工藝是由當初的16nm FinFET工藝改進而來,通過改變鰭片形狀等,性能提高了15%。

|

| 圖1:參考流程的推移。 |

16nm FinFET的16個項目正在推進

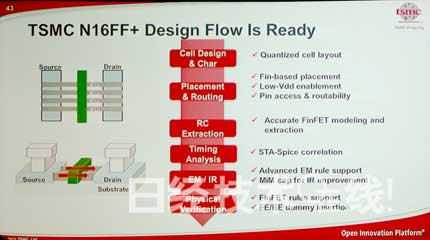

Chen表示,面向16nm FinFET+工藝的設計流程早已準備就緒(已進入可實際設計芯片的狀態)(圖2)。現在,16個開發項目正在推進,到2016年底,將有50個設計送廠生產。

|

| 圖2:16nm FinFET+(N16FF+)的設計流程。 |

臺積電直到16nm工藝,才首次將FinFET應用于量產(20nm之前采用平面晶體管),N16FF+流程中新增加的功能,很多都與FinFET有關。比如說,布局布線中的自動格線置放、寄生RC提取中的高精度FinFET建模、物理驗證中的FinFET規則支持等。

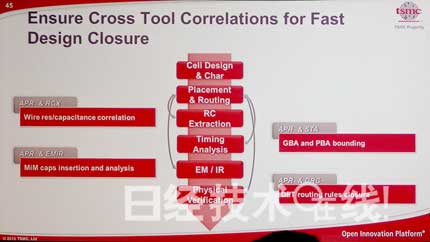

Chen重新指出,隨著工藝向16nm、10nm的微細化,自動布局布線與其他工序的聯動將變得愈發重要(圖3)。比如說,在自動布局布線和寄生RC提取中,布線電阻與電容的相關性,在自動布局布線與EM(electronic migration)/IR壓降分析中,MiM(metal insulator metal)電容的插入與分析等。

|

| 圖3:工序之間的聯動愈發重要。 |

10nm采用三重曝光

|

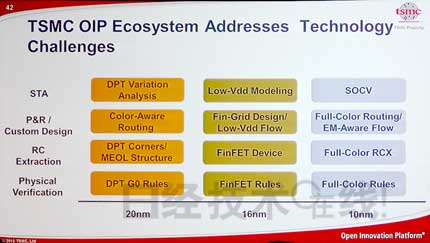

| 圖4:各代工藝的新課題。 |

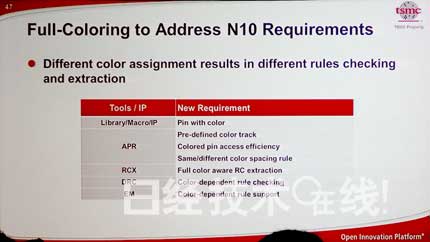

對于20nm之后的16nm工藝,適應FinFET是主要課題。而10nm工藝將采用三重曝光(通過分3次進行曝光,形成在28nm工藝之前,經1次曝光在Si上形成的圖案)。臺積電把設計三重曝光時,劃分第1次曝光數據、第2次曝光數據和第3次曝光數據叫作“全分色”(Full-Coloring)。另外,雖然這次沒有發布,但根據推測,之后的7nm工藝估計將會采用四重曝光。

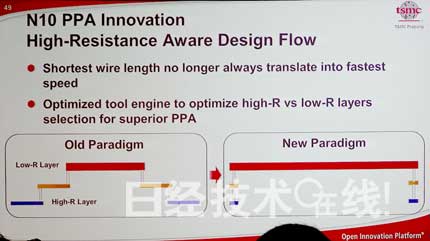

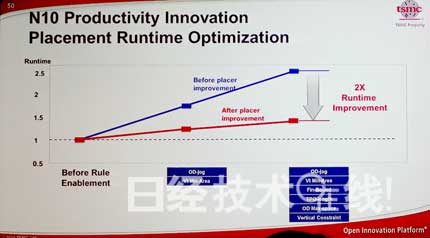

在采用三重曝光的10nm設計流程中,規則檢查和寄生成分提取有所變化(圖5)。而且,面向高速信號,還需要借助使用低電阻布線層的一維布線(圖6)、布局的多功能化和高速化(圖7)。

|

| 圖5:10nm工藝的規則檢查和寄生成分提取的課題。 臺積電的幻燈片。 (點擊放大) |

|

| 圖6:一維布線。 臺積電的幻燈片。 (點擊放大) |

|

| 圖7:改進布局。 |

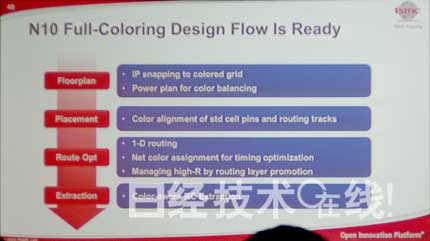

接近成品的驗證芯片送廠生產

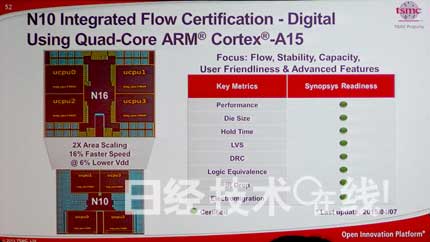

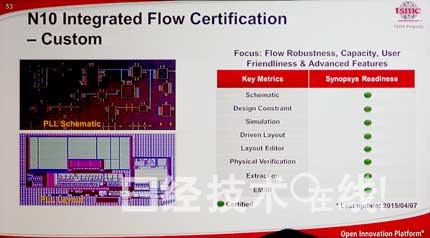

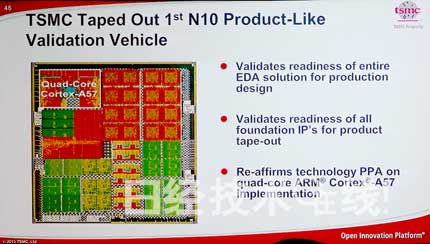

Chen表示,10nm工藝的設計流程也已準備就緒,可供客戶使用(圖8)。臺積電在數字設計方面,使用四核的“ARM Cortex-A15”進行了驗證(圖9)。在定制和模擬設計方面,使用PLL完成了驗證(圖10)。而且,接近成品的第一款驗證芯片已經送廠生產。這款驗證芯片集成了四核的Cortex-A57等(圖11)。(記者:小島郁太郎)

|

| 圖8:10nm FinFET的設計流程。 |

|

| 圖9:在數字電路中的驗證。 |

|

| 圖10:在定制電路中的驗證。 |

|

| 圖11:接近成品的第一款驗證芯片。 ) |