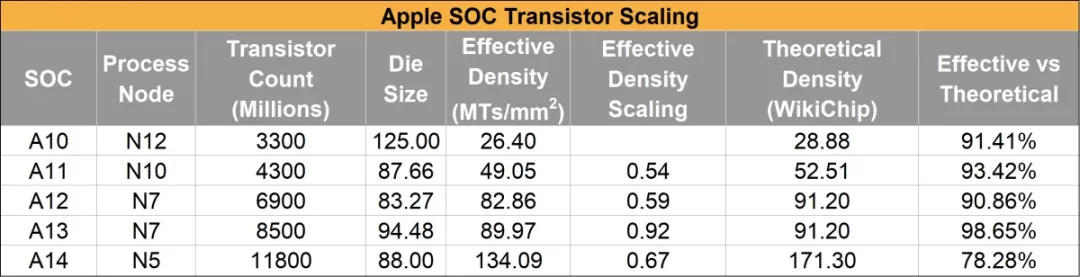

晶體管密度因不同的芯片結構而異。邏輯結構可以在每個新節點上很好地擴展,但是如今SRAM,I / O和模擬部件很難擴展,因此代工廠發布的峰值是高度理論性的,而實際數字是取決于設計。

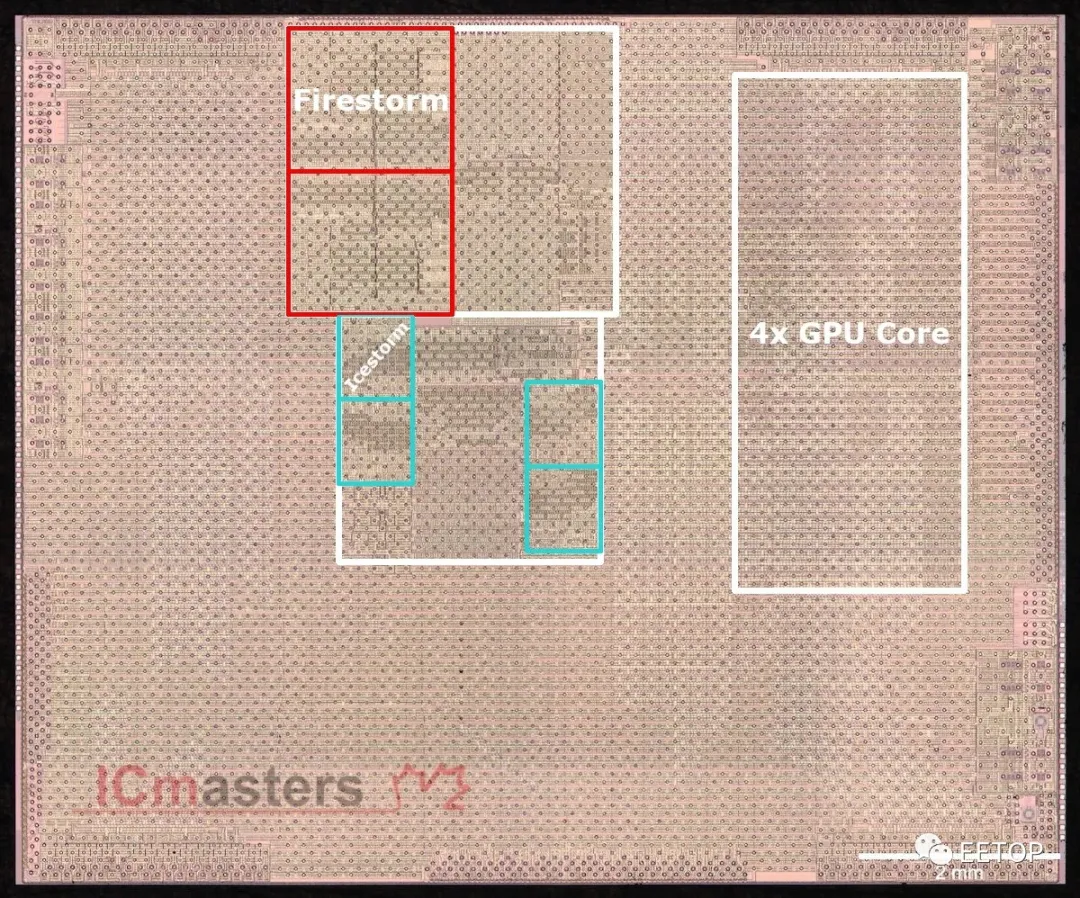

同樣,芯片的某些部分必須以更高的時鐘頻率運行(例如,通用內核)。通過使用通常更大的高性能電池,這些零件可能會犧牲性能密度。實際上,考慮到蘋果公司對最終性能的關注,其SoC通常具有大容量緩存以及可能進行其他性能優化。

臺積電的N5節點與之前的微縮有所不同,顯示出SRAM擴張放緩的跡象。盡管是一個完整的縮小與邏輯,SRAM是一個1.35倍縮小,這個數字被夸大了。因此臺積電的指引是N5可使晶片面積減少35%-40%。半分析預計,這將是一個趨勢,并將持續與新的節點。臺積電和三星已經在展示3D堆疊SRAM,這將有助于緩解密度問題。

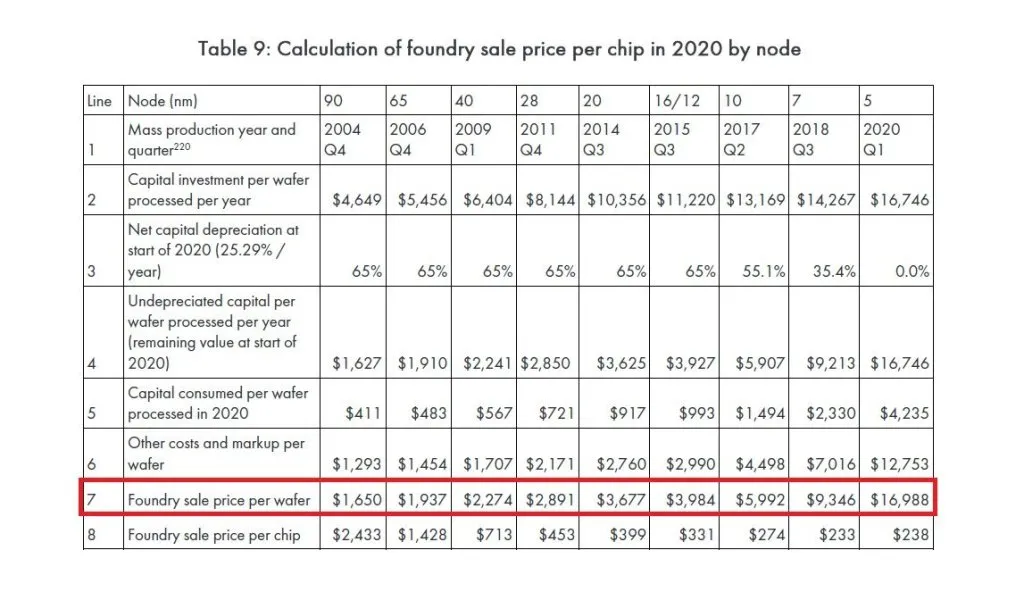

3D堆積并非萬能的,成本縮減已經開始大幅放緩。臺積電N5晶圓定價在1.7萬美元左右,顯然每個晶體管的成本并沒有下降。即使SRAM的縮放速度跟上,每晶體管的成本從N7到N5也將保持不變。