顛覆想象!臺(tái)積電將推出巨型芯片,大小如同吐司面包片!

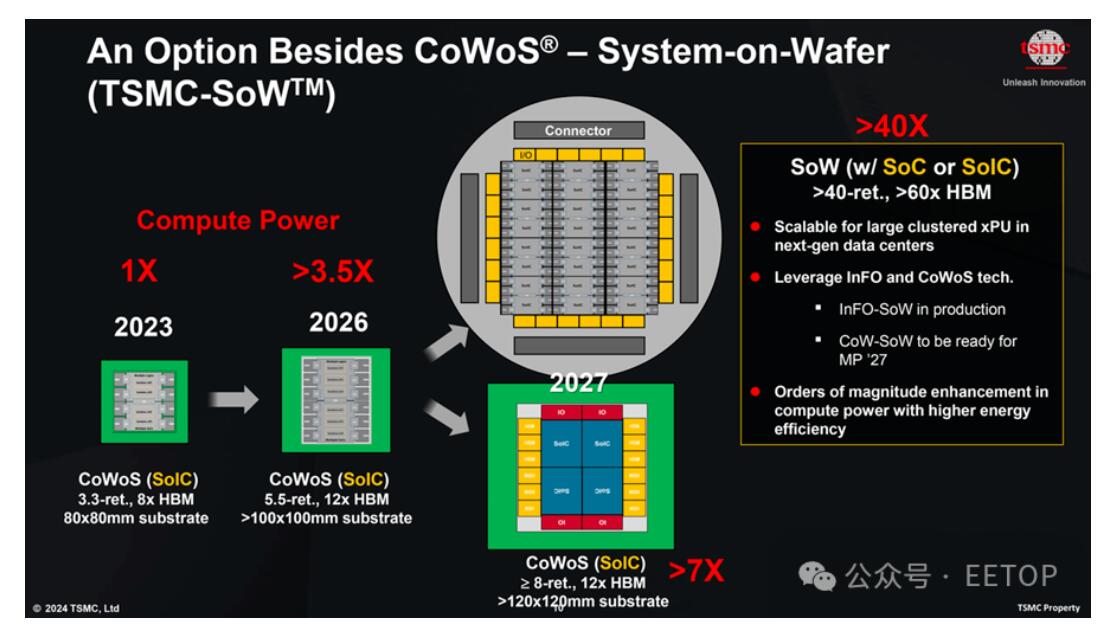

2024-04-29 17:12:57 EETOP臺(tái)積電在其北美技術(shù)研討會(huì)上宣布,正在開發(fā)其基板芯片(CoWoS)封裝技術(shù)的一個(gè)版本,該技術(shù)將使系統(tǒng)級(jí)封裝(SiP)比現(xiàn)有尺寸大兩倍以上。這些將使用120x120mm2的巨型封裝(與吐司面包片大小相當(dāng)),并將消耗數(shù)千瓦的電力。

現(xiàn)有的最新版本的CoWoS允許臺(tái)積電構(gòu)建比光掩模尺寸(或十字線,858mm2)大出約3.3倍的硅中介層。因此,邏輯、8 個(gè) HBM3/HBM3E 內(nèi)存堆棧、I/O 和其他小芯片最多可以占用 2831mm2。AMD 的 Instinct MI300X 和 Nvidia 的 B200 使用了這項(xiàng)技術(shù),盡管 Nvidia 的 B200 處理器比 AMD 的 MI300X 大。

下一代 CoWoS_L 將于 2026 年投入生產(chǎn),能夠?qū)崿F(xiàn)約現(xiàn)有尺寸的 5.5 倍,這意味著 4719mm2可用于邏輯、多達(dá) 12 個(gè) HBM 內(nèi)存堆棧和其他芯片。此類 SiP 還需要更大的基板,根據(jù)臺(tái)積電的PPT,我們將看到 100x100mm2的基板。因此,此類處理器將無法使用 OAM 模塊。

臺(tái)積電不會(huì)止步于此:到2027年,它將擁有CoWoS技術(shù)的一個(gè)版本,該技術(shù)將使轉(zhuǎn)接層的尺寸達(dá)到八倍或更多,這將使小芯片的空間達(dá)到6,864mm2。臺(tái)積電設(shè)想的其中一種設(shè)計(jì)依賴于四個(gè)堆疊的系統(tǒng)集成芯片(soic),搭配12個(gè)HBM4內(nèi)存堆棧和額外的I/O芯片。這樣一個(gè)龐然大物肯定會(huì)消耗大量的電力——將會(huì)達(dá)到數(shù)千瓦,并且需要非常復(fù)雜的冷卻技術(shù)。臺(tái)積電還希望這種解決方案使用120x120mm2的基板。

有趣的是,今年早些時(shí)候,博通公司展示了一款定制的人工智能處理器,它擁有兩個(gè)邏輯芯片和 12 個(gè) HBM 內(nèi)存堆棧。我們沒有這款處理器的規(guī)格,但它看起來比 AMD 的 Instinct MI300X 和 Nvidia 的 B200 更大,不過沒有臺(tái)積電計(jì)劃在 2027 年推出的那么大。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章