深度解析:集成電路ESD防護、閂鎖效應的測試方案及失效驗證流程

2023-11-13 12:04:06 閎康科技、technews(臺)任何電子產品都有其使用期限,以及對可靠性的要求。那么如何去度量產品的可靠性好不好呢?基本上就會考慮使用環境的條件,如電壓、溫度、濕度或任何環境下不利的因子,代入失效模型后,便可估算出產品的使用年限。

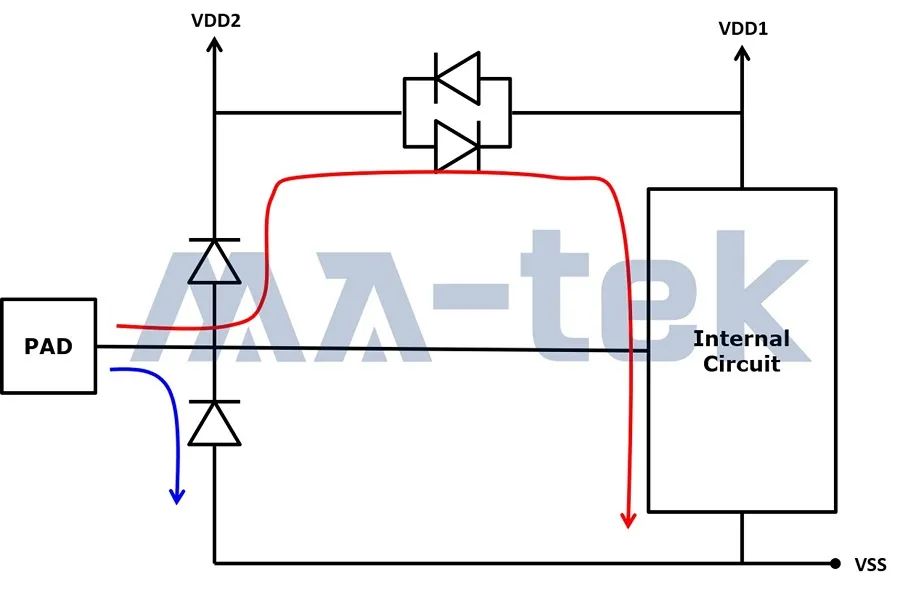

在我們所身處的環境中,靜電是無所不在的殺手,既然靜電無法完全預防,那么為了能夠在電荷流經集成電路時全身而退,IC 設計上就會在引腳旁設計靜電放電(Electrostatic Discharge,ESD)防護電路保護芯片,就像在大樓頂端設置避雷針的目的一樣,當雷擊中大樓時,能夠有引流的作用,確保大樓內的電器不會受損。此外,由于元件結構的特性,所謂的閂鎖(Latch-up,LU)效應會造成集成電路在操作時有大電流的現象而引起功能上的問題,甚至會使得芯片永久損傷,這同樣也需要在芯片設計上來避免LU 的問題。

為了驗證ESD 與LU 的防護能力,第一道課題就是如何運用專門的測試機臺,遵循國際規范定義的條件與步驟,確認集成電路在ESD 與LU 的可靠性。若該電路元件無法通過ESD 與LU 測試,且已找出驗證不過的原因之后,第二道課題便是如何進行芯片設計上的補強。本文即是針對此兩個課題闡述ESD 與LU 在測試前的準備事項、判斷標準、以及元件失效后的問題真因解析流程。

測試前的準備

在初次進行ESD 與LU 測試前,一般會遇到的問題是該如何規劃測試方案與執行,以及如何與測試專案主管溝通。為提升雙方溝通效率,可以依下述幾項主題提供資訊:

一、測試規范

在進行測試前,需先設定遵循的國際標準規范,規范的制定有其立論基礎,因此ESD/LU 測試通過驗證后,即代表獲得了客戶的信任與使用上的保證。以下是不同測試項目與其對應的國際標準規范。

MIL-STD:元件類和部分驅動IC

AEC-Q100 或AEC-Q101:車規認證

JEDEC:其余皆使用消費型產品規范

AEC-Q100 或AEC-Q101:車規認證

JEDEC:舊規范JESD22-C101F 和新規范JS-002-2022 ,絕大部分產品是使用消費型產品的JEDEC ,且建議客戶遵循最新的JS-002-2022。

JESD78F:消費型產品

AEC-Q100:車規認證

二、測試條件 1. HBM

建議從500V 執行,依序1KV, 2KV, 4KV, 8KV。

2. CDM

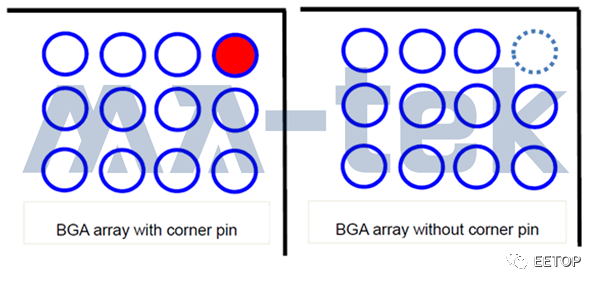

JEDEC 的安全標準是500V,AEC-Q100 另外會多增加Corner Pins 的標準到750V(圖一),電壓測試級距則建議依序為250V、500V、750V 到1000V。

3. LU

基本上依據規范只需要做到信號腳位+100mA / -100mA,電源腳位做到1.5*VDDmax,業界習慣會多往上一個級距測試到200mA。此外還需提供額定電壓與極限值以為操作條件之設定。

圖一:BGA 封裝腳位的Corner Pin 示意圖。左圖是有Coner Pin 設計者,其位置在紅色圈圈處,此腳位的CDM 測試標準需達750V。而右圖則是無Coner Pin 設計者。

三、測試顆數

HBM /CDM / LU:依據規范建議每個測試條件數據皆要3 個樣品。

四、IC Package Outline Drawing(POD)

需提供測試腳位的名稱、腳位類型(Input / Output / IO / Power / GND)與排列位置,以方便評估分析時間與條件設定,也是制作測試治具的依據。

五、HBM 測試組合

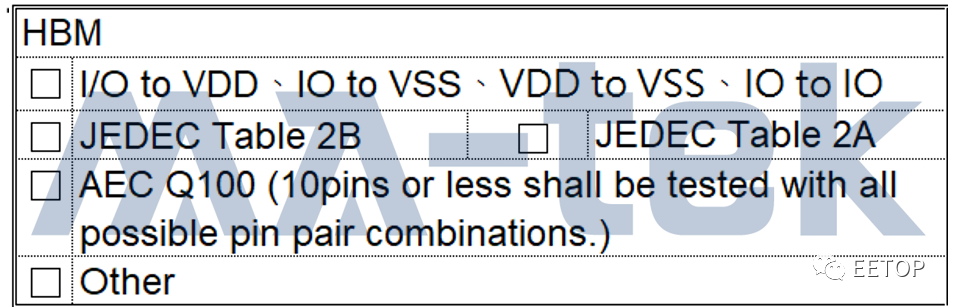

在選擇MIL-STD 規范時,表一第一列的四種測試組合皆可以選擇,在此規范下,各個Power Domain的Power/Ground 可并接在一起。在選擇JEDEC 規范時有Table 2A or 2B 選擇,相同Power Domain 的Power/Ground 彼此可并接,但不同Power Domain 的Power/Ground 間是不互接的,在此基礎下,所有的IO 腳位對不同的Power Domain 打ESD,此為Table 2B,而IO 腳位僅對自己所屬的Power/Ground 打ESD 則為Table 2A。若要使用最嚴謹的測試條件、不清楚應使用哪種測試組合或車規驗證時,建議使用Table 2B。至于車規AEC-Q100 的認證,若是封裝腳位數小于等于6 個的話,那么任何2 根腳位間的排列組合皆需驗證。

表一:第一列為IO 與Power/Ground 間的測試組合,第二列與第三列為欲采用的規范。

LU 特殊測試要求

LU 的測試目的是為了觀察是否會有異常的信號干擾導致激發出大電流的現象,因此在考慮設定的測試條件與環境下實際會發生的狀況后,一些客戶會選定某些條件進行LU 測試,如下所述。

一、高溫測試

在高溫下由于漏電升高,易觸發寄生硅控整流器(Silicon Controlled Rectifier,SCR)啟動而產生LU 效應,故可選擇常溫或高溫(視產品規格的最大操作溫度或者Tj 溫度而定)兩種測試環境,AEC 規范則是強制高溫測試。

二、Quiescent Current

高性能運算(High Performance Computing,HPC)IC 具有較高的Quiescent Current,隨著此類IC 市占率逐漸提高,LU 測試機臺已不能滿足高電流的要求,需另外訂制High Current LU 治具與外接高功率量測儀器。

三、Pattern

一般IC LU 測試是靜態測試,即輸入的電壓與電流是定值,但實際IC 操作是動態的,輸入輸出腳位有高低電壓周期性的變動,因此LU測試下輸入Pattern是為了模擬在IC 動態輸入下LU 真實的作動行為。

測試Pass/Fail 判斷標準

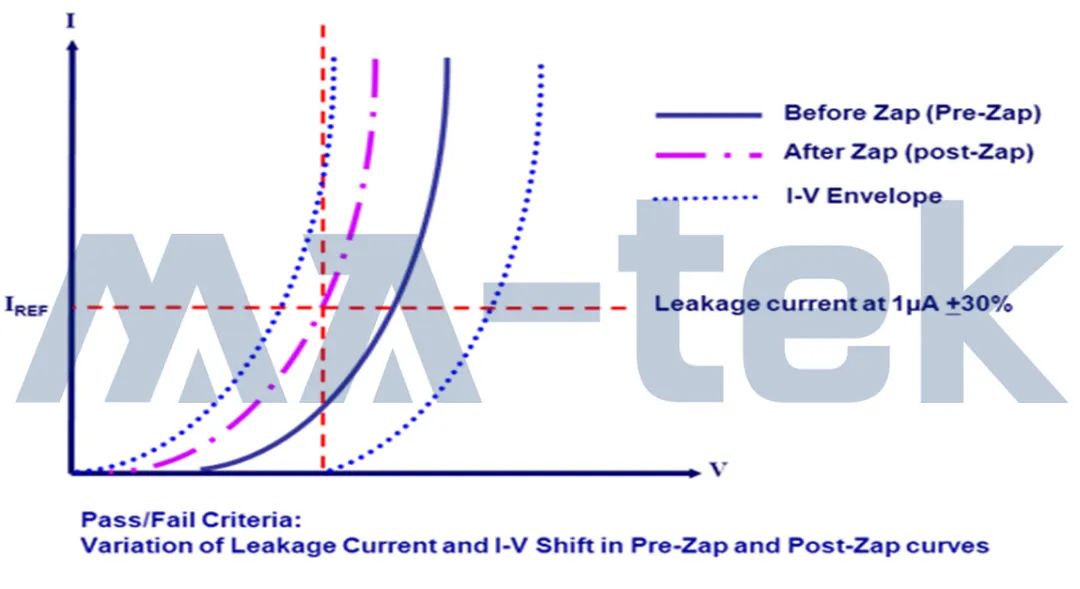

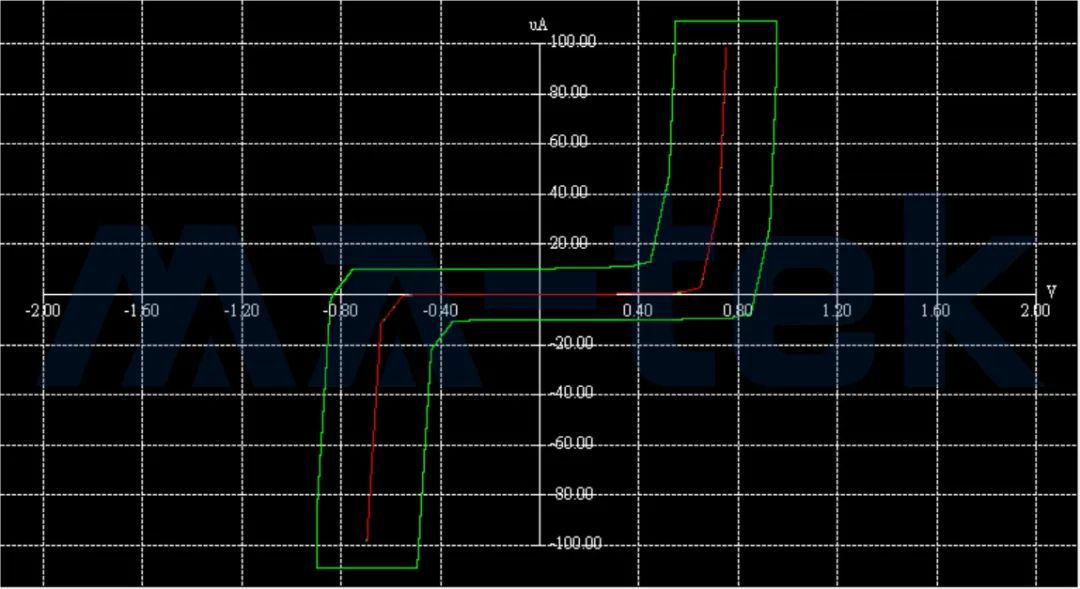

HBM 與CDM 依據規范是要測試完整的測試項,包含參數測試(Parametric Testing)和功能性測試(Functional Testing),如此才能逮到因ESD 損傷而造成的故障現象。在參數測試方面,在自動測試機臺(ATE)上即是測Open/Short(OS)、漏電和Power 端的靜態電流,但若以ESD 測試機臺來即時比較ESD 測試前后的差異的話,可以用兩種方式來量測,第一種是在電流等于1uA 時的電壓,若前后差異小于30% 的話,便能通過ESD 測試,如圖二所示;第二種是包絡線(Curve Compare Envelope) ,以ESD 測試之前的IV 曲線為參考,并以測試的最大電壓與電流的正負10% 為調整值,將此正負值加諸在測試前的IV Curve 即可得出一個區間范圍,只要測試后的IV 在此范圍便是通過ESD 驗證,如圖三所示。

圖二:Zap 前后的IV 變化,若1uA 下的電壓變化達30% 以上,判定此腳位ESD Fail

圖三:包絡線的示意圖,Zap 后的IV 曲線若超過綠線框選的范為,判定此腳位ESD Fail LU 的Pass 判斷標準是量測前的電流如果是INOM,則1.4xINOM 與INOM+10mA 取其最大值,小于此值即為驗證通過。

ESD 驗證失敗的解析與解決方案

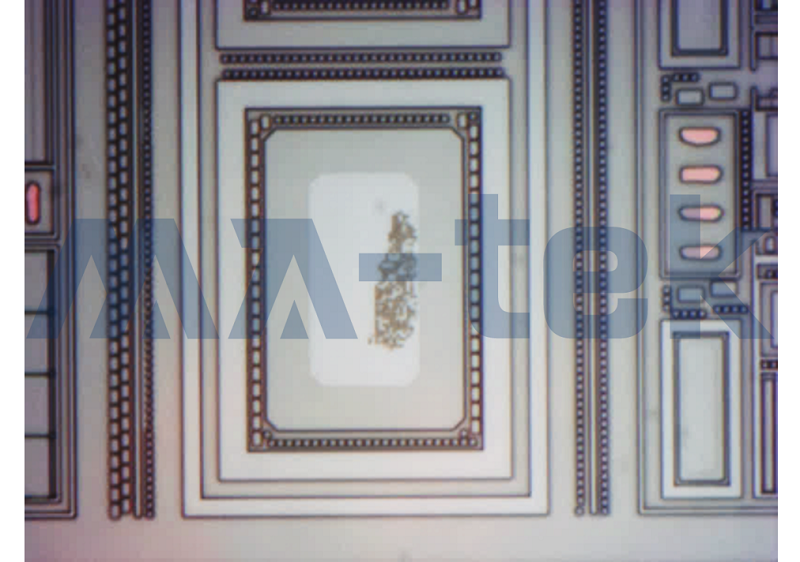

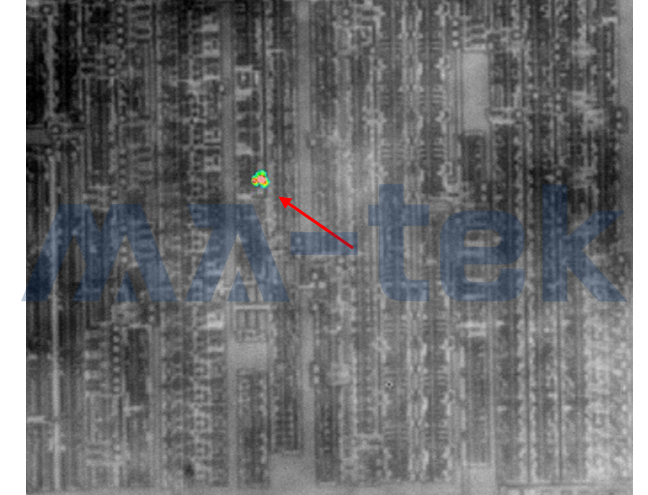

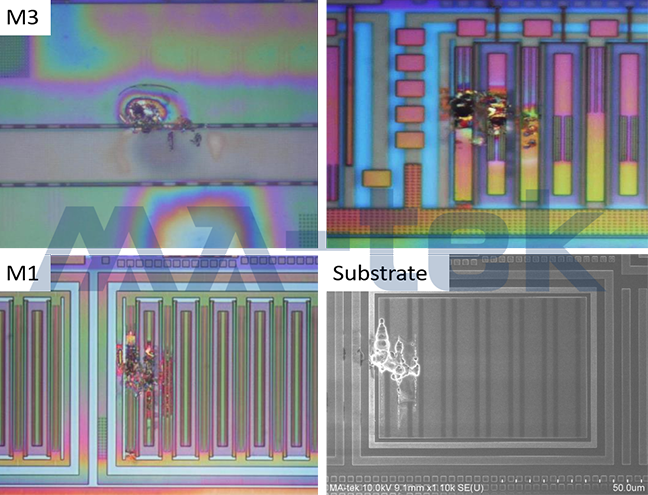

依ESD 失效原理與經驗,當靜電放電產生的過電流或過電壓超過元件的忍受能力時,就會產生元件燒毀的現象,元件燒毀的型態依放電路徑決定,如Junction 漏電、Gate Oxide Breakdown、 Drain 與Source 間的擊穿或兩個不同元件間的擊穿等等,元件燒毀嚴重者會往上向金屬層延伸。由于是元件燒毀,基本上很適合以Photon Emission Microscopy(PEM,俗稱EMMI)定位出燒毀位置,而OBIRCH 由于其檢測阻值變化的能力,若需進一步確認燒毀位置,也是可以考慮的定位工具。 靜電放電燒毀的位置依所發生的電路一般可分為兩類,ESD 電路(IO Cell)與內部電路。IO Cell 燒毀可以理解成ESD 電路發揮了導流的作用,避免靜電擊傷內部電路,但過電流超過了ESD 電路的忍受值而有燒毀的現象,這類的燒毀由于對應到參數測試有異常的Pin 腳,故尋找燒毀位置上相對來說是較簡單的。 依全晶面防護的理論,當靜電放電不循期望導通的IO Cell,而延著其它最快速最脆弱的路徑時,便有可能擊傷內部電路,此時便一定需要定位工具找出燒毀元件,才能了解放電路徑做進一步的設計防堵。 總結以上簡述,要確認燒毀元件或電路,有下述幾個選擇: 若是已知毀損電路在IO Cell,為了快速確認,可以執行全層次去除(Total Delayer)后,再以光學顯微鏡(OM)或掃描式電子顯微鏡(SEM)觀察,如圖四所示。 以亮點定位工具,EMMI 或OBIRCH 找出亮點位置所在的元件,在一些情況下,IC設計研發工程師能依據亮點對應的元件推導出ESD 失效模型,進而做出設計改良,如圖五所示。 承上,為驗證精確的失效機制,可以逐層將金屬層去除直到最底層的Contact/Poly/AA 露出,觀察燒毀的現象,甚至有時需以特別的樣品制備方式確認Gate Oxide Pinhole,特別是CDM 失效的實驗,如圖六所示。

圖四:ESD 擊傷內部電路的路徑

圖五:典型在IO Cell 的ESD 損傷

圖六:以晶背EMMI 偵測方式發現ESD 失效的亮點在邏輯電路上

圖七:逐層Delayer 觀察ESD 電路燒毀的情形 以上ESD 失效分析流程中很重要的目的是要確認放電路徑,在此要求下,建議以平面觀察(Plan View)的方式找出損傷的痕跡,如此才能建立靜電放電失效的模型,并提出“疏”和“堵”的對策,若是“疏”,就是設計其它的導通路徑,比如更多的Contact 來減少電流密度(Current Density),若是“堵”,可以設計限流的電阻以避免過多的電流造成燒毀的結果。

LU 驗證失敗的解析與解決方案

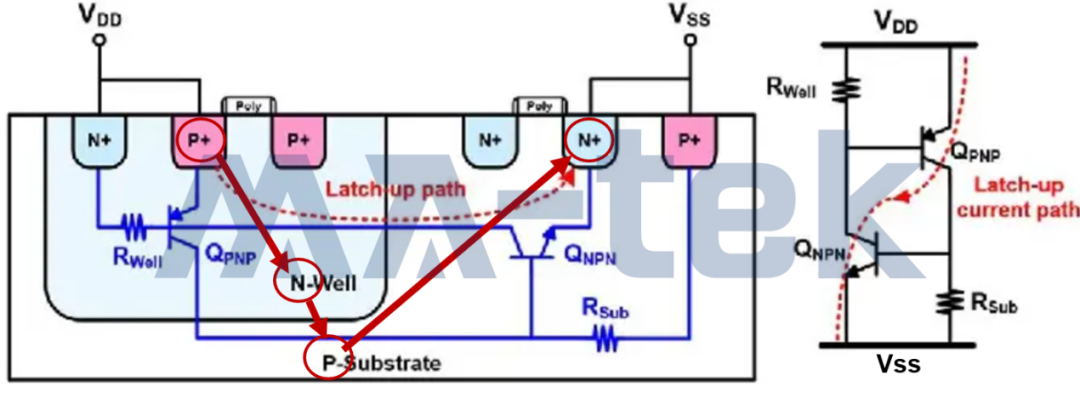

LU 的產生是因為外界的干擾信號觸發了寄生SCR 元件,產生了過大的電流造成功能性的問題,因此LU 解析的第一步就是確認寄生SCR 元件在哪里。當LU 發生時,過大的電流有可能造成芯片嚴重的燒毀,燒毀的位置雖可經由電性定位工具輕易地找出,但要注意的是燒毀的位置是大電流經過的路徑,并不一定是寄生SCR 元件所在,故碰到燒毀的現象反而不容易找到真因。 SCR 作動時,EMMI 可以偵測元件作動時發出的光,所以若LU 現象造成的大電流沒有損傷芯片,可以在設定觸發LU 的條件下執行EMMI 的定位,便可找出寄生SCR 元件的位置,進一步,在其相對應的Layout 位置上確認pnpn 的結構,將此結構繪出寄生SCR 結構圖,之后再從LU 產生的原理去理解是什么效應觸發了LU 現象,是某處的片狀電阻(Sheet Resistance)過高,亦或是某處節點有浮接(Floating)的情形等等,推理出失效模型后,LU 的問題即可迎刃而解,其道理可參考圖八。 圖八:CMOS 結構上需找出pnpn 的連續性結構,并對應到SCR 電路 在產品的研發階段,ESD 與LU 測試與分析是不可或缺的一環,依循本文的驗證流程,可以快速的解決認證方面的問題。

EETOP 官方微信

創芯大講堂 在線教育

半導體創芯網 快訊

相關文章