SRAM設計分析與優化

2023-10-28 16:58:46 EETOP

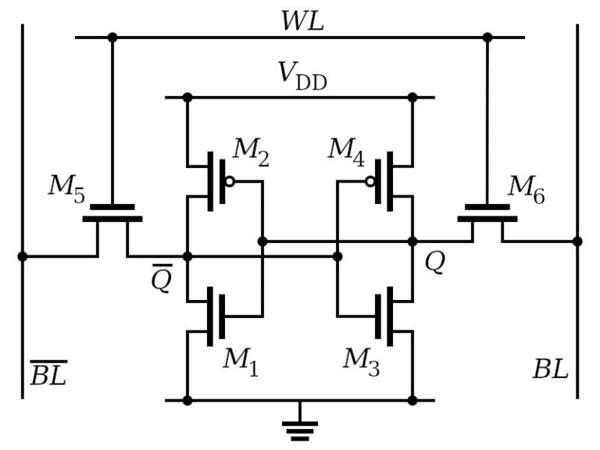

SRAM 位單元

在一個 SRAM 讀取周期中,字線 (WL) 進入激活狀態,然后將存儲的位值傳輸到位線 (BL),最后讀出放大器變為活動狀態以讀出差分位線。WL 和 BL 之間的延遲是讀取可編程自定時 (RPST) 的一部分,由電路設計人員進行調整。

SRAM 存儲器設計人員在優化電路設計和布局時需要應對多項挑戰:

軟錯誤率

隨著 Vdd 電源值的降低,SRAM 位單元最終會失效,這種失效可能發生在讀取周期、寫入周期,也可能僅僅是由于附近電路開關引起的噪聲。影響存儲器故障的因素包括內核和外圍布局的方式、工藝和局部變化、溫度、存儲器陣列大小以及良品率標準。

由于涉及多個模塊:位單元和外圍模塊,如感應放大器、多路復用器、自定時電路等,因此通過仿真預測良品率具有挑戰性。因此,SRAM 設計人員在參數良率仿真方面面臨著多重問題:

單個比特單元讀取周期的瞬態仿真工作量大,因為瞬態仿真必須高精度地包含大部分電路的布局寄生效應。

必須多次重復統計分析,以分析陣列大小、自定時宏設置、輔助和升壓電路的影響。

對提取的布局后全芯片網表中每個單元的讀取周期進行蠻力蒙特卡羅SPICE 仿真,可以計算出統計上正確的良率估計值,但仿真工作量太大,令人望而卻步。過去,可以使用 ML 代用模型來指導采樣,但這對于廣泛分析 SRAM 宏設置的影響而言,仿真工作量仍然過大。

英飛凌現在引入了一種新的兩步方法,通過使用最壞情況(worst-case )距離(WCD)來模擬其 SRAM 設計。

WCD 分析包括使用 WiCkeD 工具為一個 Vdd 和一個概率加 sigma 組合創建一個仿真集。在此過程中,確定讀取電流 (Iread) 的最壞情況值,然后確定最壞情況下的讀出放大器失諧。最后,針對每個可編程自定時(PST) 設置運行一次瞬態仿真,并使用 WCD 分析中的反標注最壞情況單元。

將分析分為兩個步驟的優點是,子塊的詳細統計分析是在仿真時間短的小網表中獨立完成的,而只需對整個電路進行少量緩慢的瞬態運行即可確定組合的最差是否-case 塊通過或失敗讀取周期取決于不同的高級宏設置 (RPST)。

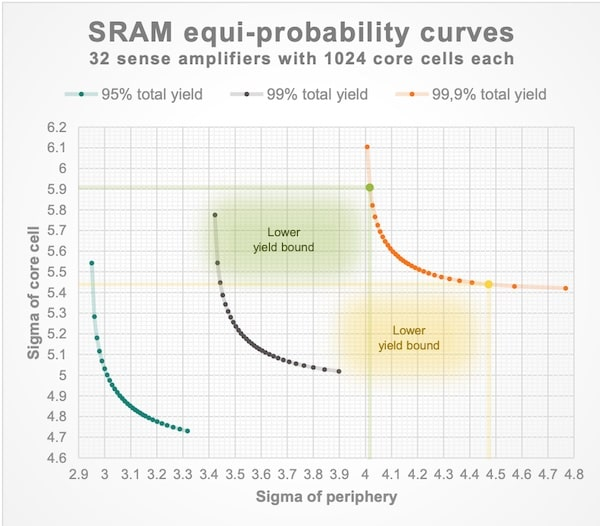

過去,最壞情況模塊的單一組合用于全芯片瞬態仿真,例如 6-sigma 最壞情況位單元與 4-sigma 最壞情況讀出放大器相結合。這對于驗證來說速度很快且足夠,但過于pessimism。在新方法中,測試了多種組合,等概率曲線上的每個單一滿足點都保證了最小的總產量,因此一個滿足點足以保證產量并接受電源電壓工作。

SRAM 等概率曲線

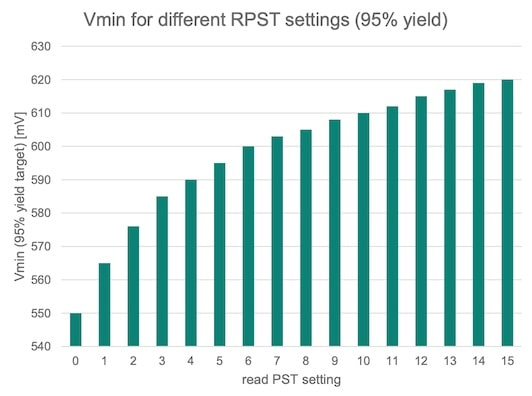

仿真結果生成以下圖,其中 Y 軸為 Vmin 值,X 軸為讀取的 PST 設置。

硅測量與仿真非常相關,其中讀取和寫入周期的 Vmin 值相差不到百分之二,正如預期的那樣,由于 IR 壓降等影響。

英飛凌的該團隊能夠通過使用 MunEDA WiCkeD 工具的兩步方法來模擬和優化 SRAM 設計的 Vmin 操作值:WCD 加瞬態模擬。Python 腳本用于自動化這些分析方法,該功能稱為 GangWay。通過腳本,他們能夠設置并轉移到新的內存架構,快速重現仿真結果并將驗證任務轉移給其他工程師。

EETOP編譯整理自semiwiki