臺積電分享更多關(guān)于2納米的技術(shù)細(xì)節(jié)

2023-06-02 11:10:03 EETOP臺積電在其 2023 年歐洲技術(shù)研討會上透露了有關(guān)其即將推出的N2 和 N2P 工藝技術(shù)的更多細(xì)節(jié)。這兩個生產(chǎn)節(jié)點的開發(fā)都考慮到了高性能計算(HPC),因此,它們具有許多專門設(shè)計用于改進(jìn)的增強功能表現(xiàn)。同時,鑒于大多數(shù)芯片旨在改進(jìn)的性能效率重點,低功耗應(yīng)用也將利用臺積電的N2 節(jié)點,因為與前代產(chǎn)品相比,它們自然會提高每瓦性能。

“N2 非常適合我們今天所處的節(jié)能計算范式,”負(fù)責(zé)代工廠高性能計算業(yè)務(wù)部門的臺積電業(yè)務(wù)發(fā)展總監(jiān)Yujun Li 在公司2023 年歐洲技術(shù)研討會上說。如圖所示,在整個電壓供應(yīng)范圍內(nèi),N2相對于 N3 的速度和功率優(yōu)勢非常一致,使其同時適用于低功率和高性能應(yīng)用。”

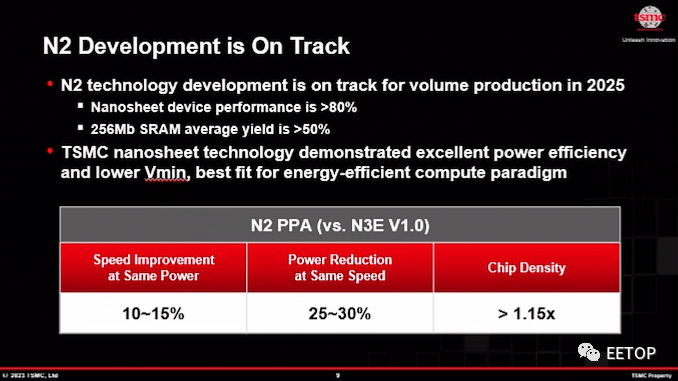

臺積電的N2制造節(jié)點--該晶圓廠的第一個使用納米片柵極環(huán)繞(GAAFET)晶體管的生產(chǎn)節(jié)點--承諾在相同的功率和復(fù)雜性下將晶體管性能提高10-15%,或者在相同的時鐘速度和晶體管數(shù)量下將功率使用降低25-30%。在提高晶體管性能方面,功率傳輸是基石之一,臺積電的N2和N2P制造工藝引入了幾個與互連有關(guān)的創(chuàng)新,以擠壓一些額外的性能。此外,N2P引入了背面電源軌,以優(yōu)化電源傳輸和芯片面積。

N2帶來的創(chuàng)新之一是超高性能金屬絕緣體-金屬(SHPMIM)電容器,以增強電源穩(wěn)定性并促進(jìn)片上去耦。臺積電表示,與幾年前為HPC推出的超高密度金屬-絕緣體-金屬(SHDMIM)電容器相比,新的SHPMIM電容器的容量密度提高了2倍以上(與上一代HDMIM相比,其電容提高了4倍)。與SHDMIM相比,新的SHPMIM還將Rs片狀電阻(歐姆/平方)降低了50%,而Rc通孔電阻也比SHDMIM降低了50%。

然而,減少電力輸送網(wǎng)絡(luò)中的電阻的另一種方法是重新構(gòu)建再分配層(RDL)。從其N2工藝技術(shù)開始,臺積電將使用銅RDL而不是今天的鋁RDL。銅RDL將提供類似的RDL間距,但將減少30%的薄層電阻,并將通孔電阻減少60%。

SHPMIM和銅RDL都是臺積電N2技術(shù)的一部分,預(yù)計將在2025年下半年用于大批量生產(chǎn)(HVM)。

去耦電源和I/O布線

使用背面電源輸送網(wǎng)絡(luò)(PDN)是N2P的另一項重大改進(jìn)。背面電源軌的一般優(yōu)勢是眾所周知的:通過將電源軌移到后面來分離I/O和電源布線,有可能使電源線變粗,從而減少線路后端(BEOL)的通孔電阻,這有望提高性能和降低功耗。此外,將I/O和電源線解耦可以縮小邏輯面積,這意味著成本降低。

在2023年技術(shù)研討會上,該公司透露,其N2P的背面PDN將通過減少紅外衰減和改善信號,使性能提高10%至12%,并使邏輯面積減少10%至15%。當(dāng)然,現(xiàn)在這樣的優(yōu)勢在高性能的CPU和GPU中會更加明顯,這些CPU和GPU擁有密集的電源傳輸網(wǎng)絡(luò),因此將其移到背面對它們來說是非常有意義的。

Backside PDN 是臺積電 N2P 制造技術(shù)的一部分,將于 2026 年底或 2027 年初進(jìn)入 HVM。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章