亞10納米節(jié)點(diǎn)的時(shí)鐘老化問(wèn)題

2022-10-28 11:47:15 EETOPEETOP編譯自semiwiki

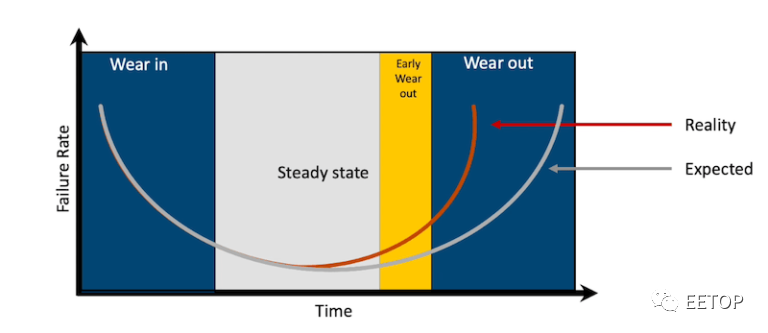

半導(dǎo)體芯片在發(fā)貨前都經(jīng)過(guò)測(cè)試,以排除早期故障,但是還有一些更微妙的可靠性影響,這些影響只會(huì)在較長(zhǎng)時(shí)間內(nèi)出現(xiàn),比如時(shí)鐘老化。甚至還有一個(gè)經(jīng)典圖表顯示了故障率隨時(shí)間變化的“浴缸曲線”:

IC故障率圖

如果磨損區(qū)域的現(xiàn)實(shí)和期望不一致,那么召回嵌入系統(tǒng)內(nèi)的芯片所帶來(lái)的財(cái)務(wù)影響可能要花費(fèi)數(shù)百萬(wàn)美元,甚至在安全關(guān)鍵應(yīng)用中要付出人命。

一個(gè) 7nm 的 SoC 可以有 100 億個(gè)晶體管,并且為了滿足功率規(guī)范,有許多時(shí)鐘域和多電壓電源域;導(dǎo)致老化問(wèn)題,如抖動(dòng)、占空比失真、插入延遲、設(shè)計(jì)余量減少和工藝變化增加。要預(yù)測(cè)晶體管老化的影響,需要了解電路拓?fù)洹㈤_(kāi)關(guān)活動(dòng)、電壓甚至溫度——這是一個(gè)復(fù)雜的目標(biāo)。

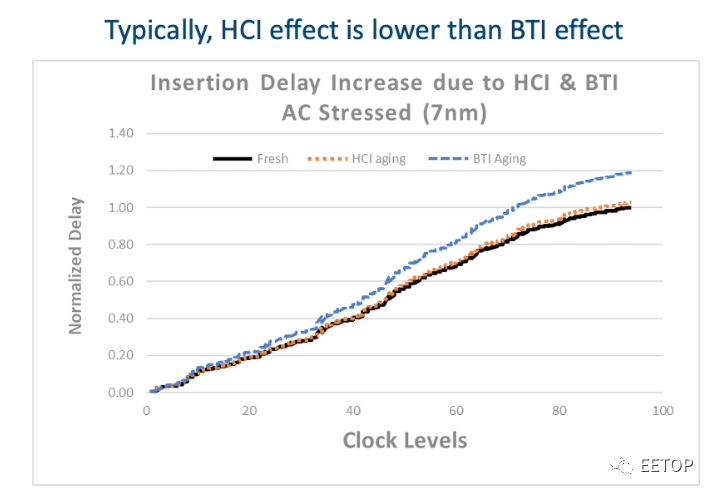

晶體管老化來(lái)自幾個(gè)影響:熱載流子注入 ( HCI )、負(fù)基極溫度不穩(wěn)定性 ( NBTI )、正基極溫度不穩(wěn)定性 ( PBTI )。較高的溫度會(huì)加速這些影響。占空比影響 BTI 效果,頻率對(duì) HCI 有成比例的影響。使用 HCI 時(shí),電荷會(huì)被困在晶體管的氧化層中,從而永久改變器件的 Vt。對(duì)于 7nm 節(jié)點(diǎn),BTI 效應(yīng)高于 HCI 效應(yīng),如下圖所示插入延遲,其中黑線是新電路,而 HCI 的老化效應(yīng)是橙色,BTI 效應(yīng)是藍(lán)色。

BTI 和 HCI 效應(yīng)

10nm 以上的 IC 設(shè)計(jì)方法使用靜態(tài)時(shí)序分析 (STA) 和一些時(shí)鐘的 SPICE 仿真,以及抖動(dòng)等參數(shù)的保護(hù)帶。老化可以應(yīng)用于所有設(shè)備,以提供有關(guān)電氣和時(shí)間影響的概念。

10nm 以下的設(shè)計(jì)需要對(duì)時(shí)鐘老化影響進(jìn)行更全面的分析,比如Infinisim 創(chuàng)建了一個(gè)名為ClockEdge的工具,可以有效地分析大型時(shí)鐘網(wǎng)絡(luò)。ClockEdge 工具會(huì)自動(dòng)創(chuàng)建一個(gè)晶體管級(jí)網(wǎng)表進(jìn)行分析,然后可以在一夜之間進(jìn)行仿真,向您展示最新的和老化的結(jié)果。

從現(xiàn)有文件創(chuàng)建一個(gè)新的時(shí)鐘域網(wǎng)表:Verilog、Lib、葉單元定義、約束、SPEF。以您的功能時(shí)鐘頻率為新鮮狀態(tài)生成具有完全 SPICE 精度的仿真結(jié)果。然后對(duì)時(shí)鐘進(jìn)行壓力分析,作為分析的第二步。第三步是使用老化的時(shí)鐘域網(wǎng)表,以功能時(shí)鐘頻率運(yùn)行完整的 SPICE 精確仿真,并評(píng)估占空比失真、插入延遲、軌到軌電平,甚至?xí)r鐘擺率。新鮮和陳年結(jié)果之間的差異告訴設(shè)計(jì)團(tuán)隊(duì)他們是否有可靠的設(shè)計(jì)。

深入研究第一步,新運(yùn)行分析從鎖相環(huán)的輸出,一直到觸發(fā)器或輸出墊的時(shí)鐘域。這個(gè)時(shí)鐘域可以非常大,包含數(shù)百萬(wàn)個(gè)器件,晶體管級(jí)分析結(jié)果向我們展示了延遲和壓擺值。

步驟1:全新運(yùn)行

通過(guò)使用分布式 SPICE 仿真方法,ClockEdge 工具可以在一夜之間對(duì)一個(gè)具有 450 萬(wàn)個(gè)門(mén)、5.17 億個(gè) MOSFET 和 32 億個(gè)器件的塊運(yùn)行時(shí)鐘分析。你的時(shí)鐘拓?fù)浣Y(jié)構(gòu)可以實(shí)現(xiàn)為樹(shù)狀、網(wǎng)格和刺狀。

步驟2:壓力運(yùn)行

特定的晶體管將被選中進(jìn)行老化,所有這些都取決于電路拓?fù)浣Y(jié)構(gòu)和時(shí)鐘是否被停頓(卡在VDD或VSS),或切換。壓力運(yùn)行也取決于溫度、電壓和每個(gè)使用模型的持續(xù)時(shí)間。

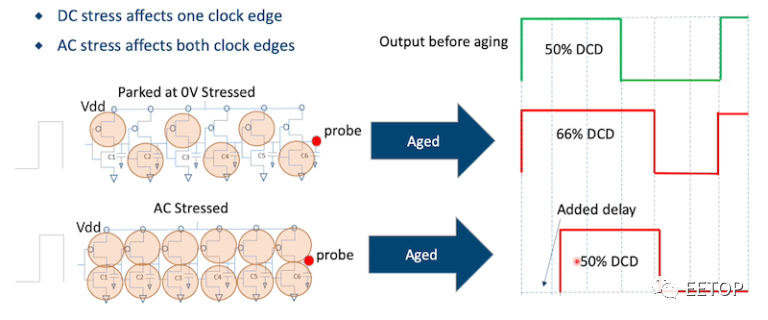

步驟3:老化模擬

使用老化的器件。對(duì)于有停頓時(shí)鐘值的器件,那么在老化分析過(guò)程中,只有時(shí)鐘的一個(gè)邊會(huì)受到影響,而有時(shí)鐘切換的器件在老化分析過(guò)程中,兩個(gè)邊都會(huì)受到影響。所以占空比延遲(DCD)的形狀將取決于你的電路拓?fù)浣Y(jié)構(gòu)。使用 ClockEdge,設(shè)計(jì)人員可以執(zhí)行假設(shè)壓力分析,比較時(shí)鐘停在 0、停在 1、切換甚至是停放和切換組合的影響。

總結(jié)

時(shí)鐘老化是一個(gè)新的可靠性問(wèn)題,特別是對(duì)于低于 10nm 工藝節(jié)點(diǎn)的 IC 設(shè)計(jì)。通過(guò)適當(dāng)?shù)姆治觯梢詼p輕老化的影響。文中提及的ClockEdge 工具可專注于為設(shè)計(jì)人員提供對(duì)其時(shí)鐘網(wǎng)絡(luò)的準(zhǔn)確老化分析,并在一夜之間快速提供結(jié)果。你可以看到你的老化時(shí)鐘域的直流和交流壓力條件。

原文

https://semiwiki.com/eda/319691-clock-aging-issues-at-sub-10nm-nodes/

關(guān)鍵詞: 納米 節(jié)點(diǎn) 時(shí)鐘 10納米

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章