指甲蓋大小塞了500億晶體管!IBM打造世界首款2納米芯片

2021-05-07 12:52:16 EETOP但這幾年來,盡管IBM退出了代工業務,不過好像IBM在半導體先進工藝研發上一直沒有放棄,時不時會傳出IBM推出領先世界一兩代的最先進的技術。

據IBM官網5月6日消息,IBM宣稱自己打造了世界首個2納米的芯片,大幅推進了當前芯片生產技術的前沿,在半導體設計及制程上取得突破。

在IBM Research的Albany工廠制造的2 nm晶圓的特寫,肉眼可見單個芯片

使用透射電子顯微鏡觀察到的2nm芯片,2nm小于人類DNA單鏈的寬度

IBM官網發布的2納米芯片宣傳片:

性能獲飛躍進展

在這里IBM的2nm制程號稱在150mm²(指甲蓋大小)的面積中塞入了500億個晶體管,平均每平方毫米為3.3億個。做為對比,臺積電和三星的7nm制程大約在每平方毫米是9,000萬個晶體管左右,三星的5LPE為1.3億個晶體管,而臺積電的5nm則是1.7億個晶體管。

據IBM 的說法,其2nm 架構可以在與現有的7nm 相同的性能下,僅是7納米的1/4的功耗,也就是說放到現代手機中的話,可能四天才需要充一次電。又或者,它也能在與現有的7nm 相同的能耗下,增加45%的性能,在筆電、自駕車等較不在意功耗的場景下,可能帶來更高的運算力。其他包括資料中心、太空探索、人工智能、5G、6G,乃至于量子運算都可能在受惠之列。

2納米的研發路線及技術細節

據悉,目前擔任IBM混合云研究副總裁的Mukesh Khare帶領其完成了2納米技術的突破。

資料顯示,Khare在1999年到2003年間,從事90納米SOI工藝的開發,該工藝將Power4和Power4+推向市場,他隨后又負責了65納米和45納米SOI的推進,這些技術被Power5和Power6采用;之后他對對用于Power7的32納米技術進行了研究,然后研究了在Power8上使用的22納米工藝中使用的高k /金屬柵極技術。然后Khare繼續擔任奧爾巴尼納米技術中心的半導體研究總監,

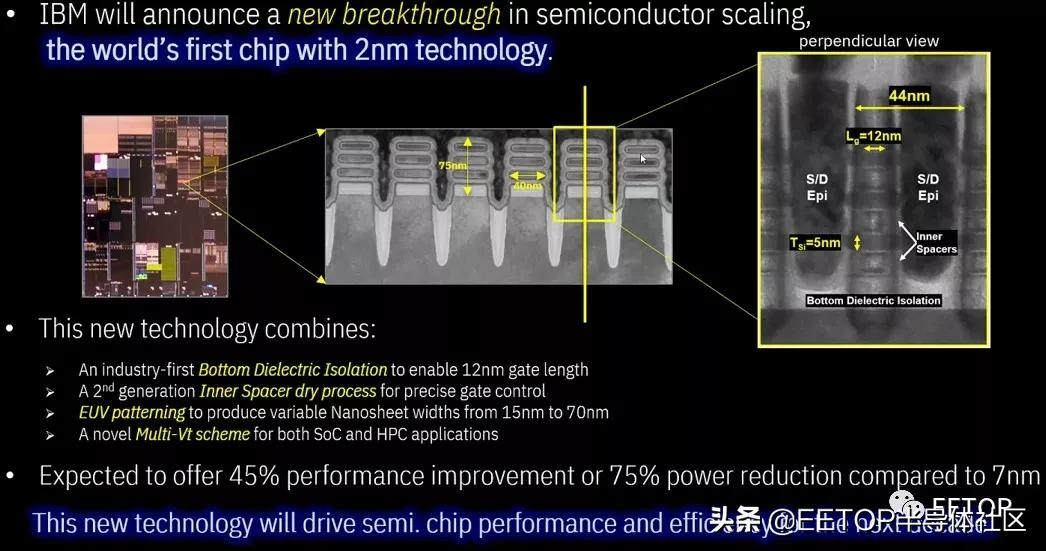

如下圖所示,這是IBM掌握的2納米芯片制造技術的要點。里面有很多東西,讓我們把它拆開一點。

首先,在這個芯片上,IBM用上了一個被稱為納米片堆疊的晶體管,它將NMOS晶體管堆疊在PMOS晶體管的頂部,而不是讓它們并排放置以獲取電壓信號并將位從1翻轉為零或從0翻轉為1。這些晶體管有時也稱為gate all around或GAA晶體管,這是當前在各大晶圓廠被廣泛采用的3D晶體管技術FinFET的接班人。從以往的介紹我們可以看到,FinFET晶體管將晶體管的源極和漏極通道拉入柵極,而納米片將多個源極和漏極通道嵌入單個柵極以提高密度。

IBM表示,其采用2納米工藝制造的測試芯片可以在一塊指甲大小的芯片中容納500億個晶體管。

在IBM的這個實現方案下,納米片有三層,每片的寬度為40納米,高度為5納米。如果您在上表的右側看,那是一張納米片的側視圖,顯示出它的側視圖,其間距為44納米,柵極長度為12納米,Khare認為這是其他大多數晶圓代工廠在2納米工藝所使用的尺寸。

2納米芯片的制造還包括首次使用所謂的底部電介質隔離(bottom dielectric isolation),它可以減少電流泄漏,因此有助于減少芯片上的功耗。在上圖中,那是淺灰色的條,位于中部橫截面中的三個堆疊的晶體管板的下面。

IBM為2納米工藝創建的另一項新技術稱為內部空間干燥工藝(inner space dry process),從表面上看,這聽起來不舒服,但實際上這個技術使IBM能夠進行精確的門控制。

在實施過程中,IBM還廣泛地使用EUV技術,并包括在芯片過程的前端進行EUV圖案化,而不僅是在中間和后端,后者目前已被廣泛應用于7納米工藝。重要的是,IBM這個芯片上的所有關鍵功能都將使用EUV光刻技術進行蝕刻,IBM也已經弄清楚了如何使用單次曝光EUV來減少用于蝕刻芯片的光學掩模的數量。

這樣的改善帶來的最終結果是,制造2納米芯片所需的步驟要比7納米芯片少得多,這將促進整個晶圓廠的發展,并可能也降低某些成品晶圓的成本。這是我們能看到的。

最后,2納米晶體管的閾值電壓(上表中的Vt)可以根據需要增大和減小,例如,用于手持設備的電壓較低,而用于百億超級計算機的CPU的電壓較高。

IBM并未透露這種2納米技術是否會采用硅鍺通道,但是顯然有可能。

能否量產是關鍵

當然,公布制程試制成功,和能量產依然是兩碼事,IBM自己2015年就宣布試制7nm制程成功,但一直到去年八月才有第一個商用化產品出現。因此IBM這里宣示的意味是比較濃厚,何時能有產品推出又是另一回事了。

目前量產的制程技術中,領先的是臺積電的5nm,由蘋果的M1、A14芯片及華為的Kirin 9000所用,次之為三星的5LPE,用在Snapdragon 888芯片上,再來就是兩間公司應用廣泛的7nm制程技術了。自然,所有人也都努力向著更高密度的芯片推進中,其中臺積電的4nm與3nm預計明年量產,而2nm也已經取得了關鍵性的突破,離IBM并不遠。反倒是Intel的7nm制程芯片(Intel的制程技術晶體管密度較高,因此約略介于臺積電的5nm與4nm之間)要等到2023年才投產,還是慢了一步了。