臺積電介紹12-Hi 3D堆疊工藝 欲將SoIC推向新的極限

2020-08-26 10:00:11 cnBeta.COM

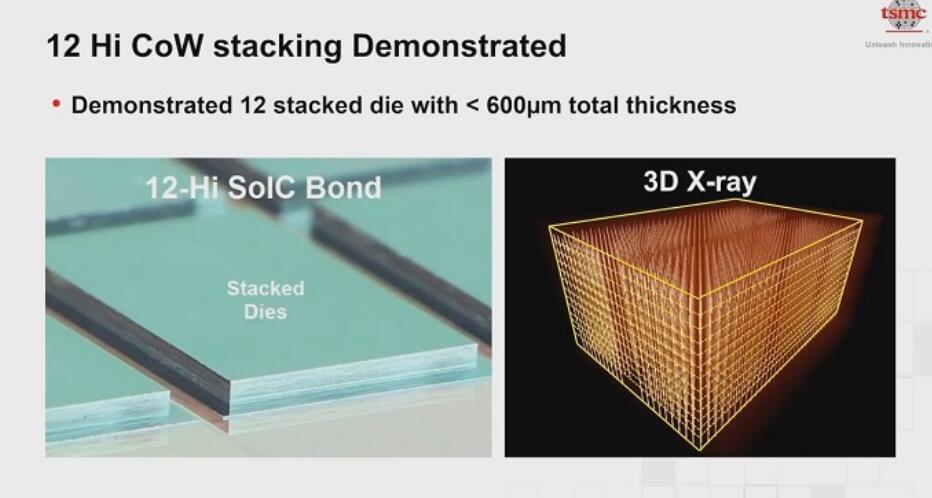

資料圖(來自:TSMC)

由臺積電分享的一張幻燈片可知,這項關鍵技術的復雜度,遠超以往的硅中介層或芯片堆疊工藝。因其允許在不使用任何 μ-bumps 凸點的情況下堆疊硅芯片,而是直接將金屬層彼此對準并鍵合到硅片上。

目前臺積電正在積極探索12-Hi 配置的 SoIC 方案,每個管芯都有一系列的硅通孔(TSV),以便每層與其它層進行通信。其設計理念是每層都可具有不同的邏輯元素,比如 IO 或 SRAM 。

此外某層也可以是無源的,以充當其它有源層之間的隔熱層。如 PPT 所示,這種設計的最大厚度為 600 μm,意味著單層厚度要控制在 50 μm 以下,而傳統標準管芯堆疊解決方案上的凸點間距也是 50 μm 左右。

至于 SoIC,N7 / N6 工藝下的混合鍵合間距為 9 μm,N5 工藝更是可以縮減到 6 μm 。這表明臺積電擁有一些令人印象深刻的線性制造和晶圓減薄技術,以實現如此高水平的管芯對準與一致性。

該公司甚至展望了將之進一步縮減到 0.9 μm 的能力,以使之擴展至硅芯片的后端互連。至于最終的制造難度和客戶的接納程度,仍有待時間去檢驗。