聯電推出全新22納米

2019-12-14 13:32:24 EETOP

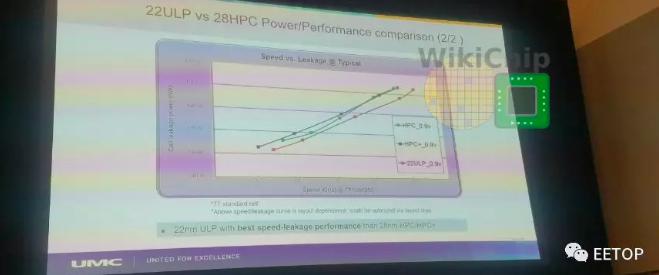

盡管聯電在其現有的28nm和最近的14nm工藝之間插入了新節點,但該節點本身更接近28nm。它仍然是平面CMOS工藝,但在28nm工藝上可減少約10-15%的面積。相比之下,聯電的14納米工藝提供了2倍的密度。UMC的22ULP(超低功耗)變體提供了設計規則兼容性,并且掩模數量與其28納米工藝相同。該公司還提供22ULL(超低泄漏)型號。與28HPC相比,22ULP在等功率情況下可提供高達20%的性能提升,在等性能情況下可提供高達35%的更低功耗。聯電還提供許多特殊設備,包括高VT和高壓設備。

聯電22納米有兩條遷移路徑。第一個是低成本的物聯網應用,可以從芯片面積縮小中受益,但仍無法承受FinFET設計帶來的成本。UMC表示:“我們看到,28納米芯片的設計將以更低的成本升級到22納米,因此我們認為它可以用于互連芯片、一些入門級智能手機和高端電視控制器。” UMC還與Arm合作在新的22nm平臺上提供POP IP。為此,Arm為Cortex-M以及包括A55在內的一些Cortex-A核心提供POP IP。

第二種遷移途徑是針對來自40納米的設計,它們希望利用低功耗工藝。與聯電現有的40ULP工藝相比,根據設計,聯電報告的性能提高了35%至95%,或者功率提高了0.55至1.2倍。

聯華電子表示,其22納米工藝可用于今天的代工客戶。聯電也正在為此過程開發eMRAM,但是尚未宣布推出計劃。