在FPGA設計中如何充分利用NoC資源去支撐創新應用設計

2020-08-21 15:26:01 Achronix為了解決這一問題,Achronix 在其最新基于臺積電(TSMC)7nm FinFET工藝的Speedster7t FPGA器件中包含了革命性的創新型二維片上網絡(2D NoC)。這種2D NoC如同在FPGA可編程邏輯結構之上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數據傳輸提供了大約高達27Tbps的超高帶寬。

作為Speedster7t FPGA器件中的重要創新之一,2D NoC為FPGA設計提供了幾項重要優勢,包括:

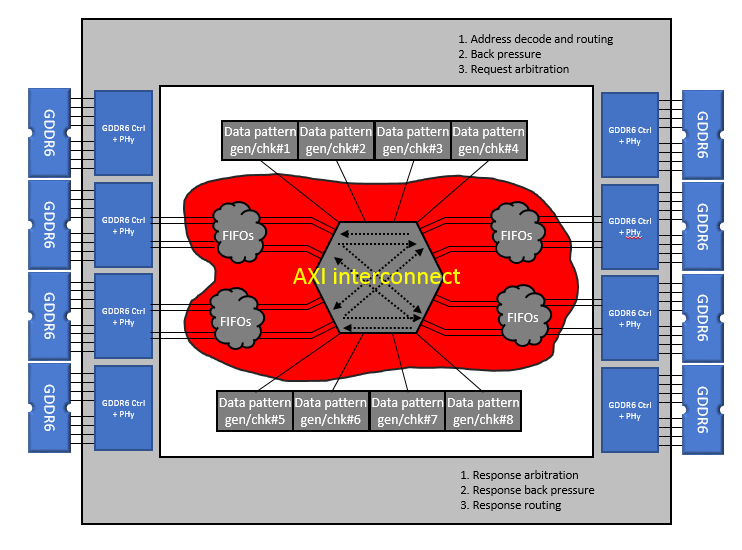

本文用了一個具體的FPGA設計案例,來體現上面提到的NoC在FPGA設計中的幾項重要作用。這個設計的主要目的是展示FPGA內部的邏輯如何去訪問片外的存儲器。如圖1所示,本設計包含8個讀寫模塊,這8個讀寫模塊需要訪問8個GDDR6通道,這樣就需要一個8x8的AXI interconnect模塊,同時需要有跨時鐘域的邏輯去將每個GDDR6用戶接口時鐘轉換到邏輯主時鐘。除了圖1中的8個讀寫模塊外,紅色區域的邏輯都需要用FPGA的可編程邏輯去實現。

圖1 傳統FPGA實現架構

對于AXI interconnect模塊,我們采用Github上開源的AXI4總線連接器來實現,這個AXI4總線連接器將4個AXI4總線主設備連接到8個AXI4總線從設備,源代碼可以在參考文獻2的鏈接中下載。我們在這個代碼的基礎上進行擴展,增加到8個AXI4總線主設備連接到8個AXI4總線從設備,同時加上了跨時鐘域邏輯。

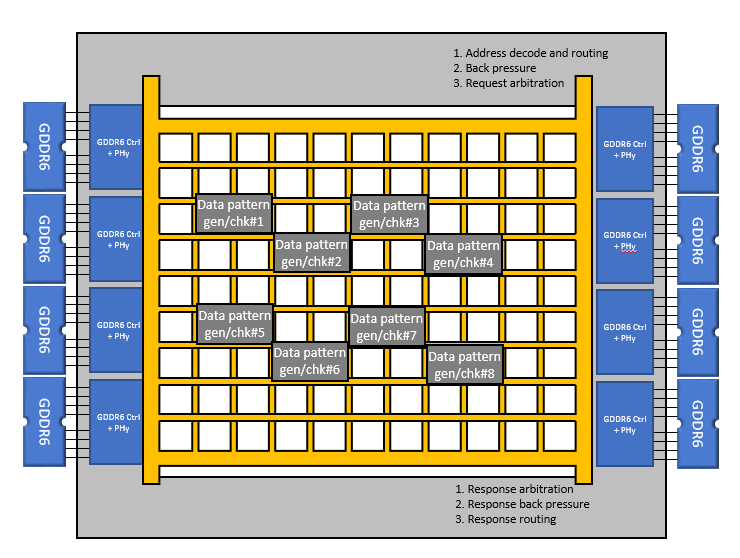

為了進行對比,我們用另外一個設計,目的還是用這8個讀寫模塊去訪問8個GDDR6通道;不同的是,這次我們將8個讀寫模塊連接到Achronix的Speedster7t FPGA器件的2D NoC上,然后通過2D NoC去訪問8個GDDR6通道。如圖2所示:

圖2 Speedster7t 1500的實現架構

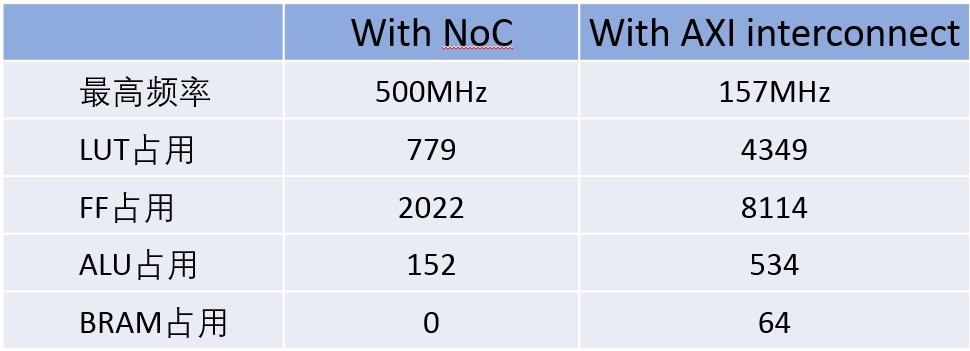

首先,我們從資源和性能上做一個對比,如圖3所示:

圖3 資源占用和性能對比

從資源占用上看,用AXI總線連接器的設計會比用2D NoC的設計占用多出很多的資源,以實現AXI interconnect還有跨時鐘域的邏輯。這里還要說明一點,這個開源的AXI interconnect實現的是一種最簡單的總線連接器,并不支持2D NoC所能提供的所有功能,比如地址表映射,優先級配置。

最重要的一點是AXI interconnect只支持阻塞訪問(blocking),不支持非阻塞訪問(non-blocking)。阻塞訪問是指發起讀或者寫請求以后,要等到本次讀或者寫操作完成以后,才能發起下一次的讀或者寫請求。而非阻塞訪問是指可以連續發起讀或者寫請求,而不用等待上次的讀或者寫操作完成。在提高GDDR6的訪問效率上面,阻塞訪問會讓讀寫效率大大下降。

如果用FPGA的可編程邏輯去實現完整的2D NoC功能,包括64個接入點、128bit位寬和400MHz的速率,大概需要850 k LE,等效于占用了Speedster7t 1500 FPGA器件56%的可編程資源。而2D NoC則可以提供 80個接入點、256bit位寬和2GHz速率,而且不占用FPGA可編程邏輯。

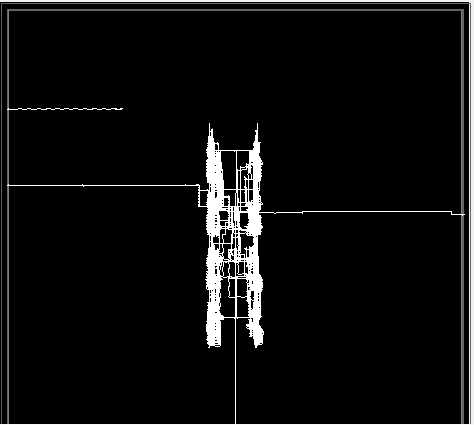

從性能上來看,使用AXI總線連接器的設計只能跑到157MHz,而使用NoC的設計則能跑到500MHz。如果我們看一下設計后端的布局布線圖,就會有更深刻的認識。圖4所示的是使用AXI總線連接器的設計后端布局布線圖。

圖4 使用AXI interconnect的設計后端布局布線圖

從圖中可以看到,因為GDDR6控制器分布在器件的兩側(圖中彩色高亮的部分),所以AXI總線連接器的布局基本分布在器件的中間,既不能靠近左邊,也不能靠近右邊,所以這樣就導致了性能上不去。如果增加pipeline的寄存器可以提高系統的性能,但是這樣會占用大量的寄存器資源,同時會給GDDR的訪問帶來很大的延時。

如果再看一下圖5中使用了2D NoC的布局布線圖,就會有很明顯的對比。首先,因為用2D NoC實現了AXI總線連接器和跨時鐘域的模塊,這就節省了大量的資源;另外,因為2D NoC遍布在整個器件上,一共有80個接入點,所以8個讀寫模塊可以由工具放置在器件的任何地方,而不影響設計的性能。

圖5 使用2D NoC設計的后端布局布線圖

從本設計的整個流程來看,使用2D NoC會極大的簡化設計,提高性能,同時節省大量的資源;FPGA設計工程師可以花更多的精力在核心模塊或者算法模塊設計上面,把總線傳輸、外部接口訪問仲裁和接口異步時鐘域的轉換等工作全部交給2D NoC吧。

EETOP 官方微信

創芯大講堂 在線教育

半導體創芯網 快訊

相關文章