歐洲本土超級(jí)計(jì)算硬件邁出第一步!高性能計(jì)算RISC-V完成流片,樣品測(cè)試"Hello World "成功顯示!

2021-09-23 13:03:49 EETOP最新消息,專為高效率和高吞吐量計(jì)算設(shè)計(jì)的被稱為歐洲處理器加速器(EPAC)芯片已成功流片,并正在EPI的實(shí)驗(yàn)室進(jìn)行測(cè)試。EPI認(rèn)為這標(biāo)志著向本土超級(jí)計(jì)算硬件邁出的第一步。

歐洲處理器計(jì)劃最初是一個(gè)由來自 10 個(gè)歐洲國家的 28 個(gè)合作伙伴組成的項(xiàng)目,旨在為歐盟配備定制處理器和技術(shù),使歐盟成為專注于科學(xué)和創(chuàng)新的技術(shù)獨(dú)立力量。為實(shí)現(xiàn)這一目標(biāo),該項(xiàng)目旨在構(gòu)建一個(gè)完全定制的 HPC 系統(tǒng),從定制處理器開始。正如該項(xiàng)目所指出的:“EPI 活動(dòng)的一個(gè)關(guān)鍵部分是基于 RISC-V 指令集架構(gòu)開發(fā)和展示完全由歐洲開發(fā)的處理器 IP,提供名為 EPAC(歐洲處理器加速器)的高能效和高吞吐量加速器內(nèi)核.”

今天,隨著第一批芯片在EPI的實(shí)驗(yàn)室中測(cè)試,該項(xiàng)目已經(jīng)兌現(xiàn)了承諾。RISC-V 處理器是包含多個(gè)專用加速器的設(shè)計(jì),所有加速器都以 RSIC-V ISA 及其設(shè)計(jì)原則為中心。該處理器包含四塊矢量處理單元(VPU),由 SemiDynamics 設(shè)計(jì)的 Avispado RISC-V 內(nèi)核和巴塞羅那超級(jí)計(jì)算中心和薩格勒布大學(xué)設(shè)計(jì)的矢量處理單元組成。在每個(gè)tile中,都有用于緩存系統(tǒng)的主節(jié)點(diǎn)和 L2 緩存,這是 Chalmers 和 FORTH 的貢獻(xiàn)。對(duì)于額外的加速,有由Fraunhofer IIS、ITWM 和 ETH Zürich 設(shè)計(jì)的 Stencil 和 Tensor 加速器 (STX),以及由 CEA LIST 設(shè)計(jì)的精度可調(diào)處理器 (VRP)。

為了保持所有這些組件之間的連接,EXTOLL開發(fā)了一個(gè)高速的片上網(wǎng)絡(luò)(NoC)路由器和SERDES。到目前為止還不知道其他的芯片外連接,但是,我們假設(shè)將利用DDR5和PCIe Gen4或Gen5 I/O。

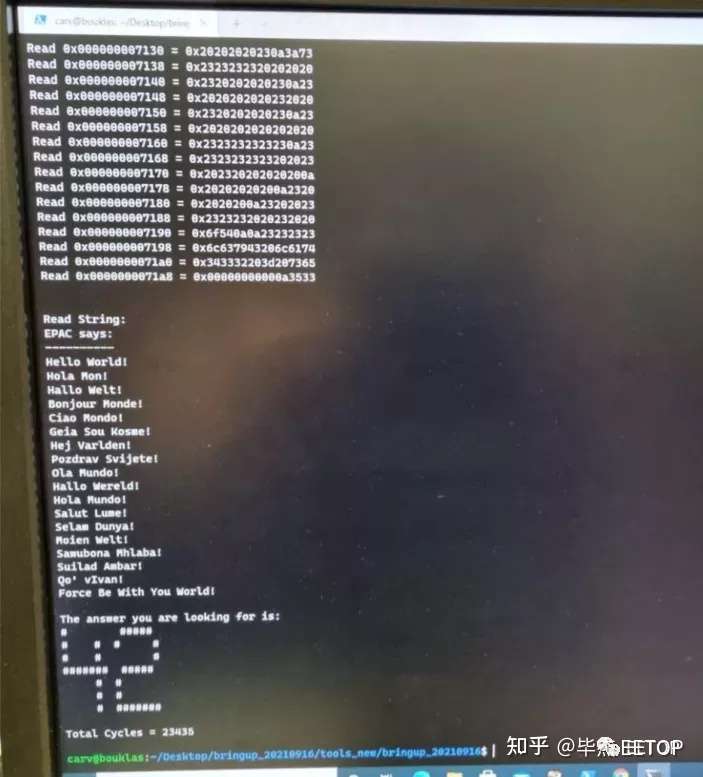

該芯片已經(jīng)在GlobalFoundries 22納米FDX低功耗半導(dǎo)體節(jié)點(diǎn)上成功流片,裸片尺寸為26.97平方毫米。測(cè)試封裝是FCBGA類型,有22 x 22個(gè)焊球的網(wǎng)格陣列,該芯片的目標(biāo)頻率為1GHz。在下面的圖片中,你可以看到經(jīng)典的"Hello World "測(cè)試正在新平臺(tái)上進(jìn)行。

該芯片的近期前景是不斷改進(jìn),與其他仍需設(shè)計(jì)的 HPC IP 一起,一旦一切準(zhǔn)備就緒,EPI 計(jì)劃將其整合到一個(gè)強(qiáng)大的 HPC 系統(tǒng)中,用于各種工作負(fù)載。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章