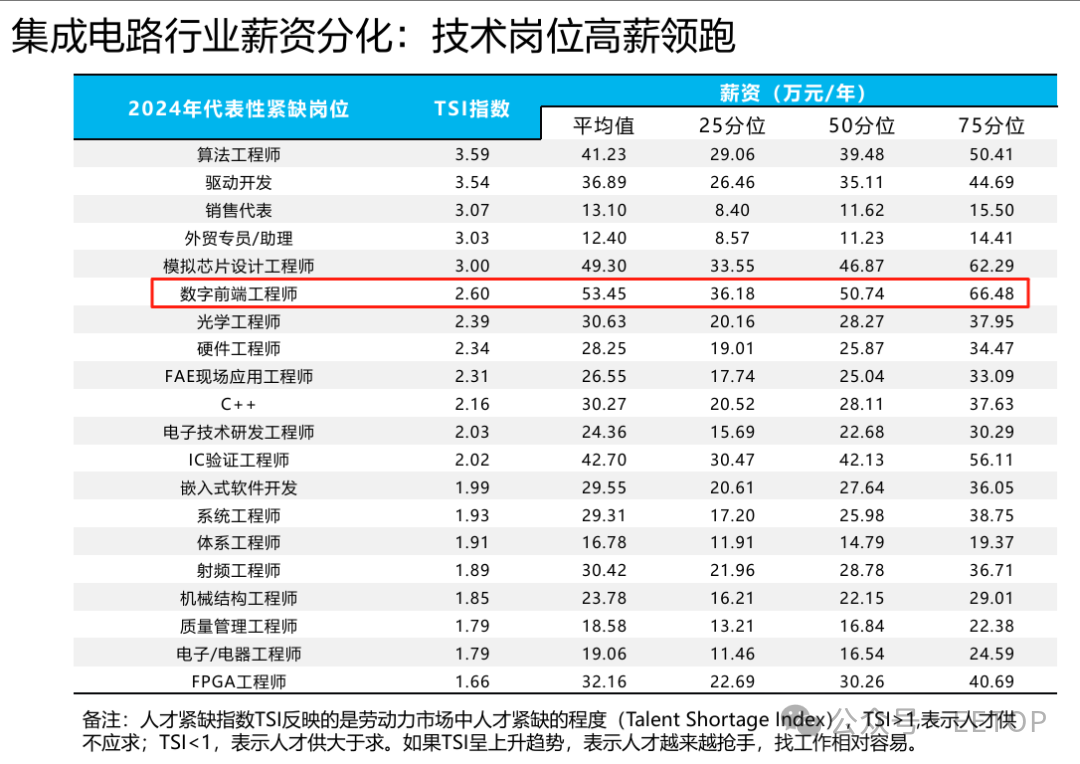

人均年薪53萬!芯片行業哪個崗位工資最多?

2025-07-28 08:33:54 EETOP芯片最賺錢的崗位居然是數字前端的設計驗證工程師,真是不可思議!人均年薪高達53.45萬元!

以下數據來自獵聘網的調研報告。

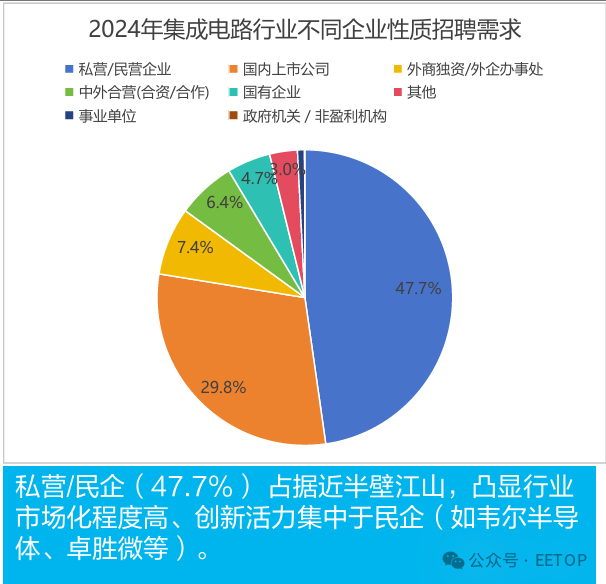

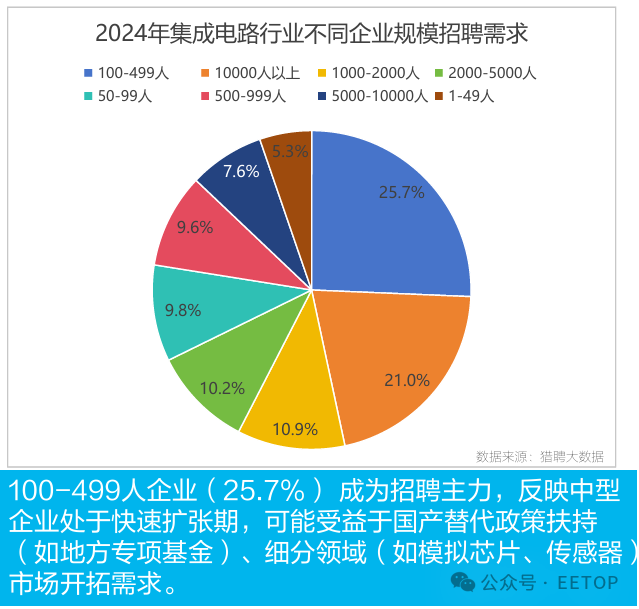

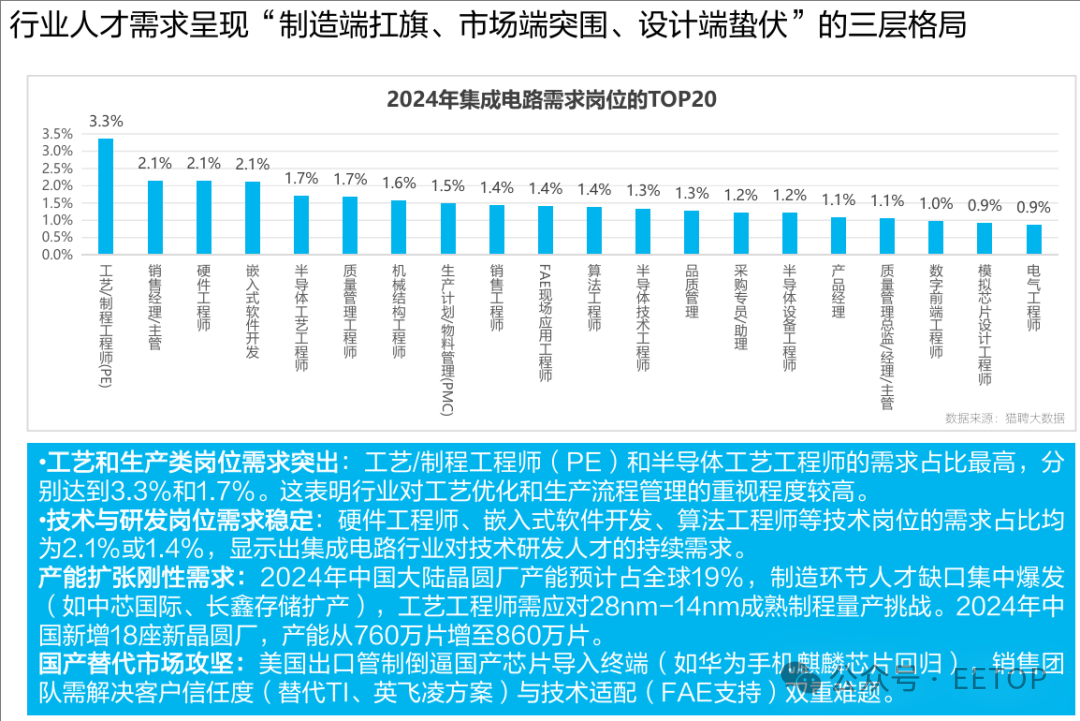

在集成電路行業,那到底哪個類型的企業招聘需求更多呢?私企還是國企?大企業還是小企業呢?

芯片設計方向:技術與工具的深度耦合

1. 數字IC設計

核心技能技能其實主要就以下幾個方面:

(前端)精通Verilog/VHDL硬件描述語言,掌握SystemVerilog驗證方法學

(后端)熟悉數字前端全流程(RTL→綜合→形式驗證→時序分析),熟練使用DC、Formality、PrimeTime工具

(前端以及架構)深入理解處理器架構(如RISC-V、ARM Cortex)和總線協議(AXI/APB/OCP)

(設計、后端、系統等)掌握UPF低功耗設計流程,在40nm以下工藝實現時鐘門控、電源隔離

比如要設計28nm移動處理器時,需使用ARM或者RISCV或者X86等CPU核的IP,當然自己開發也可以,再通過熟悉接口做好各類外設的接口控制邏輯,就是第一個技能,熟練掌握Verilog等語言,然后就是驗證相關的,到中后端,使用DC工具完成綜合,使用Innovus或者ICC2等EDA工具完成布局布線等,控制插入延遲偏差<30ps,并采用多重電壓域設計降低動態功耗23%等,所以工具與技能都要熟練掌握。

2. 模擬/混合信號IC設計

掌握關鍵技能點能力如下:

器件知識:晶體管級電路設計能力(CMOS、Bipolar、FinFET器件物理特性掌握)

各種參數控制:高頻電路參數控制技巧(例如LDO的PSRR>80dB@1MHz)

復雜模擬電路模塊開發經驗:(PLL時鐘抖動<100fs,ADC實現ENOB>14bit等)

熟練操作Spectre、HSPICE仿真工具,具備Monte Carlo分析能力

制造工藝方向:精度與穩定性的平衡藝術

1. 半導體工藝開發

基本的一些技術要求:

精通光刻工藝(DUV到EUV光刻機臺操作,套刻誤差控制<2nm)

掌握薄膜沉積技術(ALD制備高k介質時厚度波動<1?)

等離子體刻蝕工藝優化能力(深寬比50:1的TSV刻蝕均勻性管控)

良率提升方法論(SPC控制Cpk>1.67,解決defect密度<0.05/cm2)

比如工藝相關的項目可以是:在3D NAND制造中,工程師需建立96層堆疊的階梯刻蝕工藝,通過脈沖式刻蝕與原子層沉積交替,將層間厚度偏差控制在±1.5%以內。

2. 器件整合工程

必備基本能力:

FinFET/GAA納米片結構的TCAD模擬能力

應力工程技術(SiGe源漏應變提升電子遷移率30%)

可靠性驗證技能(HCI壽命預測模型誤差<10%)

掌握TEM/FIB等微觀分析設備操作

比如如下的項目:隨著環柵晶體管(GAA)量產,工程師需要建立原子層摻雜(ALD doping)工藝,在1nm節點實現閾值電壓±20mV波動控制。

封裝測試方向:系統級集成的技術突破

1. 先進封裝技術

核心能力:

2.5D/3D封裝設計能力(硅中介層布線密度>10k/mm2)

微凸點工藝開發(5μm直徑銅柱共晶焊接技術)

熱應力仿真優化(通過ANSYS Icepak實現芯片結溫<125℃)

掌握TSV深孔填充工藝(高深寬比50:1的銅電鍍技術)

比如以下項目:在Chiplet異構集成中,工程師需解決不同工藝節點芯片的熱膨脹系數匹配,采用有機中介層將CTE差異控制在1ppm/K以內。

2. 測試工程開發

基本技能要點:

- ATE測試程序開發(Teradyne UltraFLEX平臺腳本編寫)

- 高速接口測試技術(PCIe 5.0眼圖模板達標率>99.7%)

- 大數據分析能力(通過1E6個測試數據點建立多維良率預測模型)

比如以下項目:5G基帶芯片測試需開發毫米波OTA測試系統,在28GHz頻段實現±0.5dB功率測量精度,同時將測試時間壓縮至傳統方案的30%。

EDA與IP開發方向:產業鏈的賦能基石

1. EDA工具開發

基本核心技術:

- 數學建模能力(發展時序簽核的統計靜態時序分析算法)

- 并行計算優化(實現布局布線工具的多核加速比>32x)

- 機器學習應用(利用GAN網絡生成布線模式庫)

- 物理驗證引擎開發(DRC規則檢查速度突破1M layers/hour)

典型項目案例:開發7nm以下工藝的簽核工具時,需建立新型漏電模型,將電流密度計算誤差從傳統BSIM模型的15%降至3%以內。

2. IP核開發

主要基本能力:

- 標準接口協議實現(DDR5 PHY滿足6400Mbps速率)

- 工藝移植能力(28nm到12nm的IP移植性能提升驗證)

- 安全防護技術(PUF物理不可克隆函數實現>98%唯一性)

- 低功耗設計技巧(物聯網IP靜態功耗<10nW/MHz)

EETOP 創芯大講堂 數字IC前端設計課程推薦