英偉達聯手SK海力士,嘗試將 HBM 內存 3D 堆疊到 GPU 核心上

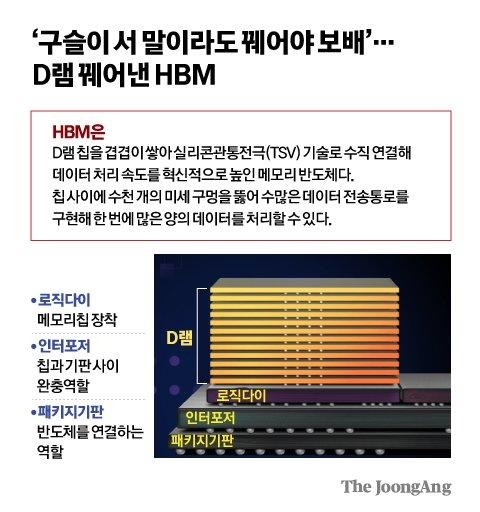

2023-11-20 08:04:54 IT之家11 月 20 日消息,據 Joongang.co.kr 報道,SK 海力士已經開始招聘邏輯半導體(如 CPU 和 GPU)設計人員,希望將 HBM4 通過 3D 堆疊的方式直接集成在芯片上。

據報道,SK 海力士正在與幾家半導體公司討論其 HBM4 集成設計方法,包括 Nvidia。

外媒認為,Nvidia 和 SK 海力士很可能會共同設計這種集成芯片,并借助臺積電進行代工,然后通過臺積電的晶圓鍵合技術將 SK 海力士的 HBM4 芯片堆疊到邏輯芯片上。而為了實現內存芯片和邏輯芯片的一體協同,聯合設計是不可避免的。

如果 SK 海力士能夠成功,這可能會在很大程度上改變行業的運作方式,因為這不僅會改變邏輯和存儲新芯片的互連方式,還會改變它們的制造方式。

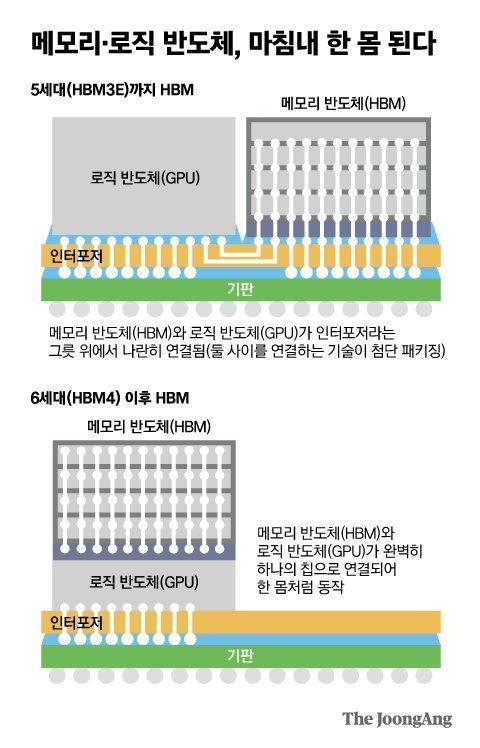

現階段,HBM 堆疊主要是放置在 CPU 或 GPU 旁邊的中介層上,并使用 1024bit 接口連接到邏輯芯片。SK 海力士的目標是將 HBM4 直接堆疊在邏輯芯片上,完全消除中介層。

在某種程度上來講,這種方法有些類似于 AMD 的 3D V-Cache 堆疊,它就是直接將 L3 SRAM 緩存封裝在 CPU 芯片上,而如果是 HBM 的話則可以實現更高的容量且更便宜(IT之家注:HBM 顯然也會比緩存速度更慢)。

目前困擾業界的主要因素之一在于 HBM4 需要采用 2048bit 接口,因此 HBM4 的中介層非常復雜且成本高昂。因此,如果能夠將內存和邏輯芯片堆疊到一起,這對于經濟效益來說是可行的,但這同時又提出了另一個問題:散熱。

現代邏輯芯片,如 Nvidia H100,由于配備了巨大的 HBM3 內存,在帶來巨大 VRAM 帶寬的同時也產生了數百瓦的熱能。因此,要想為邏輯和內存封裝集合體進行散熱可能需要非常復雜的方法,甚至要考慮液冷和 / 或浸沒式散熱。

韓國科學技術院電氣與電子工程系的教授 Kim Jung-ho 表示,“如果散熱問題在兩到三代之后解決,那么 HBM 和 GPU 將能夠像一體一樣運作,而無需中介層” 。

一位業內人士告訴 Joongang,“在未來 10 年內,半導體的 ' 游戲規則 ' 可能會發生變化,存儲器和邏輯半導體之間的區別可能變得微不足道”。

免責聲明:本文由作者原創。文章內容系作者個人觀點,轉載目的在于傳遞更多信息,并不代表EETOP贊同其觀點和對其真實性負責。如涉及作品內容、版權和其它問題,請及時聯系我們,我們將在第一時間刪除!