模擬電路遷移和優化

2023-07-19 12:11:17 EETOP編譯來源:EETOP編譯自semiwiki

MunEDA 用戶組會議 (MUGM) 自 2006 年以來一直是一年一度的活動,今年有來自眾多客戶的約 80 名參與者參加,分享他們的經驗并學習如何獲得最佳的 EDA 工具結果。我已經能夠查看演示文稿和存檔視頻,接下來與大家分享特定工具類別中一些有趣的成功案例。

ST的工程師做了兩場演講,介紹了他們如何借助設計自動化軟件進行模擬電路移植和優化。ST的 Caroline Vaganay 在其 PDK 和設計流程小組工作,她將MunEDA 的用于模擬電路遷移的WiCkeD工具與其他供應商的三種內部設計進行了比較。

他們比較用于模擬電路遷移的 EDA 工具的標準是:

支持

他們的基準測試中使用了三個電路:

帶隙

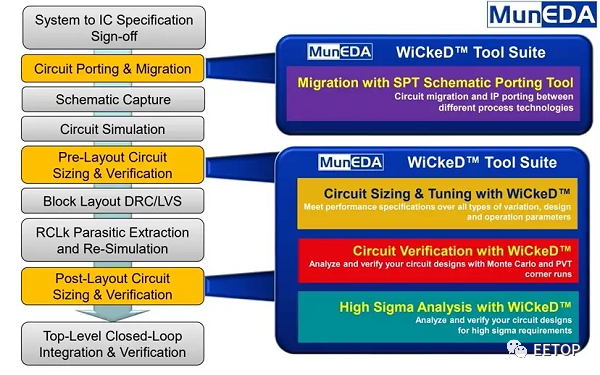

WiCkeD工具的總體設計流程如下所示:

對于設計為 0.25um 的 OPAMP 電路,他們希望通過改進所有 PVT corners的 Vio 和 Icc 來尋找更好的權衡選擇,實現 PGB > 20 MHz。優化結果表明,在標稱和最壞情況拐角處,所有性能值均在規格范圍內,并且運行時間僅需 4 小時 5 分鐘即可完成 7,455 次模擬。在最壞的情況下,性能穩健性得到改善,總良率從 14% 提高到 71%。

他們要優化的第二個電路是使用 40nm 技術的電壓參考緩沖器,其目標是改善 PVT corners上的電流重新復制,以最大限度地減少任何工藝變化的影響。WiCkeD 被指示更改設計參數以減少局部變化,從而改善性能指標的標準偏差:

DELTA_PC_X8, upper, 45.7%

Caroline 的最終基準電路是 0.18um 帶隙基準,其目標是優化電阻網絡,以在整個溫度范圍內獲得最小補償曲率,同時顯示穩定性并達到 PSRR、功耗和帶寬目標。

WiCkeD 優化器僅通過 8,107 次模擬就能滿足所有性能目標和 DC 條件,模擬時間為 9 小時 40 分鐘。借助 MunEDA 工具,他們在速度和準確性上擊敗了其他工具,找到了其他工具無法找到的解決方案。

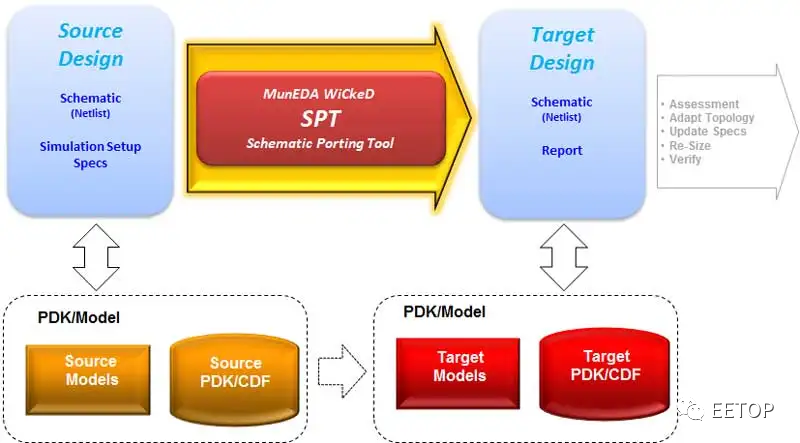

ST 的Maxime Blattes分享了他對SPT的評估,他們移植原理圖的步驟是:

運行更新參數過程

他們之前使用 Cadence Virtuoso 的流程需要定制,這對于非 CAD 工程師來說很困難,并且需要技能開發人員。移植工具的承諾是節省時間和人才。SPT 是一個基于 GUI 的工具,使工程師能夠更輕松、快速地完成符號映射、屬性映射和自動提取原理圖等任務。之前移植的最長部分是解決線路更新問題,現在通過 SPT 實現自動化。

非CAD工程師的設計師可以自行使用SPT,快速創建任何需要的模板,并在短時間內學習該工具。他們使用 SPT 只花了 30 分鐘,而使用 SKILL 編碼則需要大約 2 天的時間。

MunEDA 的 Matthias Sylvester 的第三次演示是 SPT 演示,其中他將 3 引腳到 3 引腳 MOS 設計的示例原理圖從 180nm 移植到 90nm,然后是 3 引腳到 4 引腳 MOS。他關于原理圖移植的 SPT 的主要觀點是:

SPT 比其他工具更強大、更方便

模擬電路遷移和優化可以是手動過程,也可以是自動過程,ST MicroElectronics 等公司已使用 MunEDA 的 WiCkeD 工具來實現過程自動化,產生的結果滿足面積、良率、性能和魯棒性等規格。是的,模擬設計仍然一半是藝術,一半是工程,但是使用 EDA 自動化工具可以讓您的工程師在比手動方法更短的時間內獲得更好的結果。原理圖移植工具 - SPT 是在節點和晶圓廠之間遷移任何原理圖的快速方法。