臺積電技術(shù)大秀!揭示最新技術(shù)新發(fā)展

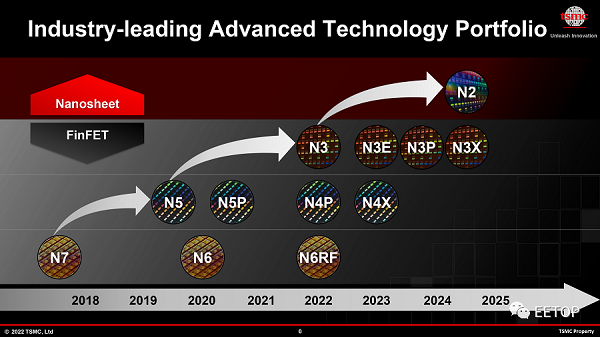

2023-04-27 11:49:43 EETOP臺積電在美國當(dāng)?shù)貢r間26 日舉辦2023 年北美技術(shù)論壇,會中揭示其最新的技術(shù)發(fā)展,包括2納米技術(shù)進(jìn)展,及業(yè)界領(lǐng)先的3納米技術(shù)家族新成員,以提供廣泛的技術(shù)組合滿足客戶多樣化的需求。其中包括支持更佳功耗、效能與密度的強化版N3P 制程、為高效能運算應(yīng)用量身打造的N3X 制程、以及支持車用客戶及早采用業(yè)界最先進(jìn)制程技術(shù)的N3AE 解決方案等。

臺積電總裁魏哲家表示,臺積電的客戶從未停止尋找新方法,以利用芯片的力量為世界帶來令人驚嘆的創(chuàng)新,并創(chuàng)造更美好的未來。憑借著相同的精神,臺積電也持續(xù)成長進(jìn)步,加強并推進(jìn)我們的制程技術(shù),提高效能、功耗效率及功能性,協(xié)助客戶在未來持續(xù)釋放更多的創(chuàng)新。

1. 更廣泛的3納米技術(shù)組合,包括N3P、N3X、以及N3AE。因為隨著N3 制程已進(jìn)入量產(chǎn),強化版N3E 制程預(yù)計將于2023 年量產(chǎn),臺積電推出更多3納米技術(shù)家族成員以滿足客戶多樣化的需求。

N3P 預(yù)計于2024 年下半年進(jìn)入量產(chǎn),相較于N3E,在相同漏電下,速度增快5%。在相同速度下,功耗降低5~10%,芯片密度增加4%。

N3X 著重于效能與最大時脈頻率以支持高效能運算應(yīng)用,相較于N3P,在驅(qū)動電壓1.2伏特下,速度增快5%,并擁有相同的芯片密度提升幅度,預(yù)計于2025 年進(jìn)入量產(chǎn)。

N3AE 將提供以N3E 為基礎(chǔ)的汽車制程設(shè)計套件(PDK),預(yù)計于2023 年推出,讓客戶能夠提早采用3納米技術(shù)來設(shè)計汽車應(yīng)用產(chǎn)品,以便于2025 年及時采用屆時已全面通過汽車制程驗證的N3A 制程。

2.納米技術(shù)開發(fā)進(jìn)展良好。臺積電2納米技術(shù)采用納米片晶體管架構(gòu),在良率與元件效能上皆展現(xiàn)良好的進(jìn)展,將如期于2025 年量產(chǎn)。相較于N3E,在相同功耗下,速度最快將可增加至15%。在相同速度下,功耗最多可降低30%,同時芯片密度增加大于15%。

3. N4PRF 推進(jìn)CMOS 射頻技術(shù)之極限。在2021 年推出N6RF 技術(shù)后,臺積電進(jìn)一步開發(fā)N4PRF,此為業(yè)界最先進(jìn)的互補式金屬氧化物半導(dǎo)體(CMOS) 射頻技術(shù),以支持Wi-Fi 7 射頻系統(tǒng)單芯片等數(shù)位密集型的射頻應(yīng)用。相較于N6RF,N4PRF 邏輯密度增加77%,且在相同速度下,功耗降低45%。

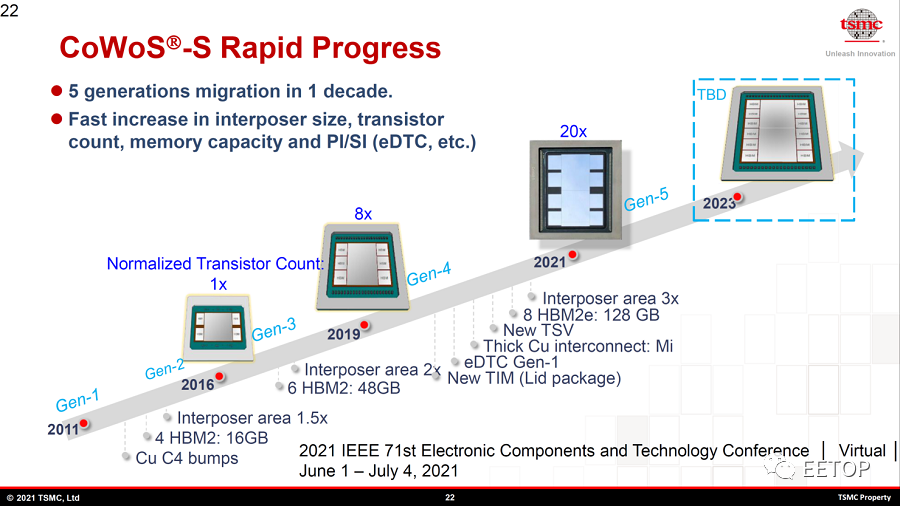

4. TSMC 3DFabricTM 先進(jìn)封裝及硅晶堆疊。臺積電3DFabric系統(tǒng)整合技術(shù)之主要新發(fā)展包括:

先進(jìn)封裝:為了滿足高效能運算應(yīng)用在單一封裝中置入更多處理器及存儲器的需求,臺積電正在開發(fā)具有高達(dá)6 個光罩尺寸(約5,000 平方毫米) 重布線層(RDL) 中介層的CoWoS 解決方案,能夠容納12 個高頻寬存儲器堆疊。

三維芯片堆疊:臺積電宣布推出SoIC-P,做為系統(tǒng)整合芯片(SoIC) 解決方案的微凸塊版本,提供具有成本效益的方式來進(jìn)行3D 芯片堆疊,SoIC-P 加上目前的SoIC-X 無凸塊解決方案,使得臺積電的3D IC 技術(shù)更臻完善。

設(shè)計支持:臺積電推出開放式標(biāo)準(zhǔn)設(shè)計語言的最新版本3DbloxTM 1.5,旨在降低三維集成電路(3D IC) 的設(shè)計門檻。3DbloxTM 1.5 增加了自動凸塊合成的功能,協(xié)助芯片設(shè)計人員處理具有數(shù)千個凸塊的復(fù)雜大型芯片,可縮短數(shù)個月的設(shè)計時程。

另外,臺積電技術(shù)論壇后續(xù)將陸續(xù)在包括美國奧斯丁、波士頓、歐洲、以色列、中國大陸、以及日本舉行。其中,5/11 將移師臺北舉辦。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章