DDR5訓(xùn)練模式介紹

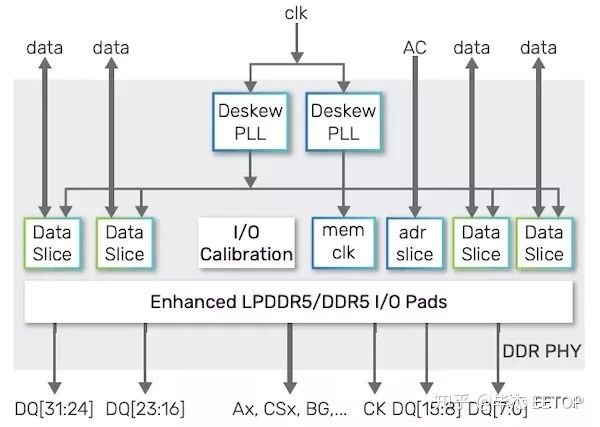

2020-11-08 12:15:53 EETOPCadence最近在臺(tái)積電N5工藝上發(fā)布了針對(duì)DDR5和LPDDR5 DRAM存儲(chǔ)標(biāo)準(zhǔn)的硅驗(yàn)證IP。

新的多標(biāo)準(zhǔn)IP面向數(shù)據(jù)中心、存儲(chǔ)、人工智能/機(jī)器學(xué)習(xí)(AI / ML)和超大規(guī)模計(jì)算等應(yīng)用。同時(shí)支持DDR5和LPDDR5協(xié)議的新IP成為單芯片解決方案,可用于具有不同DRAM要求的產(chǎn)品中。

據(jù)SK Hynix稱,具有高數(shù)據(jù)速率的DDR5預(yù)計(jì)到2024年將占據(jù)全球DRAM市場(chǎng)份額的43%。使DDR5的高數(shù)據(jù)速率成為現(xiàn)實(shí)的關(guān)鍵技術(shù)之一是決策反饋均衡(DFE)。

在本文中,我們將介紹另一種重要技術(shù),即DDR校準(zhǔn)概念,該技術(shù)可實(shí)現(xiàn)此內(nèi)存接口的最佳性能。

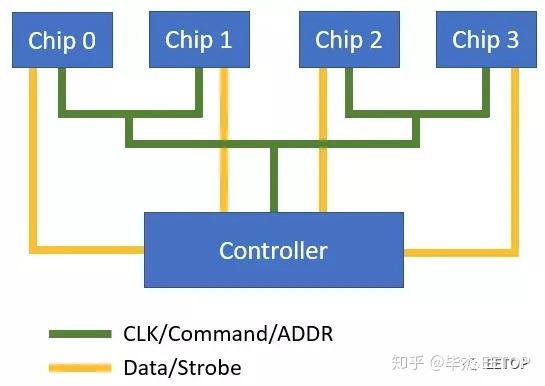

T分支拓?fù)浣Y(jié)構(gòu)

我們通常需要采用多個(gè)內(nèi)存芯片來(lái)增加系統(tǒng)的內(nèi)存容量。在這種情況下,布線策略會(huì)對(duì)最終的內(nèi)存性能產(chǎn)生重大影響。其中一種方案是下圖所示的T型分支連接。

這種配置通常用于DDR2芯片,CLK/指令/地址線被路由到一個(gè)中心點(diǎn),然后從該中心節(jié)點(diǎn)分配到不同的DRAM芯片。當(dāng)與系統(tǒng)中的不同存儲(chǔ)芯片通信時(shí),這使我們能夠?yàn)镃LK /命令/地址線設(shè)置匹配的走線長(zhǎng)度。

CLK /命令/地址信號(hào)具有幾乎相同的傳播延遲,從而簡(jiǎn)化了設(shè)計(jì)過(guò)程。但是,T分支拓?fù)鋾?huì)增加這些信號(hào)線的電容負(fù)載。

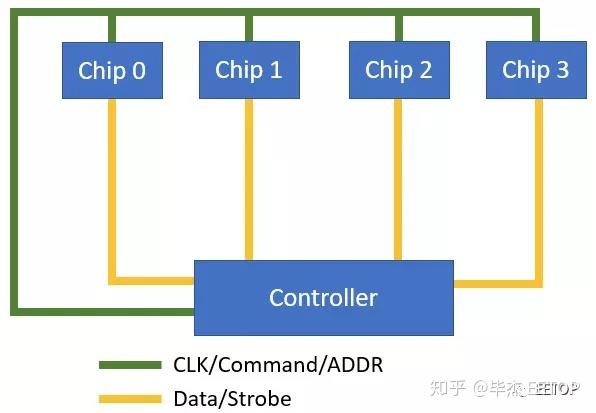

Fly-By拓?fù)?/b>

另一種解決方案是DDR3和新一代DDR技術(shù)采用的Fly-By拓?fù)浣Y(jié)構(gòu)。Fly-By拓?fù)湓趯r(shí)鐘、命令和地址線從控制器路由到DRAM芯片時(shí),采用了菊花鏈結(jié)構(gòu)。這一點(diǎn)在下面進(jìn)行了描述。

Fly-By拓?fù)?/b>

注意,數(shù)據(jù)(DQ)和選通信號(hào)(DQS)與星形分支連接一樣以星形配置連接。使用Fly-By配置,由于信號(hào)在不同DRAM芯片上的到達(dá)時(shí)間略有不同,因此我們可以更輕松地應(yīng)對(duì)增加的電容負(fù)載。

由于信號(hào)在略微不同的時(shí)間遇到DRAM芯片的輸入電容,因此總體電容性負(fù)載表現(xiàn)為這些信號(hào)的分布式負(fù)載。因此,對(duì)于給定的系統(tǒng)存儲(chǔ)容量,有效地減小了電容性負(fù)載,因此,改善了信號(hào)完整性和數(shù)據(jù)速率。

這種技術(shù)的缺點(diǎn)是,與具有較短點(diǎn)對(duì)點(diǎn)連接的數(shù)據(jù)和選通信號(hào)相比,菊花鏈控制和地址信號(hào)的延遲較大。此外,控制和地址信號(hào)在不同的時(shí)間到達(dá)不同的DRAM。在高于1 GHz的速度下,這些時(shí)間偏差會(huì)使?jié)M足信號(hào)建立/保持時(shí)間要求非常具有挑戰(zhàn)性。

為了解決這個(gè)問(wèn)題,高帶寬存儲(chǔ)器接口,如DDR4和DDR5,采用訓(xùn)練模式來(lái)測(cè)量PCB線路的時(shí)間偏斜。有了時(shí)間偏移,控制器就可以給從控制器驅(qū)動(dòng)到DRAM的數(shù)據(jù)信號(hào)引入適當(dāng)?shù)难舆t,使數(shù)據(jù)到達(dá)時(shí)與指令和地址信號(hào)有良好的時(shí)序關(guān)系。

這些訓(xùn)練模式之一是write leveling。

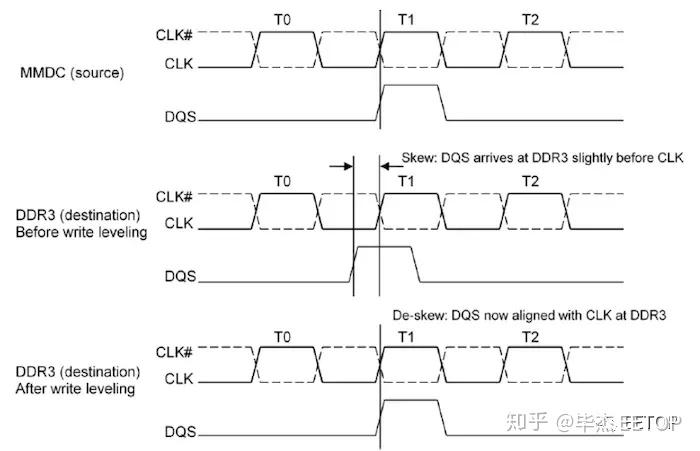

write leveling

為了進(jìn)行可靠的寫(xiě)操作,選通信號(hào)(DQS)的邊沿應(yīng)在時(shí)鐘邊沿的預(yù)定范圍內(nèi)。與具有較短點(diǎn)對(duì)點(diǎn)連接的選通信號(hào)相比,采用Fly-By拓?fù)洌跃栈ㄦ湻绞竭B接的時(shí)鐘信號(hào)會(huì)有較大的延遲。為了對(duì)齊這兩個(gè)信號(hào),DDR3和較新的DDR代提供了write leveling訓(xùn)練模式。

在這種模式下(發(fā)生在設(shè)備初始化期間),控制器不斷將選通信號(hào)發(fā)送到特定的DRAM。當(dāng)DRAM接收到選通信號(hào)時(shí),它將對(duì)時(shí)鐘信號(hào)進(jìn)行采樣,并將其在數(shù)據(jù)總線上的值返回給控制器。

在write leveling開(kāi)始時(shí),由于時(shí)鐘信號(hào)經(jīng)歷了較大的延遲,因此返回值為零。控制器將為DQS信號(hào)引入越來(lái)越多的延遲,直到控制器觀察到數(shù)據(jù)總線上從零到一的轉(zhuǎn)變?yōu)橹埂4藭r(shí),控制器將鎖定此校準(zhǔn)延遲設(shè)置,并將其用于以后的寫(xiě)操作。

執(zhí)行寫(xiě)操作時(shí),控制器會(huì)將這種延遲引入數(shù)據(jù)和選通信號(hào)。這種偏斜將使數(shù)據(jù)和控制信號(hào)以適當(dāng)?shù)臅r(shí)序到達(dá)DRAM輸入。下圖說(shuō)明了write leveling訓(xùn)練模式。

請(qǐng)注意,時(shí)鐘和DQS之間的時(shí)滯對(duì)于不同的DRAM芯片而言并不相同。因此,應(yīng)為系統(tǒng)中的每個(gè)DRAM執(zhí)行write leveling。

DDR5的訓(xùn)練模式

DDR5支持幾種不同的訓(xùn)練模式,這些模式對(duì)其高數(shù)據(jù)速率能力有重大影響。除了上面討論的write leveling以外,DDR5還包括新的讀前導(dǎo)訓(xùn)練模式,命令/地址訓(xùn)練模式和芯片選擇訓(xùn)練模式。DDR5還具有新功能以補(bǔ)償無(wú)與倫比的DQ-DQS接收器架構(gòu),從而進(jìn)一步提高了數(shù)據(jù)速率。

與DDR5讀取訓(xùn)練相關(guān)的數(shù)據(jù)模式包括默認(rèn)的可編程串行模式、簡(jiǎn)單的時(shí)鐘模式和線性反饋移位寄存器(LFSR)生成的模式,可用于在處理DDR5高數(shù)據(jù)速率時(shí)擁有更穩(wěn)健的時(shí)序余量。

關(guān)鍵詞: DDR5 DDR5訓(xùn)練

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章