臺(tái)積電公布5nm生產(chǎn)技術(shù)平臺(tái)細(xì)節(jié)

2020-02-06 12:16:24 EETOP早在2019年4月,臺(tái)積電宣布將在風(fēng)險(xiǎn)生產(chǎn)中引入其5nm技術(shù),在IEDM 2019上,臺(tái)積電對經(jīng)過1000小時(shí)HTOL并將于2020年1H投入量產(chǎn)的5nm工藝進(jìn)行了詳細(xì)描述。這種5nm技術(shù)是一種從7nm節(jié)點(diǎn)擴(kuò)展到全節(jié)點(diǎn)的技術(shù),使用主要設(shè)計(jì)規(guī)則(柵極、鰭和Mx/Vx節(jié)距)的智能擴(kuò)展來提高成品率,具有0.021um2 的SRAM單元和領(lǐng)先于計(jì)劃的下降缺陷密度D0。

5nm技術(shù)平臺(tái)成功的主要原因是實(shí)現(xiàn)了極紫外(EUV)光刻技術(shù)。成熟的EUV在切割、接觸、通孔和金屬線掩蔽步驟上至少替換了至少四倍的浸沒層,從而縮短了周期時(shí)間,提高了可靠性和良率。

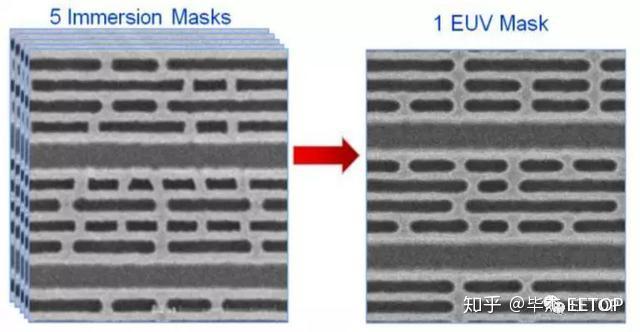

5nm中的總掩模數(shù)量比以前的7nm節(jié)點(diǎn)少幾個(gè)。圖1顯示了一個(gè)EUV掩模如何代替五個(gè)浸沒掩模,又如何產(chǎn)生更好的圖案保真度,更短的循環(huán)時(shí)間和更少的缺陷。

圖1. BEOL金屬化圖,將EUV與浸沒光刻法進(jìn)行了比較,顯示了一個(gè)EUV掩模如何以更好的圖案保真度,更短的循環(huán)時(shí)間和更少的缺陷取代了五個(gè)浸沒圖案層。

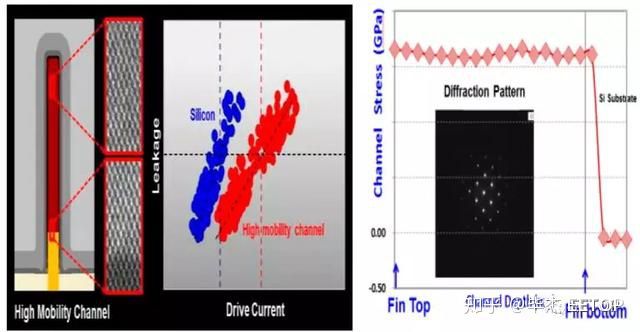

從16nm節(jié)點(diǎn)到7nm,F(xiàn)inFET已經(jīng)使用了四代,但作為通道遷移的性能一直停滯不前。為了解決這個(gè)問題,采用了高移動(dòng)性信道(HMC)以提高性能。圖2中的TEM顯示了與Si晶格常數(shù)相接的完全應(yīng)變HMC晶格常數(shù)。

圖2. finFET截面TEM的示意圖,顯示了與Si晶格常數(shù)相接的全應(yīng)變HMC晶格常數(shù)。第二個(gè)圖顯示,硅與HMC晶體管的漏電流與驅(qū)動(dòng)電流的關(guān)系更大。第三幅圖顯示了通道應(yīng)力(以GPa為單位)與從鰭片頂部到鰭片底部的通道深度之間的關(guān)系。所示的衍射圖證實(shí)了HMC應(yīng)變。

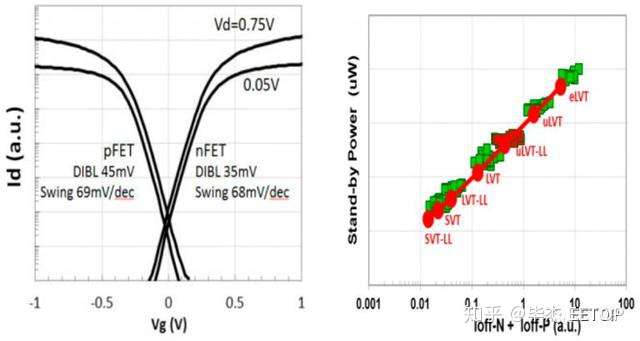

HMC finFET具有出色的Id-Vg特性,如圖3所示,并且產(chǎn)生的驅(qū)動(dòng)電流比Si finFET高出約18%。品質(zhì)因數(shù)(FOM)環(huán)形振蕩器的待機(jī)功率也與晶體管泄漏密切相關(guān)。

圖3.圖表顯示了對于不同的漏極電壓,高遷移率溝道(HMC)晶體管的漏極電流與柵極電壓(Id與Vg)的關(guān)系。第二幅圖顯示了該技術(shù)中可用的七個(gè)不同Vt的截止電流范圍Ioff-N和Ioff-P以及對待機(jī)電流的相對影響。兩個(gè)圖中的電流均為對數(shù)刻度,每格十進(jìn)制。漏極感應(yīng)勢壘降低(DIBL)為45mV和35mV,對于p溝道和n溝道晶體管,擺幅分別為69mV和68mV。

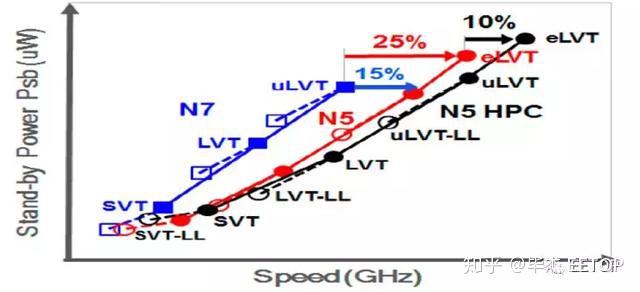

這種5nm CMOS平臺(tái)技術(shù)是IEDM 2016中描述的7nm工藝的完整節(jié)點(diǎn)擴(kuò)展。如圖4所示,每個(gè)晶體管類型最多可提供7個(gè)Vt,這使得產(chǎn)品設(shè)計(jì)能夠滿足移動(dòng)SoC的功率效率需求以及高性能計(jì)算的峰值速度需求。

圖4. N5中最多可提供7個(gè)Vt的圖表,顯示了N5和N5 HPC與N7相比,待機(jī)功率(uW)與GHz速度的對比,以滿足移動(dòng)設(shè)備的最大功率效率和HPC的峰值速度。eLVT在7nm處的峰值速度提高了25%。

HPC的新功能是極低的VT(eLVT)晶體管,其在7nm處的峰值速度提高了25%,并采用三鰭標(biāo)準(zhǔn)單元,從而使性能進(jìn)一步提高了10%。該技術(shù)可用于使用混合鍵合的3D芯片堆疊。除了相對于7nm而言令人印象深刻的密度和性能提升之外,該技術(shù)還獲得了1000小時(shí)HTOL認(rèn)證,相對于7nm技術(shù)而言,它具有改善的應(yīng)力老化特性。超出計(jì)劃的高良率SRAM和邏輯缺陷密度D0。能夠?qū)崿F(xiàn)這一進(jìn)展的技術(shù)成果包括可以完全實(shí)施EUV和高遷移率通道(HMC)finFET。

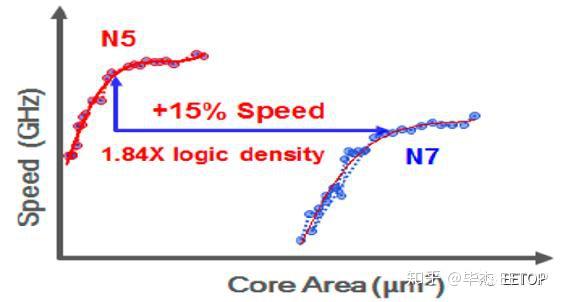

設(shè)計(jì)和開發(fā)此5nm平臺(tái)技術(shù)是為了滿足PPACT的目標(biāo)(功率,性能,面積,成本和上市時(shí)間)。設(shè)計(jì)技術(shù)協(xié)同優(yōu)化(DTCO)強(qiáng)調(diào)了智能縮放,避免了brute-force 縮放,因?yàn)閎rute-force 縮放會(huì)導(dǎo)致工藝成本和產(chǎn)量影響急劇增加。柵極-接觸-擴(kuò)散和獨(dú)特的擴(kuò)散終止以及基于EUV的柵極圖案等設(shè)計(jì)功能可降低SRAM的尺寸并提高邏輯密度。5nm技術(shù)在7nm節(jié)點(diǎn)的邏輯密度為1.84倍的情況下,在相同功率下的速度提高了15%,在相同速度下的功率降低了30%,如圖5所示。

圖5.比較N5技術(shù)和以前的N7 的速度(GHz)與核心面積(um2 )的比較。5nm技術(shù)在7nm節(jié)點(diǎn)的邏輯密度為1.84倍的情況下,在相同功率下的速度提高了15%,在相同速度下的功率降低了30%。

互連延遲會(huì)嚴(yán)重影響產(chǎn)品性能,并且每一代互連延遲都會(huì)變得越來越差。從N28到N5,后端金屬RC和過孔電阻如圖6所示。通過EUV圖案化,創(chuàng)新的按比例縮放的勢壘/襯里ESL / ELK電介質(zhì)和Cu回流焊,最緊密的間距Mx RC和Vx Rc保持與7nm節(jié)點(diǎn)相似。

圖6.示出了歸一化的BEOL金屬化RC產(chǎn)品和過孔電阻與節(jié)點(diǎn)(從N28到N5)之間的關(guān)系圖。對于最緊密的金屬間距,通過EUV圖案化,創(chuàng)新的按比例縮放的勢壘/襯里ESL / ELK電介質(zhì)和Cu回流焊,MX RC和過孔電阻Vx Rc保持與先前的7nm節(jié)點(diǎn)相似。

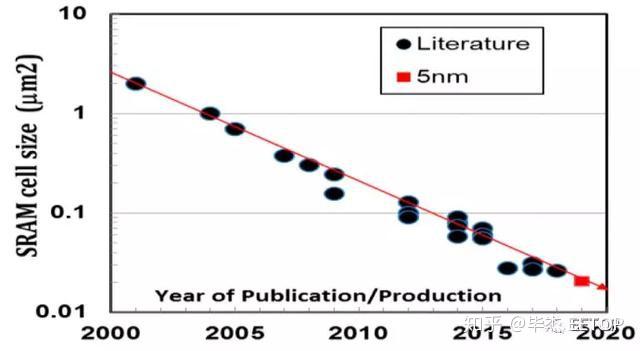

SRAM密度和性能/泄漏對于移動(dòng)SoC和HPC AI是至關(guān)重要的。在 F2 的特征尺寸方面,具有更高級(jí)節(jié)點(diǎn)的SRAM單元的縮放變得越來越困難。如圖7所示,所提供的高電流(HC)和高密度(HD) SRAM電池的電池面積分別為0.025um2 和0.021um2 ,是業(yè)界密度最高的器件。實(shí)現(xiàn)了始終如一的256 Mb SRAM高良率,邏輯測試芯片的峰值良率大于90%,平均良率約為80%(無需維修)。

Fig. 7. Chart of published SRAM cell size in um2 vs year of publication. The 5nm HD SRAM cell at 0.021 um2 is the densest offered in the industry.

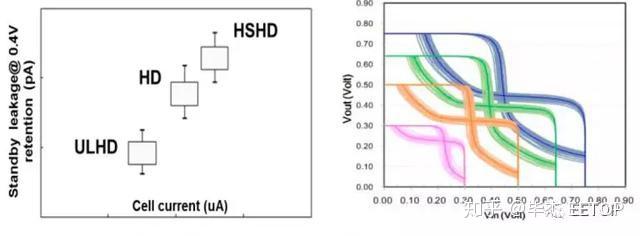

超低泄漏的ULHD可用于降低保留泄漏,提高功率效率,而高速HSHD SRAM可作為HC SRAM單元的替代方案,從而使存儲(chǔ)區(qū)域減少約22%,如圖8所示。

圖8. ULHD,HSHD和標(biāo)準(zhǔn)HD SRAM單元在0.4V時(shí)的pA待機(jī)泄漏與uA中的單元電流的關(guān)系圖。5nm HD SRAM單元的Vout與Vin蝶形曲線圖顯示在0.75V至0.3V的電壓下。

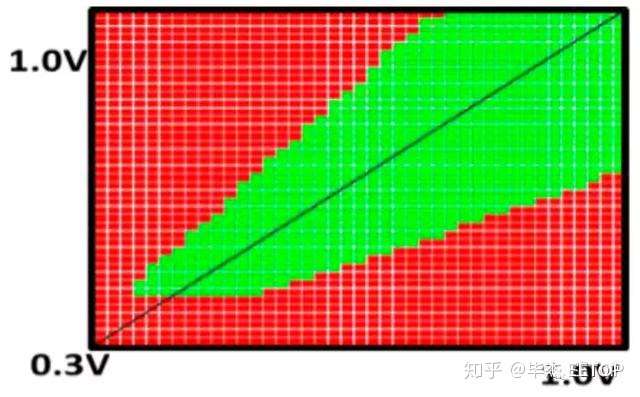

具有完整讀/寫功能的256Mb 0.021um2 HD SRAM單元的shmoo圖在圖9中顯示為低至0.4V。

圖9. Shmoo圖顯示了基于5nm 0.021um2 HD SRAM單元的256Mb SRAM從1.0V降至0.4V時(shí)Vout與Vin的關(guān)系。

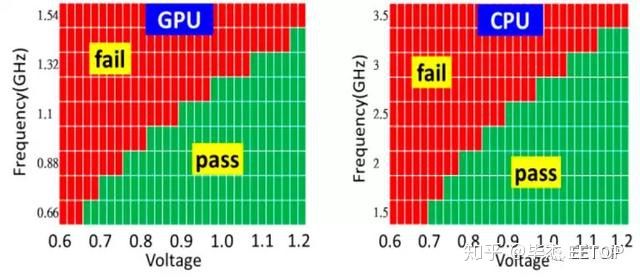

圖10顯示了高良率邏輯測試芯片中GPU和CPU模塊的頻率響應(yīng)shmoo圖。

圖10. 5nm鑒定工具中高良率邏輯測試芯片中GPU和CPU模塊的GHz頻率與電壓的Shmoo曲線。

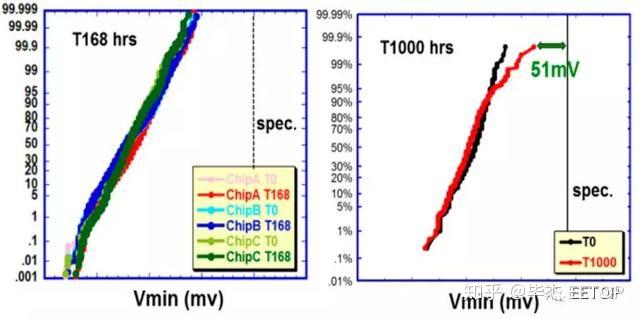

256Mb HD/HC SRAM和邏輯測試芯片通過了1000小時(shí)的HTOL認(rèn)證。SRAM Vmin在168小時(shí)時(shí)的變化可以忽略不計(jì),并且以約51mV的裕度通過了1000小時(shí)的HTOL,如圖11所示。

圖11. Plots of log-normal distribution vs Vmin in mV at 168 hours HTOL showing negligible Vmin shift and at 1000 hours HTOL, passing 1000 hours with 51mV margin.

使用圖12所示的高遷移率通道finFET制成的5nm FOM環(huán)形振蕩器在0.96 V和125C時(shí)的應(yīng)力老化數(shù)據(jù),相對于7nm節(jié)點(diǎn)具有更好的老化性能。

圖12. N5 HMC finFET環(huán)形振蕩器和N7硅finFET環(huán)形振蕩器在125℃下的T50%壽命(年)與老化電壓應(yīng)力Vstr的關(guān)系圖,顯示在5nm節(jié)點(diǎn)處的老化相對于在7nm處有所改善。

HPC的另一個(gè)重要功能是在BEOL金屬化層的上層中形成的金屬-絕緣體-金屬(MiM)電容器。5nm節(jié)點(diǎn)MiM的電容密度是典型HD-MiM的4倍,并通過最小化瞬態(tài)下降電壓使Fmax快約4.2%,并在CPU測試芯片中將Vmin降低了約20mV。

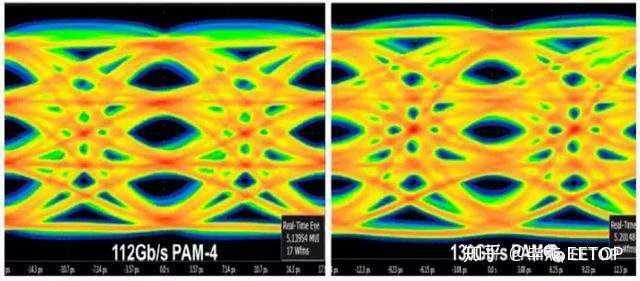

HPC嚴(yán)重依賴于高速IO,尤其是SERDES。通過使用特殊的高速設(shè)備成功優(yōu)化finFET驅(qū)動(dòng)強(qiáng)度和電容/電阻,PAM-4 SERDES發(fā)射機(jī)速度在0.78 pJ/bit時(shí)為112Gb/s,在0.96pJ/b時(shí)為130Gb/s,如圖13所示。

圖13.分別顯示了在SERDES PAM-4中以0.78pJ/b和0.96pJ / b進(jìn)行數(shù)據(jù)傳輸時(shí),112Gb/s和130Gb/ s的電壓輸出信號(hào)特性(以mV為單位)與時(shí)間(以ps為單位)的關(guān)系。

總而言之,臺(tái)積電提供了一個(gè)極具競爭力的技術(shù)平臺(tái),確立了其在同類最佳的最高密度邏輯技術(shù)領(lǐng)域的領(lǐng)導(dǎo)者地位。2020年上半年的批量生產(chǎn)將使先進(jìn)的SoC產(chǎn)品在移動(dòng)設(shè)備(尤其是5G)以及用于AI,數(shù)據(jù)中心和區(qū)塊鏈產(chǎn)品的HPC應(yīng)用中實(shí)現(xiàn)領(lǐng)先,這些產(chǎn)品越來越需要高性能和最佳能效。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章