逆向?qū)W習(xí):解析40年前里程碑處理器80386預(yù)取隊(duì)列電路

2025-07-11 12:11:06 EETOP關(guān)注我們 設(shè)為星標(biāo)

EETOP

百萬(wàn)芯片工程師專業(yè)技術(shù)論壇

官方微信號(hào)

在本文中,我將詳細(xì)剖析 386 的預(yù)取隊(duì)列電路。其中一個(gè)有趣的電路是增量器,它給一個(gè)指針加 1,以按順序遍歷內(nèi)存。這聽(tīng)起來(lái)好像很簡(jiǎn)單,但為了實(shí)現(xiàn)高性能,增量器采用了復(fù)雜的電路設(shè)計(jì)。預(yù)取隊(duì)列使用一個(gè)大型電路網(wǎng)絡(luò)來(lái)對(duì)字節(jié)進(jìn)行移位操作,確保它們能正確對(duì)齊。它還設(shè)有一個(gè)簡(jiǎn)潔的電路,用于將有符號(hào)的 8 位和 16 位數(shù)字?jǐn)U展為 32 位。本文雖不會(huì)有重大發(fā)現(xiàn),但如果你對(duì)底層電路和動(dòng)態(tài)邏輯感興趣,不妨繼續(xù)閱讀。

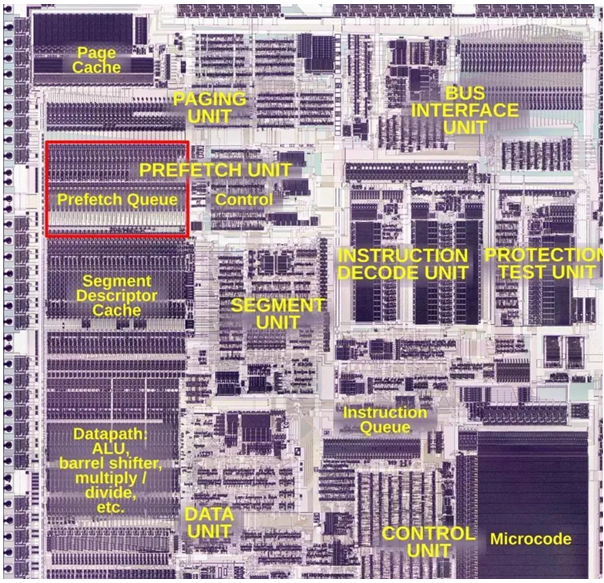

下圖展示了在顯微鏡下,386 那如指甲蓋大小、閃閃發(fā)亮的硅芯片。盡管它看起來(lái)可能像一座分區(qū)奇特城市的航拍圖,但芯片照片揭示了芯片的功能模塊。左上角的預(yù)取單元(Prefetch Unit)就是我們關(guān)注的模塊。

在本文中,我將討論預(yù)取隊(duì)列電路(用紅色突出顯示部分),暫不涉及右側(cè)的預(yù)取控制電路。預(yù)取單元從與內(nèi)存通信的總線接口單元(Bus Interface Unit,右上角)接收數(shù)據(jù)。指令解碼單元(Instruction Decode Unit)則逐個(gè)字節(jié)地從預(yù)取單元接收預(yù)取指令,并對(duì)操作碼進(jìn)行解碼,以便執(zhí)行。

這張 386 的芯片裸片照片顯示了寄存器的位置

芯片的左四分之一部分由一條條電路組成,這些電路看起來(lái)比芯片其他部分規(guī)整得多。這種類似網(wǎng)格的外觀源于每個(gè)功能模塊(在很大程度上)都是通過(guò)將相同電路重復(fù) 32 次構(gòu)建而成的,每個(gè)位對(duì)應(yīng)一次,并排排列。垂直數(shù)據(jù)線以 32 位為一組上下延伸,連接各個(gè)功能模塊。為了實(shí)現(xiàn)這一點(diǎn),每個(gè)電路在芯片上必須適配相同的寬度;這種布局限制迫使電路設(shè)計(jì)師開(kāi)發(fā)出一種能高效利用該寬度且不超出允許寬度的電路。預(yù)取隊(duì)列的電路采用了相同方法:每個(gè)電路寬 66 微米,重復(fù) 32 次。正如后文將看到的,要把預(yù)取電路塞進(jìn)這個(gè)固定寬度,需要一些布局技巧。

預(yù)取單元的目的是通過(guò)在指令需要執(zhí)行前從內(nèi)存中讀取它們來(lái)加快性能,這樣處理器就無(wú)需等待從內(nèi)存獲取指令。預(yù)取利用了內(nèi)存總線閑置的時(shí)間,盡量減少與其他讀寫(xiě)數(shù)據(jù)指令的沖突。在 386 中,預(yù)取的指令存儲(chǔ)在一個(gè) 16 字節(jié)的隊(duì)列中,該隊(duì)列由四個(gè) 32 位塊組成。

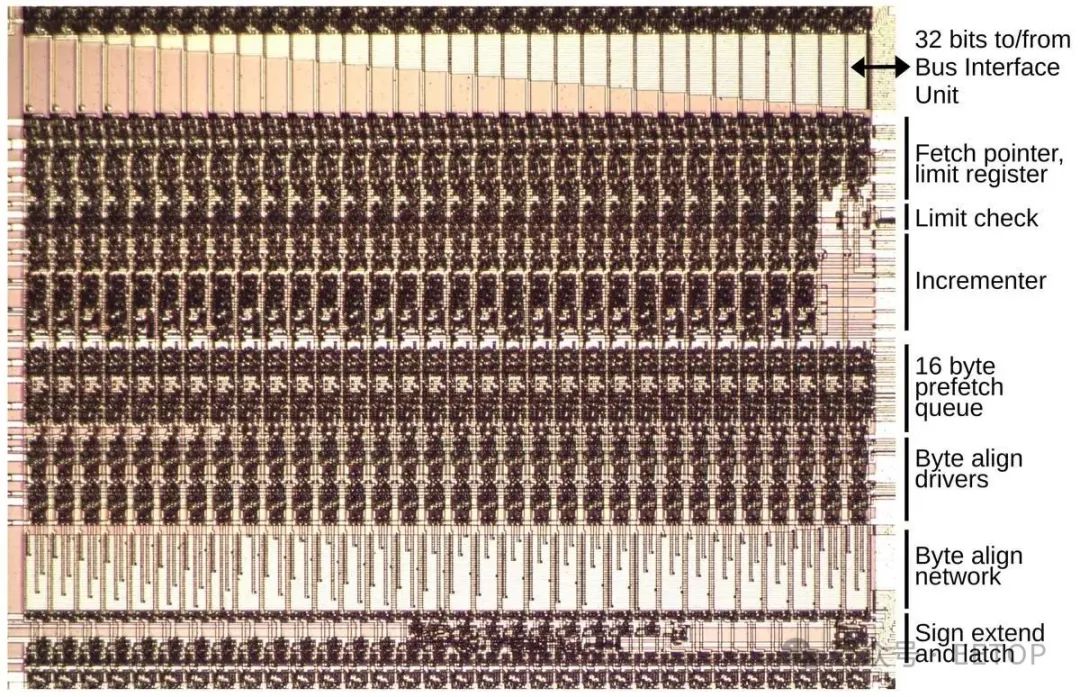

下圖放大展示了預(yù)取器及其主要組件。你可以看到,相同的電路(在大多數(shù)情況下)是如何重復(fù) 32 次,形成垂直條帶的。頂部是來(lái)自總線接口單元的 32 條總線線路。這些線路通過(guò)總線接口單元在數(shù)據(jù)通路和外部?jī)?nèi)存之間建立連接。當(dāng)右側(cè)的 32 條水平線分支并形成 32 條垂直線(每個(gè)位對(duì)應(yīng)一條)時(shí),這些線路形成一個(gè)三角形圖案。接下來(lái)是取指指針(fetch pointer)和限制寄存器(limit register),以及一個(gè)用于檢查取指指針是否已到達(dá)限制的電路。注意,增量器和限制檢查電路的兩個(gè)低階位(右側(cè))的電路缺失了。在增量器的底部,你可以看到某些位位置的電路與其他位置相比,有一塊缺失,打破了重復(fù)塊的圖案。16 字節(jié)的預(yù)取隊(duì)列在增量器下方。盡管這個(gè)內(nèi)存是預(yù)取器的核心,但它的電路占用的面積相對(duì)較小。

預(yù)取器的特寫(xiě),標(biāo)注了主要模塊。在右側(cè),預(yù)取器接收控制信號(hào)

預(yù)取器的底部會(huì)根據(jù)需要對(duì)數(shù)據(jù)進(jìn)行移位以對(duì)齊。一個(gè) 32 位的值可能會(huì)跨預(yù)取緩沖區(qū)的兩個(gè) 32 位行拆分存儲(chǔ)。為處理這種情況,預(yù)取器包含一個(gè)數(shù)據(jù)移位網(wǎng)絡(luò)來(lái)對(duì)數(shù)據(jù)進(jìn)行移位和對(duì)齊。這個(gè)網(wǎng)絡(luò)占用大量空間,但這里沒(méi)有有源電路:只有水平和垂直導(dǎo)線組成的網(wǎng)格。

最后,符號(hào)擴(kuò)展電路(sign extend circuitry)會(huì)根據(jù)需要將有符號(hào)的 8 位或 16 位值轉(zhuǎn)換為有符號(hào)的 16 位或 32 位值。可以看到,符號(hào)擴(kuò)展電路非常不規(guī)則,尤其是在中間部分。一個(gè)鎖存器存儲(chǔ)預(yù)取隊(duì)列的輸出,供數(shù)據(jù)通路的其他部分使用。

如果你編寫(xiě)過(guò) x86 程序,可能知道處理器的指令指針(EIP),它存儲(chǔ)著下一條要執(zhí)行指令的地址。在程序執(zhí)行時(shí),指令指針會(huì)從一條指令指向下一條指令。然而,事實(shí)證明,指令指針實(shí)際上并不 “存在”!相反,386 有一個(gè) “提前指令取指指針”(Advance Instruction Fetch Pointer),它存儲(chǔ)著下一條要預(yù)取到預(yù)取隊(duì)列中的指令地址。但有時(shí)處理器需要知道指令指針的值,例如,在調(diào)用子例程時(shí)確定返回地址,或者計(jì)算相對(duì)跳轉(zhuǎn)的目標(biāo)地址。那該怎么辦呢?處理器從預(yù)取隊(duì)列電路中獲取提前指令取指指針地址,然后減去預(yù)取隊(duì)列當(dāng)前的長(zhǎng)度。結(jié)果就是下一條要執(zhí)行指令的地址,即所需的指令指針值。

提前指令取指指針(即下一條要預(yù)取指令的地址)存儲(chǔ)在預(yù)取隊(duì)列電路頂部的一個(gè)寄存器中。隨著指令被預(yù)取,這個(gè)指針會(huì)由預(yù)取電路遞增。(由于每次取指 32 位,所以這個(gè)指針每次遞增 4,且最低兩位始終為 0。)

但是什么阻止預(yù)取器預(yù)取過(guò)度,超出有效內(nèi)存范圍呢?x86 架構(gòu)因使用段來(lái)定義內(nèi)存的有效區(qū)域而聞名。一個(gè)段有起始和結(jié)束地址(稱為基地址和限制地址),通過(guò)阻止對(duì)段外的訪問(wèn)來(lái)保護(hù)內(nèi)存。386 有六個(gè)活動(dòng)段;相關(guān)的是存儲(chǔ)程序指令的代碼段(Code Segment)。因此,代碼段的限制地址控制著預(yù)取器何時(shí)必須停止預(yù)取。預(yù)取隊(duì)列包含一個(gè)電路,當(dāng)取指指針到達(dá)代碼段的限制時(shí),該電路會(huì)停止預(yù)取。在本節(jié)中,我將描述這個(gè)電路。

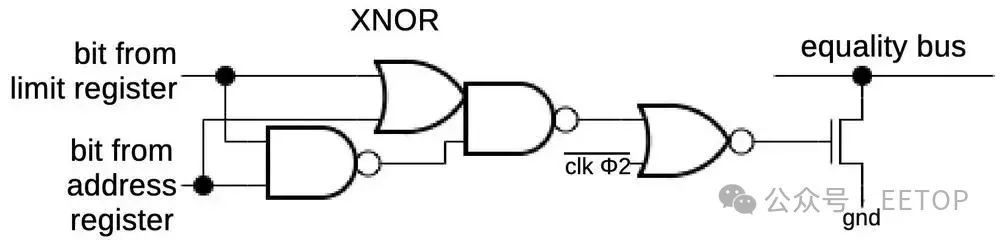

比較兩個(gè)值看似簡(jiǎn)單,但 386 使用了一些技巧來(lái)加快比較速度。基本思路是使用 30 個(gè)異或(XOR)門(mén)來(lái)比較兩個(gè)寄存器的位。(為什么是 30 位而不是 32 位呢?因?yàn)槊看稳?nbsp;32 位,地址的最低兩位是 00,可以忽略。)如果兩個(gè)寄存器匹配,所有異或結(jié)果都為 0;如果不匹配,至少有一個(gè)異或結(jié)果為 1。從概念上講,將異或門(mén)的輸出連接到一個(gè) 32 輸入的或(OR)門(mén),就能得到期望的結(jié)果:如果所有位都匹配,輸出為 0;如果存在不匹配,輸出為 1。但遺憾的是,出于電學(xué)原因,使用標(biāo)準(zhǔn) CMOS 邏輯構(gòu)建一個(gè) 32 輸入的或門(mén)是不現(xiàn)實(shí)的,而且它的體積大到難以融入電路。相反,386 使用動(dòng)態(tài)邏輯來(lái)實(shí)現(xiàn)一個(gè)分散的或非(NOR)門(mén),預(yù)取器的每一列中有一個(gè)晶體管。

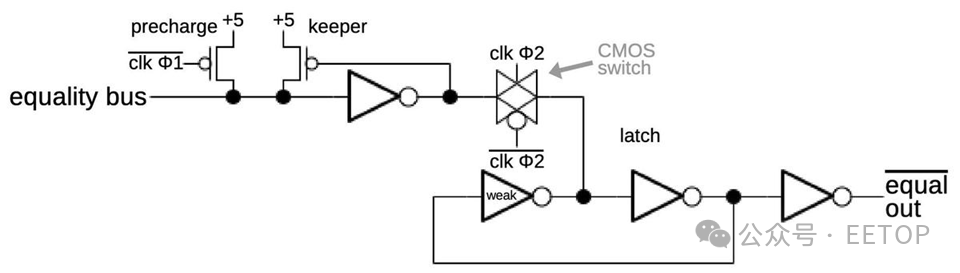

下圖展示了一位相等比較的實(shí)現(xiàn)。其機(jī)制是,如果兩個(gè)寄存器不同,右側(cè)的晶體管會(huì)導(dǎo)通,將相等總線(equality bus)拉低。這個(gè)電路重復(fù) 30 次,比較所有位:如果有任何不匹配,相等總線會(huì)被拉低;如果所有位都匹配,總線保持高電平。左側(cè)的三個(gè)門(mén)實(shí)現(xiàn)異或非(XNOR);這個(gè)電路可能看起來(lái)過(guò)于復(fù)雜,但它是實(shí)現(xiàn)異或非的標(biāo)準(zhǔn)方法。右側(cè)的或非門(mén)會(huì)在時(shí)鐘相位 2 之外阻止比較(其重要性將在下文解釋)。

這個(gè)電路重復(fù) 30 次以比較寄存器

相等總線水平穿過(guò)預(yù)取器,如果有任何位不匹配,總線就會(huì)被拉低。但是什么讓總線保持高電平呢?這由下面的動(dòng)態(tài)電路負(fù)責(zé)。與常規(guī)靜態(tài)門(mén)不同,動(dòng)態(tài)邏輯由處理器的時(shí)鐘信號(hào)控制,并依賴電路中的電容來(lái)保存數(shù)據(jù)。386 由兩相時(shí)鐘信號(hào)控制。在第一個(gè)時(shí)鐘相位,下方的預(yù)充電晶體管導(dǎo)通,將相等總線拉高。在第二個(gè)時(shí)鐘相位,上方的異或電路被啟用,如果兩個(gè)寄存器不匹配,就將相等總線拉低。同時(shí),CMOS 開(kāi)關(guān)在時(shí)鐘相位 2 導(dǎo)通,將相等總線的值傳遞給鎖存器。“保持器”(keeper)電路會(huì)在相等總線未被顯式拉低時(shí)保持其高電平,以避免相等總線上的電壓緩慢消散的風(fēng)險(xiǎn)。保持器使用一個(gè)弱晶體管,在總線未被激活時(shí)保持其高電平。但如果總線被拉低,保持器晶體管會(huì)被 overpowered 并關(guān)閉。

這是等值比較的輸出電路,該電路位于預(yù)取器右側(cè)

這種動(dòng)態(tài)邏輯降低了功耗和電路尺寸。由于總線在相反的時(shí)鐘相位充電和放電,避免了通過(guò)晶體管的持續(xù)電流(相比之下,像 8086 這樣的 NMOS 處理器可能在總線上使用上拉電阻。當(dāng)總線被拉低時(shí),電流會(huì)流過(guò)上拉和下拉晶體管,這會(huì)增加功耗,使芯片更熱,并限制時(shí)鐘速度) 。

每次預(yù)取后,提前指令取指指針必須遞增,以保存下一條要預(yù)取指令的地址。遞增這個(gè)指針是增量器的工作。(因?yàn)槊看稳≈?nbsp;32 位,所以指針每次遞增 4。但在芯片照片中,你可以看到增量器和限制檢查電路中有一個(gè)缺口,最低兩位的電路被省略了。因此,增量器的電路將其值加 1,這樣指針(附加兩個(gè)零位)就以 4 為步長(zhǎng)遞增。)

構(gòu)建一個(gè)增量器電路很直接,例如,可以使用由 30 個(gè)半加器組成的鏈。但問(wèn)題在于,高速遞增一個(gè) 30 位的值很困難,因?yàn)檫M(jìn)位會(huì)從一個(gè)位位置傳遞到下一個(gè)位位置。這類似于用十進(jìn)制計(jì)算 99999999 + 1;你需要繁瑣地進(jìn)位,進(jìn)位,再進(jìn)位,依此類推,遍歷所有數(shù)字,導(dǎo)致這是一個(gè)緩慢的順序過(guò)程。

增量器采用了一種更快的方法。首先,它幾乎并行地高速計(jì)算所有進(jìn)位。然后,根據(jù)進(jìn)位并行計(jì)算每個(gè)輸出位—— 如果有進(jìn)位進(jìn)入某個(gè)位位置,就翻轉(zhuǎn)該位。

計(jì)算進(jìn)位在概念上很直接:如果值的末尾有一個(gè)由 1 組成的塊,所有這些位都會(huì)產(chǎn)生進(jìn)位,但進(jìn)位會(huì)被最右邊的 0 位阻止。例如,遞增二進(jìn)制數(shù) 11011 會(huì)得到 11100;最后兩位產(chǎn)生進(jìn)位,但零位阻止了進(jìn)位。早在 1959 年,英國(guó)曼徹斯特大學(xué)就開(kāi)發(fā)出了實(shí)現(xiàn)這種功能的電路,被稱為曼徹斯特進(jìn)位鏈(Manchester carry chain)。

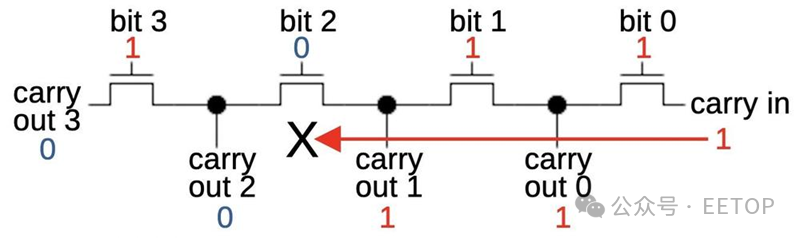

在曼徹斯特進(jìn)位鏈中,為每個(gè)數(shù)據(jù)位構(gòu)建一個(gè)開(kāi)關(guān)鏈,如下所示。對(duì)于 1 位,閉合開(kāi)關(guān);對(duì)于 0 位,打開(kāi)開(kāi)關(guān)(開(kāi)關(guān)由晶體管實(shí)現(xiàn))。為了計(jì)算進(jìn)位,從右側(cè)輸入一個(gè)進(jìn)位信號(hào)。信號(hào)會(huì)通過(guò)閉合的開(kāi)關(guān),直到遇到一個(gè)打開(kāi)的開(kāi)關(guān),然后被阻斷。進(jìn)位鏈上的輸出為我們提供了每個(gè)位置所需的進(jìn)位值。

曼徹斯特進(jìn)位鏈的概念,4 位。

由于曼徹斯特進(jìn)位鏈中的開(kāi)關(guān)都可以并行設(shè)置,且進(jìn)位信號(hào)能高速通過(guò)開(kāi)關(guān),所以這個(gè)電路能快速計(jì)算出我們需要的進(jìn)位。然后,進(jìn)位會(huì)并行翻轉(zhuǎn)相關(guān)的位,比直接使用加法器快得多地得到結(jié)果。

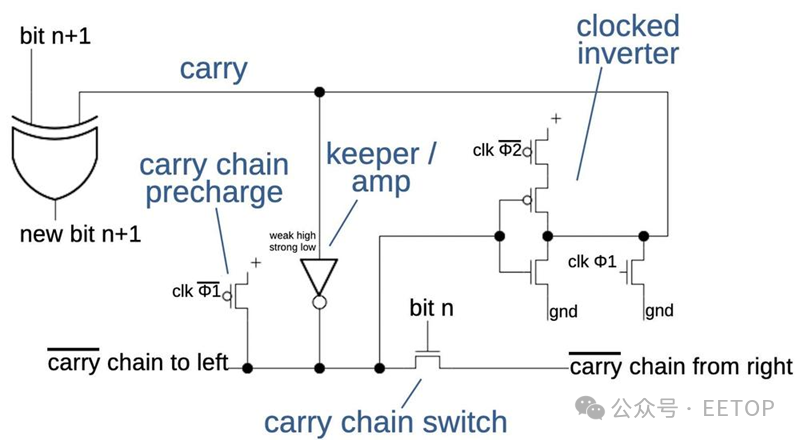

當(dāng)然,在實(shí)際實(shí)現(xiàn)中存在復(fù)雜情況。進(jìn)位鏈中的進(jìn)位信號(hào)是反相的,所以低信號(hào)通過(guò)進(jìn)位鏈傳播以表示進(jìn)位(將信號(hào)拉低比拉高更快)。但在必要時(shí),需要讓線路拉高。與相等電路一樣,解決方案是動(dòng)態(tài)邏輯。也就是說(shuō),進(jìn)位線在一個(gè)時(shí)鐘相位預(yù)充電至高電平,然后在第二個(gè)時(shí)鐘相位進(jìn)行處理,可能會(huì)將線路拉低。

下一個(gè)問(wèn)題是,進(jìn)位信號(hào)在通過(guò)多個(gè)晶體管和長(zhǎng)導(dǎo)線時(shí)會(huì)減弱。解決方案是每個(gè)段都有一個(gè)電路來(lái)放大信號(hào),使用時(shí)鐘控制的反相器和不對(duì)稱反相器。重要的是,這個(gè)放大器不在進(jìn)位鏈路徑中,所以不會(huì)減慢鏈中信號(hào)的速度。

增量器中典型位的曼徹斯特進(jìn)位鏈電路。

上圖展示了增量器中典型位的曼徹斯特進(jìn)位鏈電路實(shí)現(xiàn)。鏈本身在底部,晶體管開(kāi)關(guān)如前所述。在時(shí)鐘相位 1,預(yù)充電晶體管將進(jìn)位鏈的這個(gè)段拉至高電平。在時(shí)鐘相位 2,鏈上的信號(hào)通過(guò)右側(cè)的 “時(shí)鐘控制反相器” 產(chǎn)生本地進(jìn)位信號(hào)。如果有進(jìn)位,下一個(gè)位會(huì)被異或門(mén)翻轉(zhuǎn),產(chǎn)生遞增后的輸出。“保持器 / 放大器” 是一個(gè)不對(duì)稱反相器,產(chǎn)生強(qiáng)低輸出但弱高輸出。當(dāng)沒(méi)有進(jìn)位時(shí),其弱輸出使進(jìn)位鏈保持高電平。但一旦檢測(cè)到進(jìn)位,它會(huì)強(qiáng)烈地將進(jìn)位鏈拉低以增強(qiáng)進(jìn)位信號(hào)。

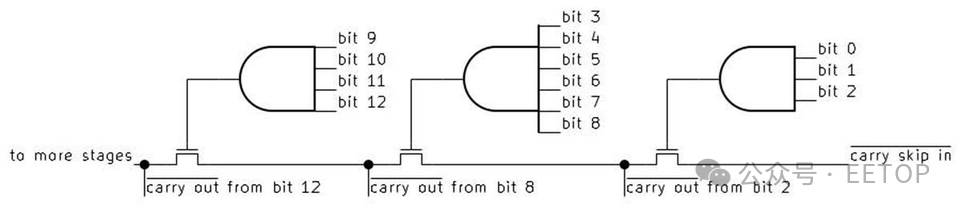

但這個(gè)電路對(duì)于期望的性能來(lái)說(shuō)仍然不夠。增量器并行使用了第二種進(jìn)位技術(shù):進(jìn)位跳躍(carry skip)。其概念是查看位塊,并允許進(jìn)位跳過(guò)整個(gè)塊。下圖展示了進(jìn)位跳躍電路的簡(jiǎn)化實(shí)現(xiàn)。每個(gè)塊由 3 到 6 位組成。如果一個(gè)塊中的所有位都是 1,與門(mén)(AND gate)會(huì)導(dǎo)通進(jìn)位跳躍線中的相關(guān)晶體管。這允許進(jìn)位跳躍信號(hào)以塊為單位(從左到右)傳播。當(dāng)它到達(dá)一個(gè)包含 0 位的塊時(shí),相應(yīng)的晶體管會(huì)關(guān)閉,像在曼徹斯特進(jìn)位鏈中那樣阻止進(jìn)位。與門(mén)都并行工作,所以晶體管會(huì)快速并行導(dǎo)通或關(guān)閉。然后,進(jìn)位跳躍信號(hào)通過(guò)少量晶體管,無(wú)需經(jīng)過(guò)任何邏輯(進(jìn)位跳躍信號(hào)就像一列快車,跳過(guò)大多數(shù)站點(diǎn),而曼徹斯特進(jìn)位鏈?zhǔn)堑剿姓军c(diǎn)的慢車)。與曼徹斯特進(jìn)位鏈一樣,進(jìn)位跳躍的實(shí)現(xiàn)需要在線路上使用預(yù)充電電路、保持器 / 放大器和時(shí)鐘控制邏輯,但我將跳過(guò)細(xì)節(jié)。

一個(gè)抽象且簡(jiǎn)化的進(jìn)位跳躍電路。塊大小與 386 的電路不匹配。

一個(gè)有趣的特點(diǎn)是大型與門(mén)的布局。一個(gè) 6 輸入的與門(mén)是一個(gè)大型器件,難以適配增量器的一個(gè)單元。解決方案是將該門(mén)分散在多個(gè)單元中。具體來(lái)說(shuō),該門(mén)使用標(biāo)準(zhǔn)的 CMOS 與非門(mén)(NAND)電路,NMOS 晶體管串聯(lián),PMOS 晶體管并聯(lián)。每個(gè)單元有一個(gè) NMOS 晶體管和一個(gè) PMOS 晶體管,鏈在末端連接以形成所需的與非門(mén)(對(duì)輸出取反得到所需的與功能)。這種分散的布局技術(shù)不常見(jiàn),但能使每個(gè)位的電路大致保持相同大小。

由于這些技術(shù),增量器電路的逆向工程頗具挑戰(zhàn)性。特別是,預(yù)取器的大部分由一個(gè)電路塊重復(fù) 32 次組成,每個(gè)位對(duì)應(yīng)一次。另一方面,增量器由四個(gè)不同的電路塊組成,以不規(guī)則模式重復(fù)。具體來(lái)說(shuō),一個(gè)塊啟動(dòng)進(jìn)位鏈,第二個(gè)塊繼續(xù)進(jìn)位鏈,第三個(gè)塊結(jié)束進(jìn)位鏈。結(jié)束塊之前的塊不同(一個(gè)大晶體管驅(qū)動(dòng)最后一個(gè)塊),總共有四個(gè)變體。這種不規(guī)則模式在之前的預(yù)取器照片中可見(jiàn)。

預(yù)取器的底部會(huì)根據(jù)需要旋轉(zhuǎn)數(shù)據(jù)以對(duì)齊。與某些處理器不同,x86 不強(qiáng)制要求內(nèi)存訪問(wèn)對(duì)齊。也就是說(shuō),一個(gè) 32 位的值無(wú)需在內(nèi)存中從 4 字節(jié)邊界開(kāi)始。因此,一個(gè) 32 位的值可能會(huì)跨預(yù)取隊(duì)列的兩個(gè) 32 位行拆分存儲(chǔ)。此外,當(dāng)指令解碼器從預(yù)取隊(duì)列中獲取指令的一個(gè)字節(jié)時(shí),該字節(jié)可能在預(yù)取隊(duì)列的任何位置。

為了處理這些問(wèn)題,預(yù)取器包含一個(gè)對(duì)齊網(wǎng)絡(luò),它可以旋轉(zhuǎn)字節(jié),以輸出符合處理器其他部分所需對(duì)齊方式的一個(gè)字節(jié)、字或四個(gè)字節(jié)。

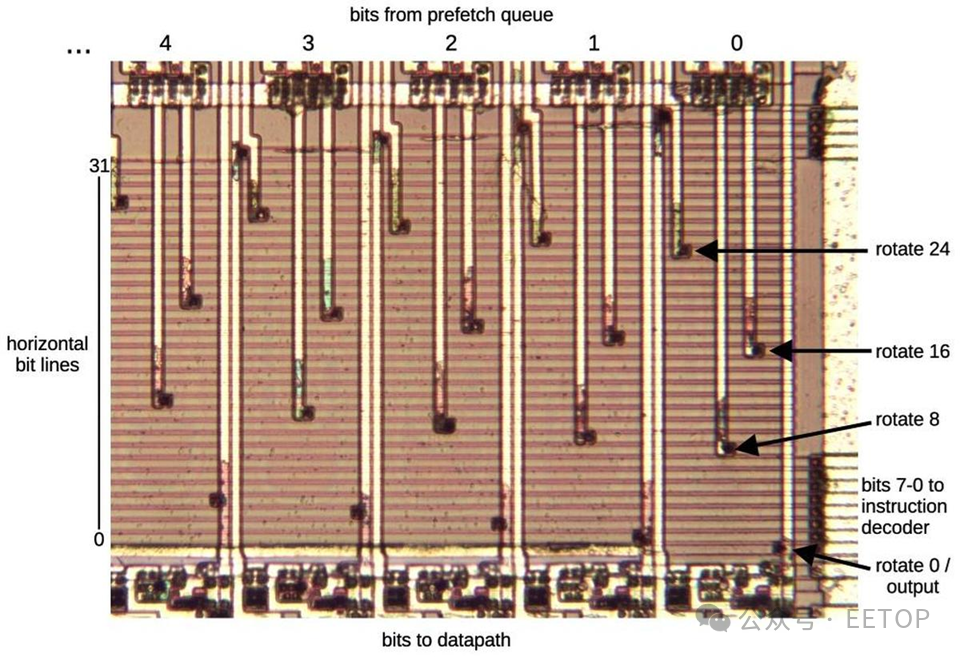

下圖展示了這個(gè)對(duì)齊網(wǎng)絡(luò)的一部分。從預(yù)取隊(duì)列(頂部)輸出的每個(gè)位有四條導(dǎo)線,用于 24 位、16 位、8 位或 0 位旋轉(zhuǎn)。每條旋轉(zhuǎn)導(dǎo)線連接到 32 條水平位線之一。最后,每條水平位線有一個(gè)輸出抽頭,連接到下方的數(shù)據(jù)通路。(垂直線在芯片的下層 M1 金屬層,而水平線在上層 M2 金屬層。為了拍攝這張照片,我移除了 M2 層以顯示下層。原始水平線的陰影仍然可見(jiàn)。 )

對(duì)齊網(wǎng)絡(luò)的一部分。

其原理是,通過(guò)選擇一組垂直旋轉(zhuǎn)線,預(yù)取隊(duì)列的 32 位輸出將向左旋轉(zhuǎn)相應(yīng)的量。例如,要旋轉(zhuǎn) 8 位,位會(huì)通過(guò) “旋轉(zhuǎn) 8” 線向下傳輸。預(yù)取隊(duì)列的位 0 會(huì)激活水平位線 8,位 1 會(huì)激活水平位線 9,依此類推,位 31 會(huì)回繞到水平位線 7。由于水平位線 8 連接到輸出 8,結(jié)果就是位 0 作為位 8 輸出,位 1 作為位 9 輸出,依此類推。

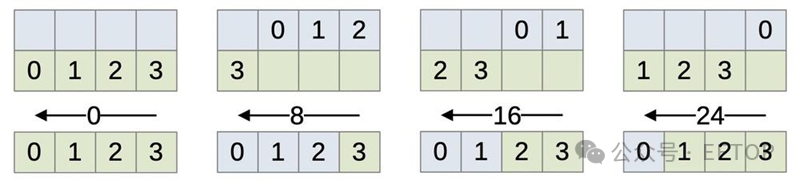

對(duì)齊 32 位值的四種可能性。上方的四個(gè)字節(jié)按指定方式移位,以產(chǎn)生下方所需的輸出。

對(duì)于對(duì)齊過(guò)程,預(yù)取隊(duì)列中一個(gè) 32 位輸出可能會(huì)以四種不同方式跨兩個(gè) 32 位條目拆分存儲(chǔ),如上所示。這些組合由多路復(fù)用器(multiplexers)和驅(qū)動(dòng)器(drivers)實(shí)現(xiàn)。兩個(gè) 32 位多路復(fù)用器選擇預(yù)取隊(duì)列中相關(guān)的兩行(上方的藍(lán)色和綠色)。四個(gè) 32 位驅(qū)動(dòng)器連接到四組垂直線,其中一組驅(qū)動(dòng)器被激活以產(chǎn)生所需的移位。每個(gè)驅(qū)動(dòng)器的每個(gè)字節(jié)都進(jìn)行了布線,以實(shí)現(xiàn)上述對(duì)齊。例如,旋轉(zhuǎn) 8 位的驅(qū)動(dòng)器從 “綠色” 多路復(fù)用器獲取其最高字節(jié),從 “藍(lán)色” 多路復(fù)用器獲取其他三個(gè)字節(jié)。結(jié)果是,跨兩個(gè)隊(duì)列行拆分的四個(gè)字節(jié)被旋轉(zhuǎn),形成一個(gè)對(duì)齊的 32 位值。

最后一個(gè)電路是符號(hào)擴(kuò)展電路。假設(shè)你想將一個(gè) 8 位數(shù)值與一個(gè) 32 位數(shù)值相加。一個(gè)無(wú)符號(hào) 8 位數(shù)值可以通過(guò)簡(jiǎn)單地將高位填充為零來(lái)擴(kuò)展為 32 位。但對(duì)于有符號(hào)數(shù)值來(lái)說(shuō),情況就更復(fù)雜了。例如,-1 的 8 位表示是 0xFF,而其 32 位表示是 0xFFFFFFFF。要將一個(gè) 8 位有符號(hào)數(shù)值轉(zhuǎn)換為 32 位,高 24 位必須用原始數(shù)值的最高位(即符號(hào)位)來(lái)填充。換句話說(shuō),對(duì)于正數(shù),擴(kuò)展位填充為 0;而對(duì)于負(fù)數(shù),擴(kuò)展位填充為 1。這個(gè)過(guò)程就稱為符號(hào)擴(kuò)展。9

在 386 處理器中,預(yù)取器底部的一個(gè)電路負(fù)責(zé)對(duì)指令中的數(shù)值進(jìn)行符號(hào)擴(kuò)展。該電路支持將 8 位數(shù)值擴(kuò)展為 16 位或 32 位,也支持將 16 位數(shù)值擴(kuò)展為 32 位。此電路會(huì)根據(jù)指令的要求,用零或符號(hào)位來(lái)擴(kuò)展數(shù)值。

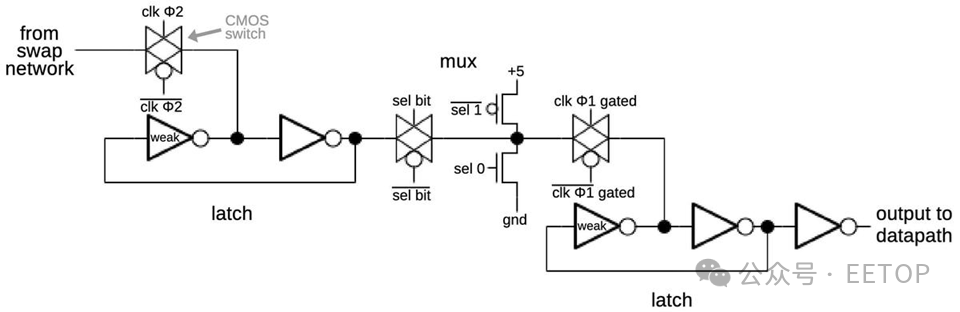

下圖展示了這個(gè)符號(hào)擴(kuò)展電路的一個(gè)位的結(jié)構(gòu)。它由左側(cè)和右側(cè)的鎖存器以及中間的多路復(fù)用器組成。鎖存器是采用標(biāo)準(zhǔn)的 386 電路,通過(guò) CMOS 開(kāi)關(guān)構(gòu)建而成(參見(jiàn)腳注)。7 多路復(fù)用器從三個(gè)值中選擇一個(gè):來(lái)自交換網(wǎng)絡(luò)的位值、用于符號(hào)擴(kuò)展的 0,或用于符號(hào)擴(kuò)展的 1。如果選擇位值,多路復(fù)用器由 CMOS 開(kāi)關(guān)構(gòu)成;若選擇 0 或 1 值,則由兩個(gè)晶體管構(gòu)成。這個(gè)電路被復(fù)制了 32 次,但最低字節(jié)只包含鎖存器,沒(méi)有多路復(fù)用器,因?yàn)榉?hào)擴(kuò)展不會(huì)修改最低字節(jié)。

預(yù)取器中與 31-8 位相關(guān)的符號(hào)擴(kuò)展電路。

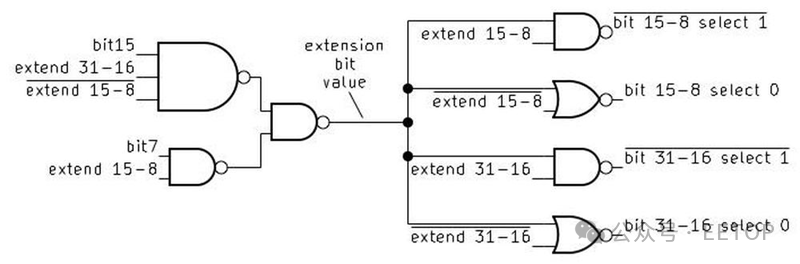

符號(hào)擴(kuò)展電路的第二部分用于確定這些位應(yīng)該填充 0 還是 1,并將控制信號(hào)發(fā)送給上面的電路。左側(cè)的門(mén)電路確定符號(hào)擴(kuò)展位應(yīng)該是 0 還是 1。對(duì)于 16 位符號(hào)擴(kuò)展,該位來(lái)自數(shù)據(jù)的第 15 位;而對(duì)于 8 位符號(hào)擴(kuò)展,該位來(lái)自第 7 位。右側(cè)的四個(gè)門(mén)電路生成用于每個(gè)位的符號(hào)擴(kuò)展信號(hào),分別為 31-16 位范圍和 15-8 位范圍產(chǎn)生獨(dú)立的信號(hào)。

該電路確定哪些位應(yīng)該填充 0 或 1。

這個(gè)電路在芯片上的布局有些不同尋常。預(yù)取器的大部分電路由 32 個(gè)相同的列組成,每列對(duì)應(yīng)一個(gè)位。8 上面描述的電路只實(shí)現(xiàn)了一次,使用了大約 16 個(gè)門(mén)電路(未顯示緩沖器和反相器)。盡管如此,該電路被擠在第 17 位到第 7 位的位置,導(dǎo)致布局出現(xiàn)了不規(guī)則性。此外,與 386 處理器的其他部分相比,該電路在硅片上的實(shí)現(xiàn)方式也很特別。386 的大部分電路使用兩層金屬進(jìn)行互連,盡量減少多晶硅布線的使用。然而,上面提到的這個(gè)電路還使用了長(zhǎng)段的多晶硅來(lái)連接各個(gè)門(mén)電路。

符號(hào)擴(kuò)展電路的布局。該電路位于預(yù)取隊(duì)列的底部。

指令在芯片中的傳輸路徑

指令在 386 芯片中的傳輸路徑曲折復(fù)雜。首先,右上角的總線接口單元從內(nèi)存中讀取指令,并通過(guò) 32 位總線(藍(lán)色)將其發(fā)送到預(yù)取單元。預(yù)取單元將指令存儲(chǔ)在 16 字節(jié)的預(yù)取隊(duì)列中。

指令在預(yù)取隊(duì)列中進(jìn)進(jìn)出出,路徑曲折。

如何從預(yù)取隊(duì)列中執(zhí)行一條指令呢?事實(shí)證明,這有兩條不同的路徑。假設(shè)你要執(zhí)行一條將 12345678 加到 EAX 寄存器的指令。預(yù)取隊(duì)列中會(huì)存放五個(gè)字節(jié):05(操作碼)、78、56、34 和 12。預(yù)取隊(duì)列通過(guò) 8 位總線(紅色)將操作碼逐個(gè)字節(jié)地提供給解碼器。該總線從預(yù)取隊(duì)列的對(duì)齊網(wǎng)絡(luò)中取出最低 8 位,并將該字節(jié)發(fā)送到一個(gè)緩沖器(紅色箭頭頭部的小方塊)。操作碼再?gòu)倪@里傳輸?shù)街噶罱獯a器。10 指令解碼器反過(guò)來(lái)使用大型查找表(PLA)將 x86 指令轉(zhuǎn)換為包含 19 個(gè)不同字段的 111 位內(nèi)部格式。

另一方面,指令的數(shù)據(jù)字節(jié)通過(guò) 32 位數(shù)據(jù)總線(橙色)從預(yù)取隊(duì)列傳輸?shù)剿阈g(shù)邏輯單元(ALU)。與前面提到的總線不同,這條數(shù)據(jù)總線分布較廣,每條線貫穿數(shù)據(jù)通路的每一列。因此,數(shù)據(jù)也可以存儲(chǔ)到寄存器中。例如,MOV(移動(dòng))指令可以將指令中的一個(gè)值(即 “立即數(shù)”)存儲(chǔ)到寄存器中。

386 處理器的預(yù)取隊(duì)列包含約 7400 個(gè)晶體管,比整個(gè)英特爾 8080 處理器的晶體管數(shù)量還多(而且這還只是隊(duì)列本身,不包括預(yù)取控制邏輯)。這體現(xiàn)了處理器技術(shù)的飛速發(fā)展:386 中一個(gè)功能單元的一部分所包含的晶體管數(shù)量,就超過(guò)了 11 年前的整個(gè) 8080 處理器。而這個(gè)單元還不到整個(gè) 386 處理器的 3%。

每次觀察 x86 電路時(shí),我都能看到為支持向后兼容所付出的復(fù)雜性,也更能理解為什么精簡(jiǎn)指令集計(jì)算機(jī)(RISC)會(huì)流行起來(lái)。預(yù)取器也不例外。其復(fù)雜性在很大程度上源于 386 對(duì)未對(duì)齊內(nèi)存訪問(wèn)的支持,這需要一個(gè)字節(jié)移位網(wǎng)絡(luò)來(lái)將字節(jié)調(diào)整到 32 位對(duì)齊狀態(tài)。此外,在指令總線的另一端是復(fù)雜的指令解碼器,用于解碼復(fù)雜的 x86 指令。而解碼 RISC 指令則要簡(jiǎn)單得多。

無(wú)論如何,希望你能對(duì)預(yù)取電路的介紹感興趣。我計(jì)劃撰寫(xiě)更多關(guān)于 386 的內(nèi)容,所以請(qǐng)?jiān)?Bluesky(@righto.com)上關(guān)注我,或通過(guò) RSS 獲取更新。我之前已經(jīng)寫(xiě)過(guò)多篇關(guān)于 386 的文章,一個(gè)不錯(cuò)的起點(diǎn)可能是我對(duì) 386 芯片的綜述。

原文:https://www.righto.com/

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章