Hot Chips 2023 :世界首顆面向數據中心的RISC-V 處理器,每周期可解碼8條指令

2023-09-12 12:34:39 EETOPHot chips的全稱是A Symposium on High Performance Chips,于每年八月份在斯坦福大學舉行。不同于其他行業會議以學術研究為主,HotChips是一場產業界的盛會,各大處理器公司會在每年的會上展現他們最新的產品以及在研的產品。

我們不但看到了來自英特爾、AMD、Arm這些傳統處理器巨頭的展示,還看到了存儲雙雄三星和SK海力士的分享。此外,RISC-V服務器芯片新貴Ventana也在本屆大會上分享了公司Veyron V1的細節。

Ventana Veyron V1 被認為是首款面向數據中心的RISC-V處理器。接下來讓我們看看該款處理器有何過人之處。

以下內容來源于中國臺灣媒體科技新報,作者:癡漢水球

處理器業界一直有一種觀點:Arm 是下個RISC / Unix 服務器,而RISC-V 是下個Arm(Arm Is The New RISC / Unix,RISC-V Is The New Arm)。

云端巨頭紛紛自行打造處理器,繼Calxeda、Applied Micro、AMD、Marvell、Nvidia和三星等制造Arm服務器芯片的第一波嘗試,博通(Broadcom)、高通(Qualcomm)和Nuvia第二波努力,Arm指令集兼容處理器由AWS自研Graviton和Arm推出Neoverse引領第三波浪潮, 終于沖破數據中心大門。

對嶄新工作覆載,云端巨頭也沒有「非 x86 不可」需求,同等性能的云端實例(Cloud Instance),相較 x86,Arm 也有 30%~40% 性價比優勢,注定 Arm 成為超大規模云服務的首選。

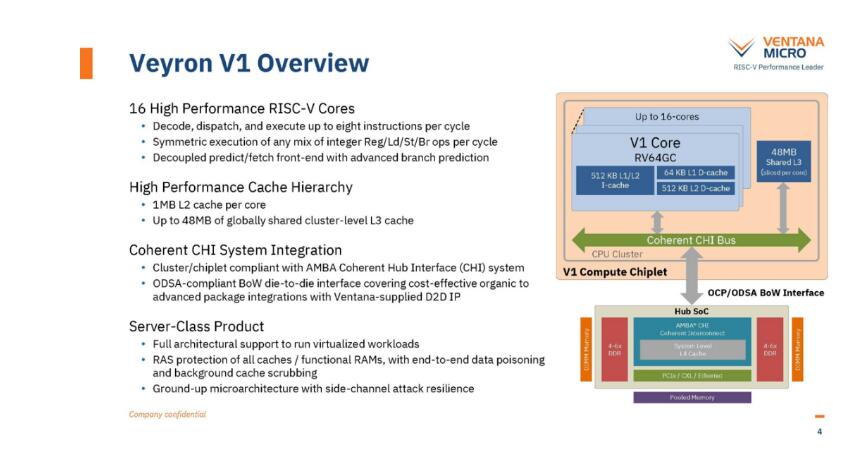

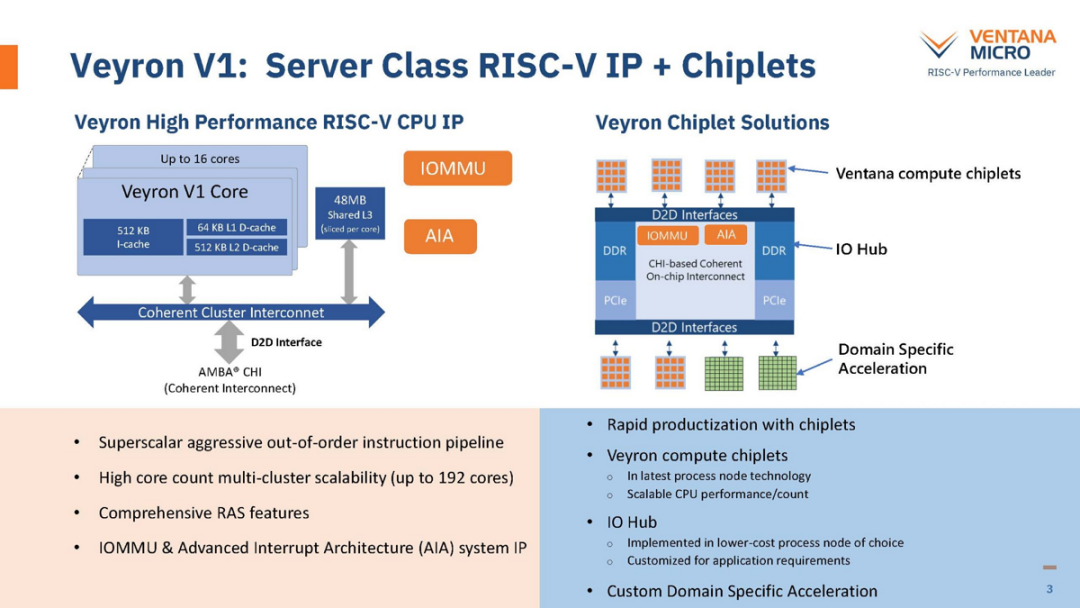

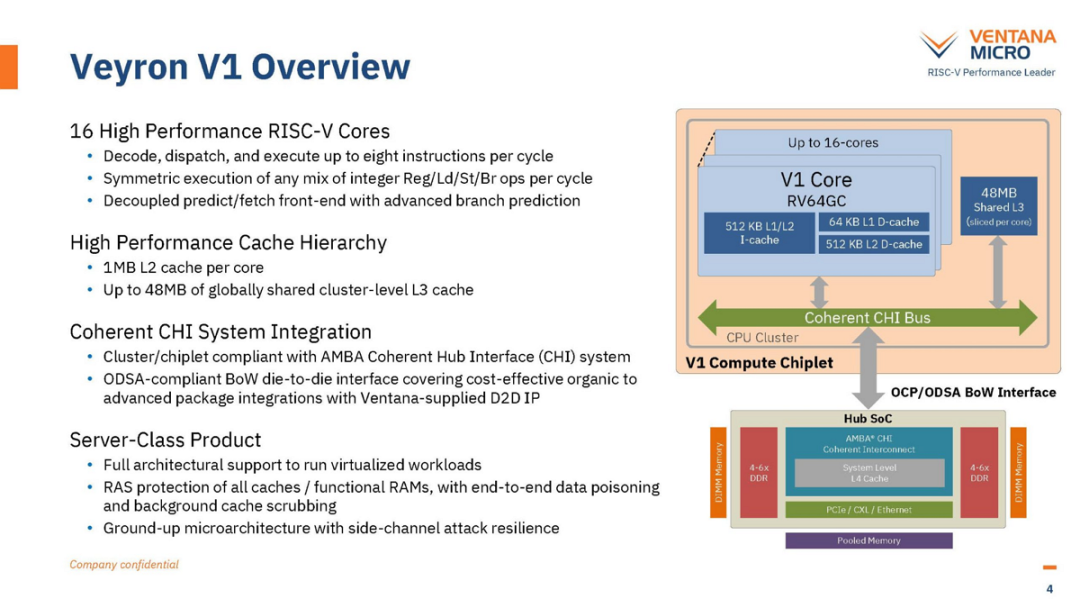

▲ 兼容 RISC-V 指令集的 Veyron V1 是首款「數據中心等級」RISC-V 處理器。 分別掌握移動平臺和高效能運算市場的Arm與x86,近來因自由度極高崛起的RISC-V多半用于低功耗嵌入式平臺,但也不乏企圖將RISC-V推入數據中心的公司。新創Ventana Microsystems 2022年12月發布兼容64位RISC-V指令集的Veyron V1處理器,采用類AMD EPYC的Chiplet設計,允許客戶購買CPU模組和I/O Hub(含存儲器控制器和PCIe),最多可擴展到192個核心(12個CPU模組),然后整合自己的加速器,實作出一顆完整芯片。

▲ 對還不知道客戶在哪里的新創公司,目標不外乎有講跟沒講一樣的「只要我們能找到需求」。

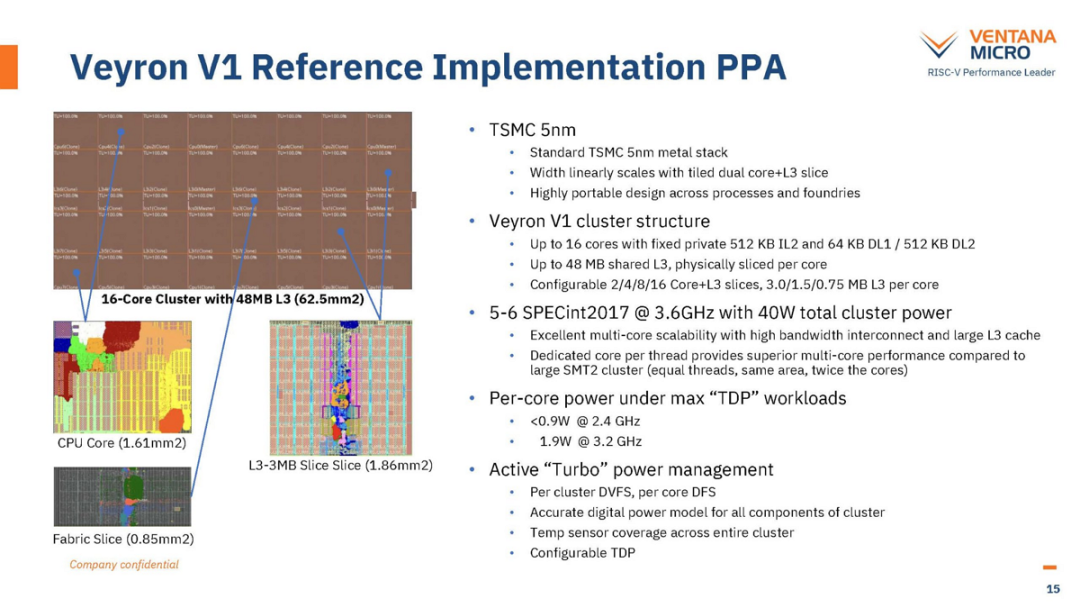

▲ 一個Veyron V1處理器CPU Chiplet含16個核心(臺積電5納米),接著跟有DDR內存控制器和PCIe等功能的I/O Hub(推測是臺積電6納米)結合,最多可延展至192個核心,并整合特定領域加速器。

▲ 更多Veyron V1處理器關鍵規格:每個時鐘周期最多可解碼8個指令、每個核心有1MB L2快取,全部核心共享的L3快取最高容量48MB,服務器該有的特性如虛擬化、內存數據保護、和防御旁路攻擊(Side-band Attack)等。

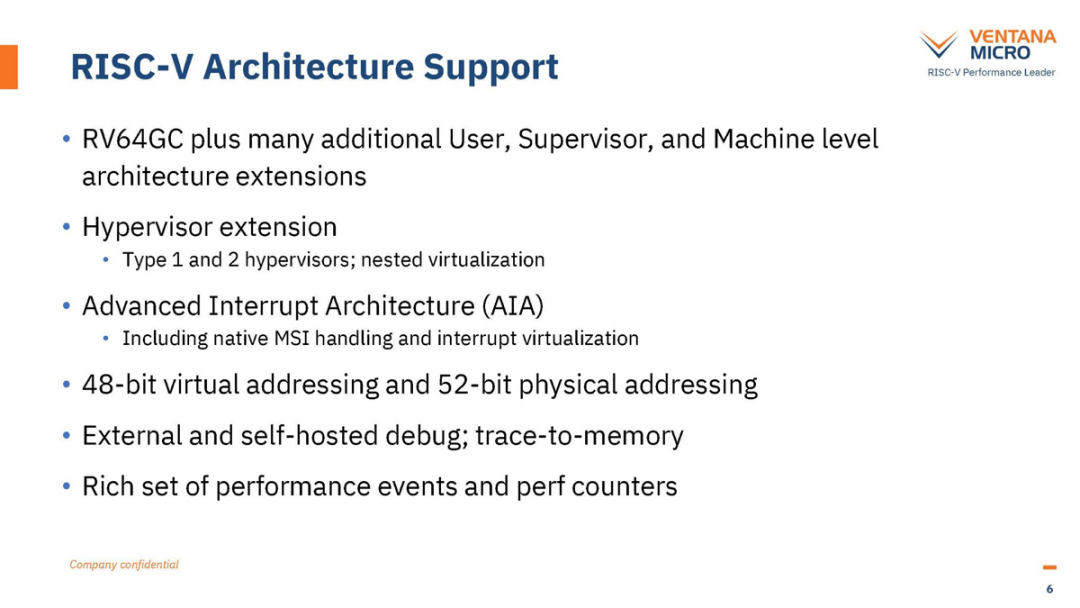

▲ 對應指令集以 RV64GC(意指 RISC-V 64-bit, extensions G and C) 為基礎再延伸。讓人訝異的是,Veyron V1 支持「可在虛擬機架設虛擬機器」的巢狀虛擬化(Nested Virtualization),這個連 Arm Neoverse N1 都做不到。

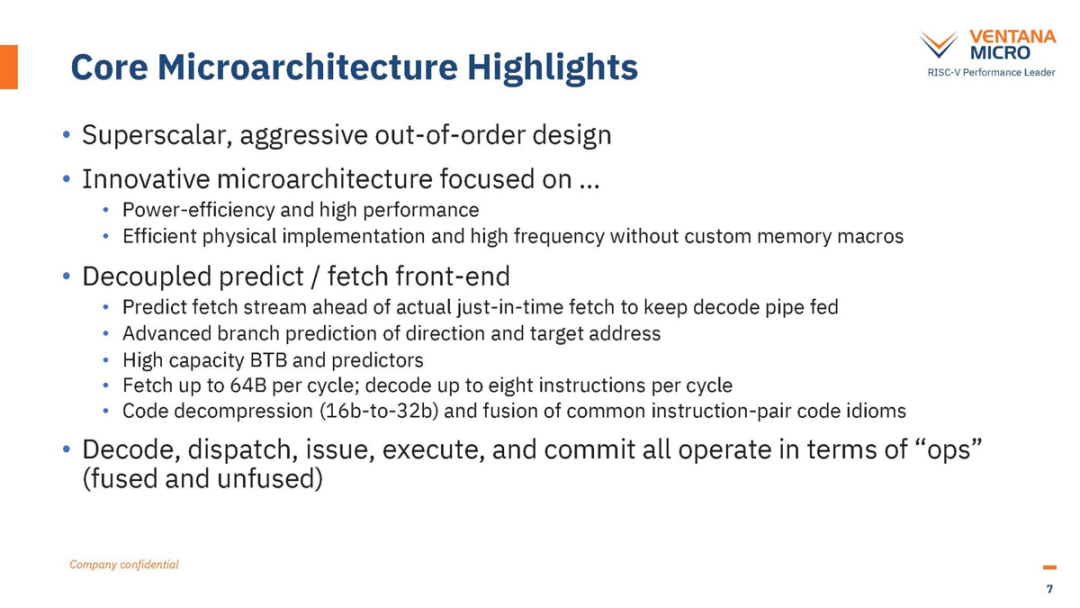

▲ Veyron V1 核心微架構的相關細節,但說穿了跟其他高效能處理器如出一轍,像追求能效、與指令管線解耦的分支預測與指令擷取、執行單元將部份相連指令融合為單一運算等。

RFQZnpKAJ5eztOrzTCHa7OvwgjA/640?wx_fmt=png" data-w="1080" data-index="8" src="http://www.xebio.com.cn/uploadfile/2023/0912/20230912123539468.jpg" _width="100%" crossorigin="anonymous" alt="圖片" data-fail="0" style="margin: 0px; padding: 0px; outline: 0px; max-width: 100%; box-sizing: border-box; overflow-wrap: break-word !important; vertical-align: middle; height: auto !important; width: 677px; visibility: visible !important;"/>

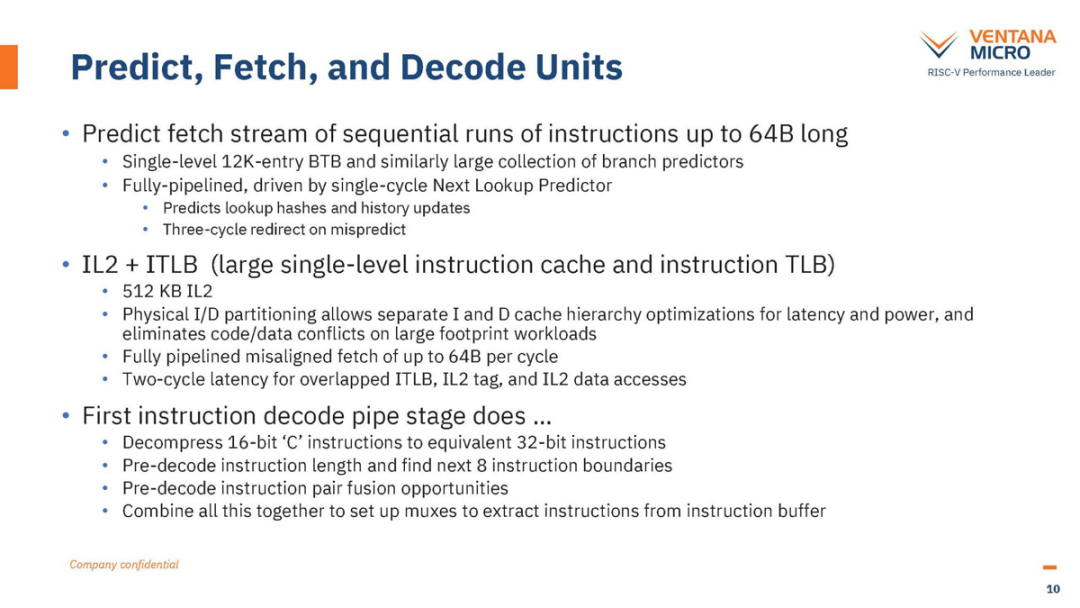

▲ Veyron V1 指令快取頗具特色:充當 L1 / L2 大型化 512kB 指令快取,搭配一塊當指令循環緩沖區(Loop Buffer)的超小型 L0 快取。

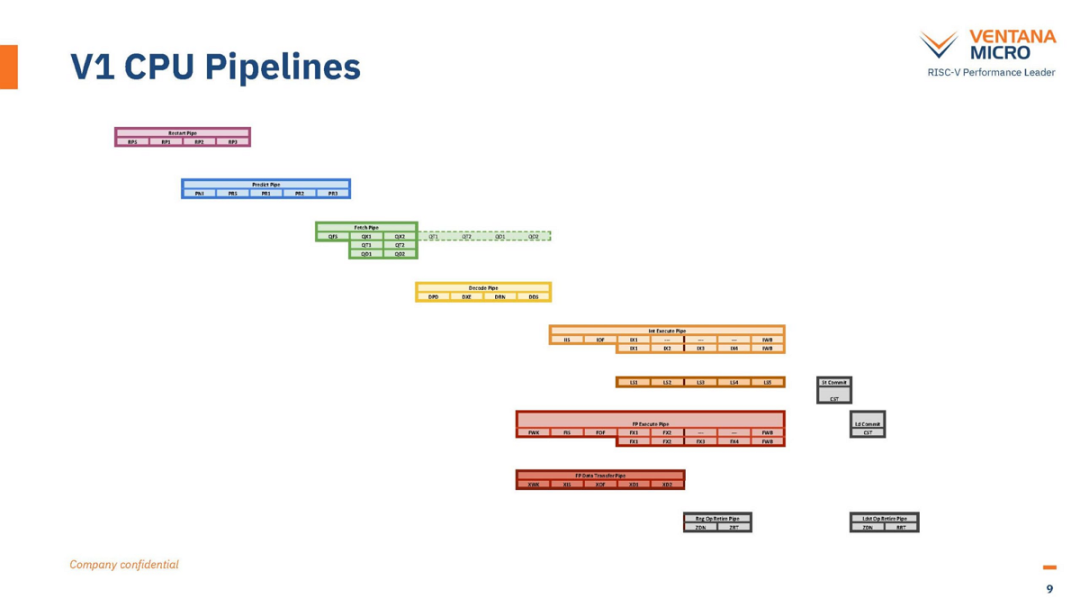

▲ Veyron V1 指令流水線全貌,坦白講,畫成這樣的確很難理解。

▲ Veyron V1 為了確保每時鐘周期可擷取并解碼 8 個指令,從分支預測、指令快取、指令 TLB、指令擷取到指令預先解碼,都要有因應配套措施。

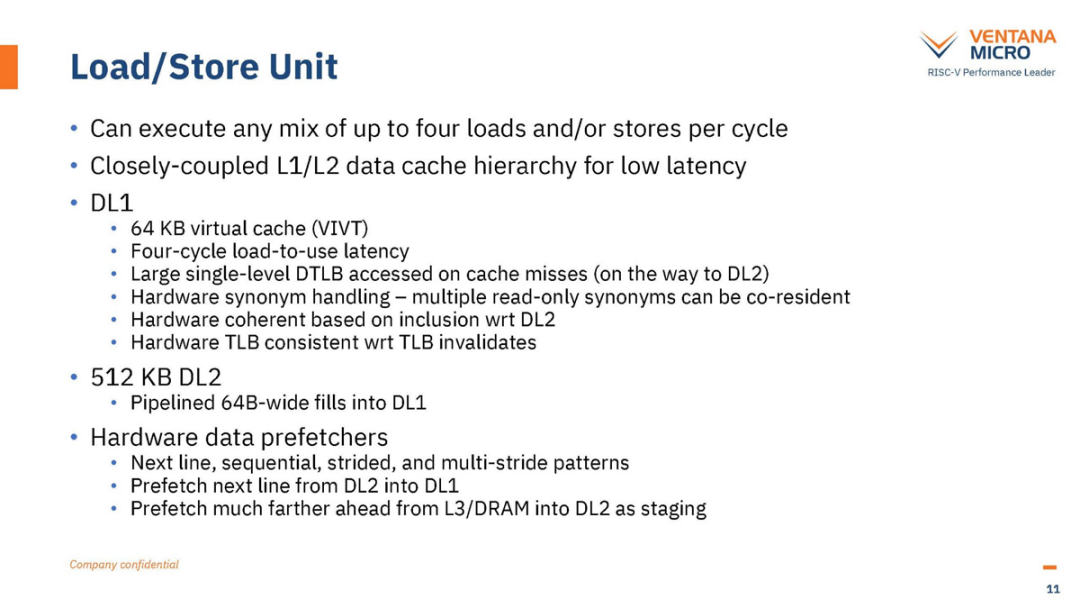

▲ Veyron V1 內存加載和回存單元,每時鐘周期可同時執行總計四個加載/回存。

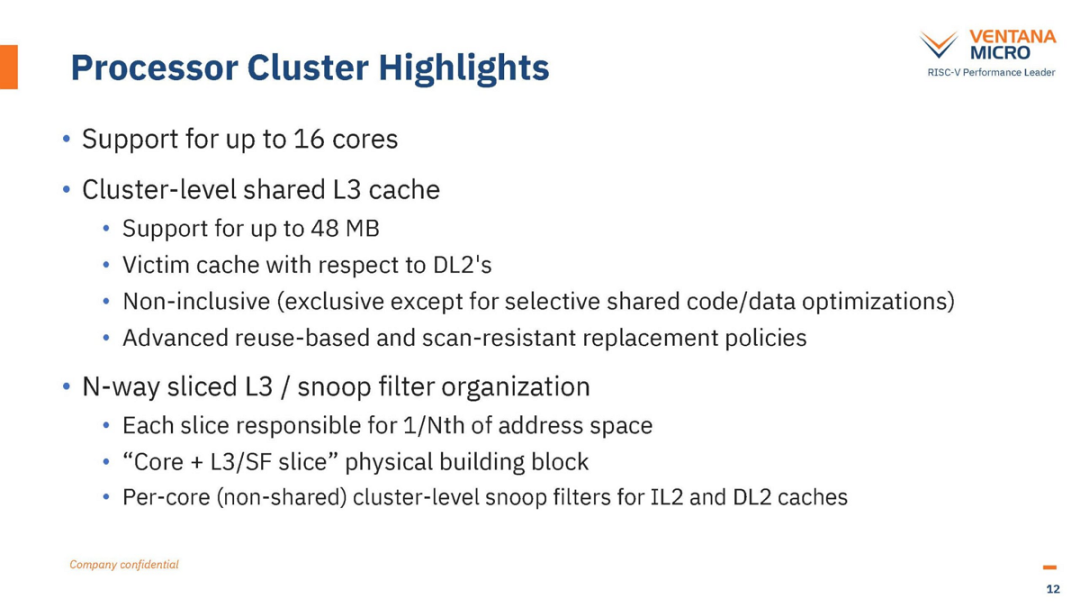

▲ Veyron V1 單一 CPU 模組最多 16 核,L3 快取最高容量是48MB,并兼具快取數據一致性協議的窺探過濾器(Snoop Filter)角色。

▲ Veyron V1 打從一開始就走 Chiplet 路線,兼容 Arm 制定的 AMBA CHI(Coherent Hub Interface)接口。

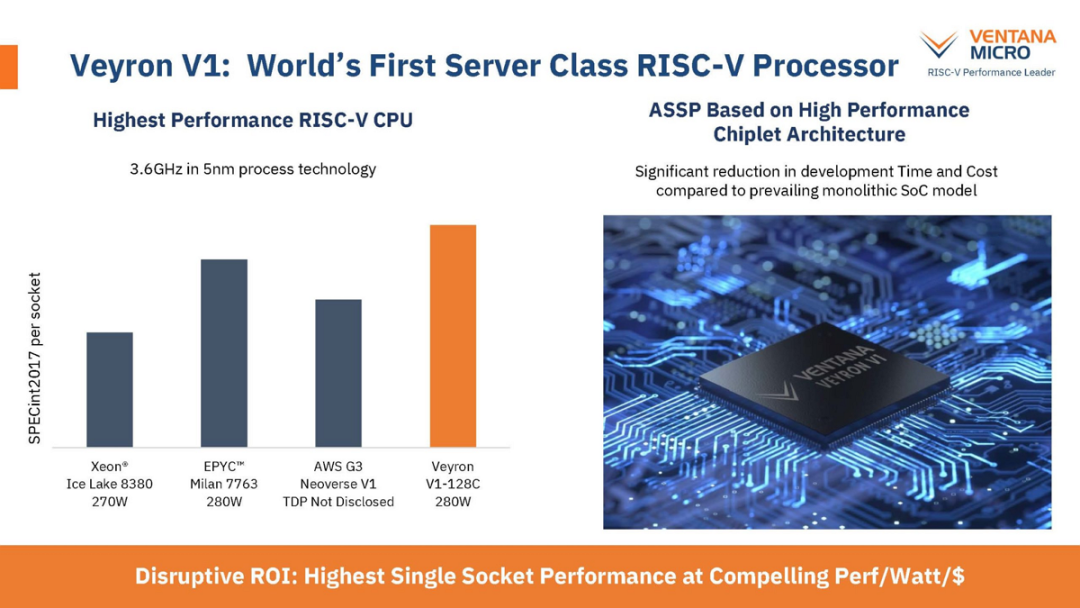

▲ 128核Veyron V1,主頻為3.6GHz、功耗280W時,性能可超越40核英特爾Xeon8380、64核AMD EPYC7763和64核AWS Graviton3,但能否抗衡英特爾第四代Xeon-SP和AMD第四代EPYC就有點存疑。

▲ Veyron V1的CPU模組使用臺積電5納米制程參考實作:16核心結合48MB L3快取內存(每核心3MB),耗電量約 40W。 但有件事不得不提:Veyron V1 看來并沒有 SIMD 或向量執行單元,這對上有 AVX-512 的 AMD Zen 4c 會非常吃虧。 至于「RISC-V進軍數據中心」,Ventana Microsystems 的Veyron V1處理器可謂開了第一槍,但缺乏矢量運算能力的Veyron V1,追求吞吐量應用(如視訊編碼器和繪圖相關)會非常吃虧,即便下一版Veyron V2補回,RISC-V生態系統依然遠不如Arm和x86成熟,必須另外編寫軟件支持向量擴展。以前Arm試圖將自己塑照成x86替代品的過程,就多次面臨軟件支援難題,RISC-V只會面對更艱巨的挑戰。 Ventana Microsystems計劃是,客戶應能在第二季或第三季收到Veyron V1處理器樣品,屆時就能知道世界首顆數據中心等級RISC-V處理器,究竟有多大能耐。