聯(lián)發(fā)科:為何要開發(fā)10核移動(dòng)SoC

2015-07-03 16:11:21 未知聯(lián)發(fā)科于2015年5月發(fā)布了集成有10個(gè)64位ARM內(nèi)核的移動(dòng)產(chǎn)品用應(yīng)用處理SoC“Helio X20”。聯(lián)發(fā)科設(shè)計(jì)技術(shù)部副總經(jīng)理Denny Liu通過演講介紹了這款SoC的開發(fā)過程。

《日經(jīng)電子》拍攝。

Denny Liu是在新思科技、ARM、臺(tái)積電借第五十二屆設(shè)計(jì)自動(dòng)化會(huì)議之機(jī),于2015年6月8日聯(lián)合舉辦的“Collaborating to Enable Design with 16-nm and 10-nm FinFET”上發(fā)表的演講(圖1),題目是“Power Scalability : from System to Silicon”。

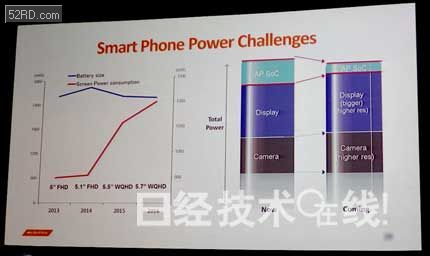

Denny Liu稱,最近的智能手機(jī)屏幕越來越大,分辨率越來越高,攝像頭的像素越來越高,同時(shí)外殼越來越薄,電池容量趨于減小(圖2)。

聯(lián)發(fā)科的幻燈片。

負(fù)責(zé)應(yīng)用處理的SoC也受到了智能手機(jī)這一發(fā)展趨勢的影響。聯(lián)發(fā)科的當(dāng)務(wù)之急是開發(fā)比現(xiàn)有應(yīng)用處理SoC功耗更低的芯片。不過,只是商品目錄中功耗值低的芯片還不行,要開發(fā)出智能手機(jī)用戶實(shí)際使用時(shí)能延長續(xù)航時(shí)間的應(yīng)用處理SoC。

3種CPU內(nèi)核群

因此,聯(lián)發(fā)科按照功耗和性能將智能手機(jī)使用的應(yīng)用分成了三類(圖3)。顯示待機(jī)畫面、電子郵件、使用SNS(Facebook等)發(fā)送信息等屬于“輕度處理”,瀏覽網(wǎng)頁、滾動(dòng)SNS屏幕、播放音樂/錄音等屬于“中度處理”,運(yùn)行游戲、圖像處理相關(guān)應(yīng)用等屬于“重度處理”。

聯(lián)發(fā)科的幻燈片。

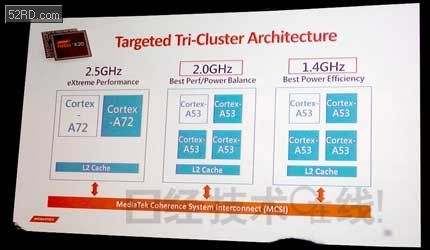

Helio X20在基本架構(gòu)上為這三種處理負(fù)荷分別準(zhǔn)備了CPU內(nèi)核群(圖4)。輕度處理用內(nèi)核群由4個(gè)“ARM Cortex-A53”構(gòu)成,工作頻率為1.4GHz。中度處理用內(nèi)核群同樣由4個(gè)Cortex-A53構(gòu)成,但工作頻率稍高,為2.0GHz。重度處理采用了2個(gè)比Cortex-A53性能高的“ARM Cortex-A72”,工作頻率為2.5GHz。

聯(lián)發(fā)科的幻燈片。

功耗降低30%

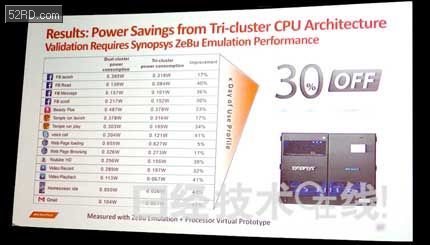

之所以采用三集群(Tri-Cluster)架構(gòu)而非通常的雙集群(Dual Cluster),是為了更加高效地節(jié)能。三種內(nèi)核群中,用于中度處理的內(nèi)核群非常重要。聯(lián)發(fā)科利用新思科技的邏輯模擬器“ZeBu”,證實(shí)了三集群架構(gòu)的效果(圖5)。

聯(lián)發(fā)科的幻燈片。

測試參考了某智能手機(jī)用戶的應(yīng)用案例,按照應(yīng)用,調(diào)查了三集群與雙集群架構(gòu)之間功耗的差異。采用三集群后各個(gè)應(yīng)用的功耗有了幅度不同的下降,綜合來看,功耗降低了30%(圖6)。

聯(lián)發(fā)科的幻燈片。

利用IC Compiler II

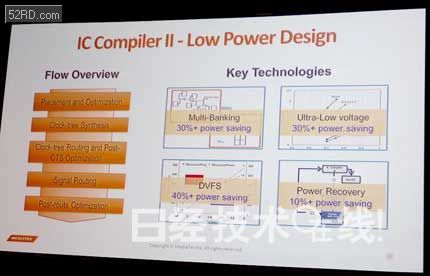

Helio X20的布局設(shè)計(jì)采用了新思科技的自動(dòng)布局設(shè)計(jì)工具“IC Compiler II”(圖7)。使用該工具,在多存儲(chǔ)體、低壓工作、DVSF、電源供應(yīng)等方面容易降低功耗。另外,還有報(bào)告稱,IC Compiler II的處理時(shí)間比上代產(chǎn)品“IC Compiler I”更短,能縮短芯片開發(fā)時(shí)間。聯(lián)發(fā)科稱,IC Compiler II的處理速度是IC Compiler I的5倍。

聯(lián)發(fā)科的幻燈片。

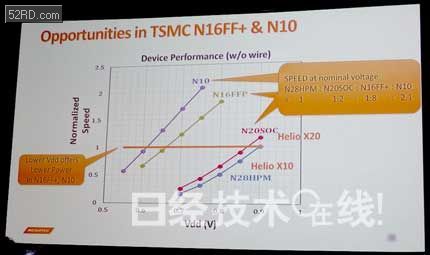

Denny Liu在演講中還展示了臺(tái)積電微細(xì)工藝的效果。Helio X20采用臺(tái)積電的20nm工藝(N20SOC)制造。據(jù)介紹,與28nmHPM工藝(Helio X10采用的制造工藝)相比,N20SOC的速度是其1.2倍,16nm FinFET+工藝的速度是其1.8倍,10nm FinFET工藝的速度是其2.1倍(圖8)。另外,在相同速度下,采用16nm FinFET+和10nm FinFET工藝能夠降低電源電壓,因此可以降低功耗。

聯(lián)發(fā)科的幻燈片。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章