摩爾定律死不死?

2019-12-05 12:51:51 金捷幡2018年是英特爾悲哀的一年。就在公司50周年大慶前一個月,擠了五年牙膏的CEO柯再奇因桃色事件辭職。

外界猜測,這只是董事會找的一個小借口干掉他,因為本身這個戀情微不足道。

最關鍵的是,柯再奇簡直就是摩爾定律的反義詞。在他任內,從14nm到14nm+++尷尬無比。而摩爾定律就是英特爾的基本法。

2018年,在半導體制程技術上曾遙遙領先半個世紀的英特爾被臺積電反超。老陪襯AMD的RyZen居然在也迎頭趕上。

Nvidia的黃仁勛說,摩爾定律已經死啦。一代巨擎Risc先驅David Patterson也說摩爾定律死了。

這幾乎等于說,英特爾存在的意義消失了。一個科技界的指路明燈變成了一個普通的賺錢機器。

一

如果單看英特爾的財報,總體來說還是不錯的。雖然在新產品上捉襟見肘,但是搭著云計算強勁的東風,英特爾的CPU還是供不應求。

如果時光倒流到十多年前,英特爾一定后悔兩次拒絕蘋果的日子。因為蘋果培養了它的兩大對手:三星和臺積電。

在iPhone第一代發布前一年,英特爾拒絕了為喬布斯提供手機CPU并賣掉了自己的ARM分部XScale。蘋果選擇了三星。

2012-2013年,蘋果為了去三星化尋求iPhone 5s的A7處理器代工廠。傳聞中的候選人英特爾卻沒有接,臺積電當時也沒準備好接這么大的單子。

又在三星忍了一年的蘋果,砸巨資投向臺積電,終于實現了20nm A8的量產。當年英特爾已經開始量產14nm,領先臺積電1-1.5代。蘋果對CPU性能的圖騰式要求倒逼了臺積電的一路狂奔。

半導體先進制程需要太多資金的投入,蘋果這個大客戶的驅動終于給臺積電井噴的動力,并在7nm站到巔峰。而格芯很明顯是先進制程客戶太少,導致沒有錢繼續軍備競賽。

二

事后諸葛亮是沒有意義的,錯誤誰都犯過:喬布斯當年也清倉過ARM的股票,微軟也清倉過蘋果的股票。

我們八卦了半天,還是要回到摩爾定律這個話題。

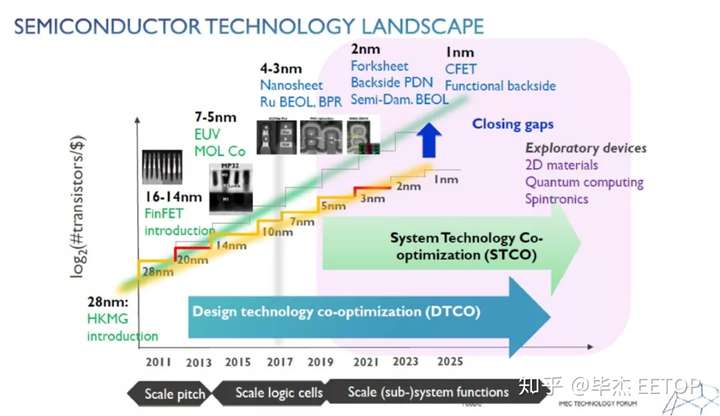

在英特爾燈塔暗淡的同時,大洋彼岸的比利時小鎮魯汶則熠熠生輝。下圖是IMEC最新路線圖,1nm已經正式出場。其實IMEC數年前就對此堅信不疑,而英特爾的Roadmap早就淪為平庸。

(Photo Credit: IMEC)

IMEC是尖端技術回歸歐洲的一個象征。作為ASML的鐵桿盟友并部署了最新NXE3400系列EUV的半導體研究重鎮,IMEC也是High NA EUV的原型機聯合研發合作伙伴。因此IMEC是最有底氣說,它在真機上實現了1~3nm技術。

下圖是ASML的路線圖。由于High NA EUV已經設計完成,所以從光刻角度認為至少未來十年摩爾定律還在掌握之中。

(Photo Credit: ASML)

下圖是High NA超凈室里的巨型光學測量真空倉和巨大的EUV反射鏡機械手。

(Photo Credit: ASML)

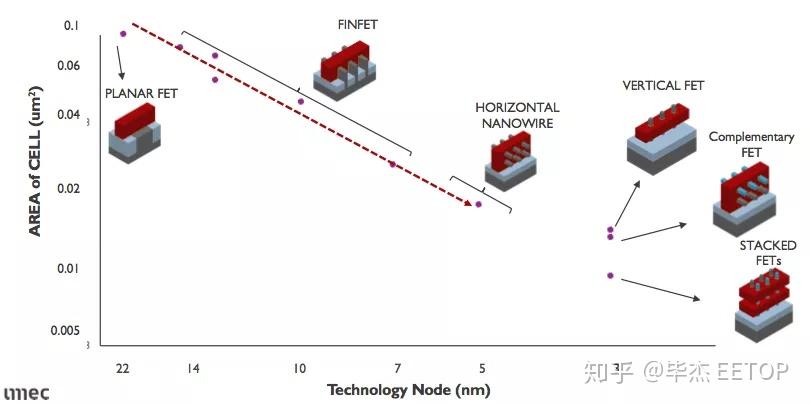

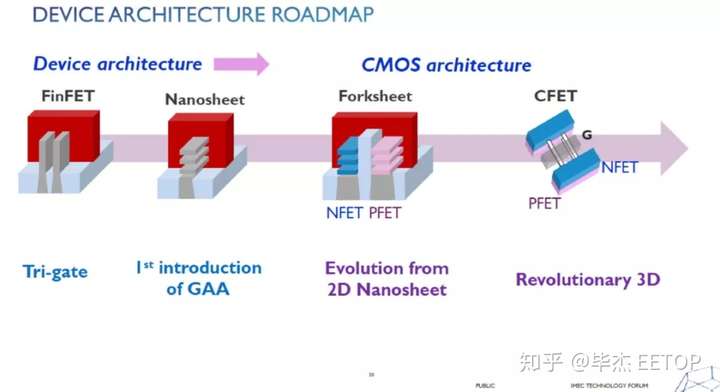

IMEC認為,超越5nm以后,晶體管Cell的模式可能是各種形狀的FET管子。

(Photo Credit: IMEC)

有沒有越來越像樂高積木的感覺,接下來粗淺解釋一下一些基礎知識。

三

首先,有人會質疑道:原子直徑才0.1nm(1 Å),怎么可能把這么復雜的晶體管做到1nm。

確實如此。目前所謂制程技術或技術節點多少nm,并不是晶體管做到這么小了。

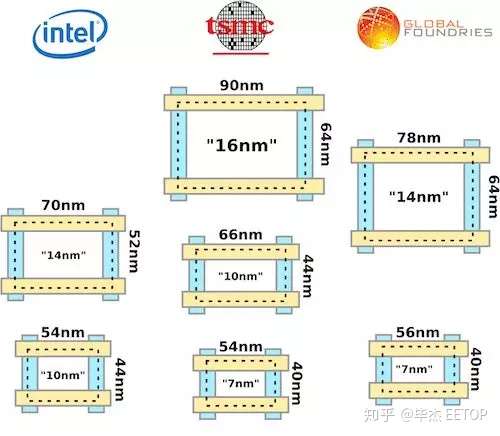

早期晶體管的縮小都是類似二維的,為了達到摩爾定律,長寬各縮小到0.7倍則面積縮小近一半(0.7x0.7=0.5)。傳統ITRS定義技術節點是最小金屬間距(MMP,即下圖藍色那根)的一半。但到了20/22nm引入FinFET以后,MMP的減少開始變得很慢,但是因為3D化后晶體管數量仍舊激增,廠商再用1/2MMP就顯示不出來技術進步了。因此各家的命名就開始亂了起來:

20nm x0.7=14nm,所以新一代叫14nm

14nm x0.7=9.8nm, 所以再新一代叫10nm

10nm x0.7=7nm, 所以下一代叫7nm

7nm x0.7=4.9nm, 所以再下一代叫5nm

(請注意,上面這些0.7并未真正物理出現,只是假想如果二維縮小0.7而已。實際上看下圖臺積電10nm到7nm,MMP距離只是從42/44nm降到40nm)

(Photo Credit: WikiChip)

從上圖看,英特爾的10nm和臺積電的7nm平面基礎尺寸是近似的。為了對比技術差距,單位面積的晶體管數成為一個好方法。據分析數據,兩者每平方毫米都是一億個晶體管左右。但臺積電早已量產(麒麟980/990,A12/A13,AMD Ryzen 3000等),但英特爾多年還是搞不定良率問題。

四

有專家猜測,英特爾10nm碰到的問題可能和它家激進地把導體從銅全面轉到鈷有關,而臺積電和三星仍然用銅或鍍鈷。銅是很好的導體,但有個很討厭的特性,就是在納米尺度電阻會激增。

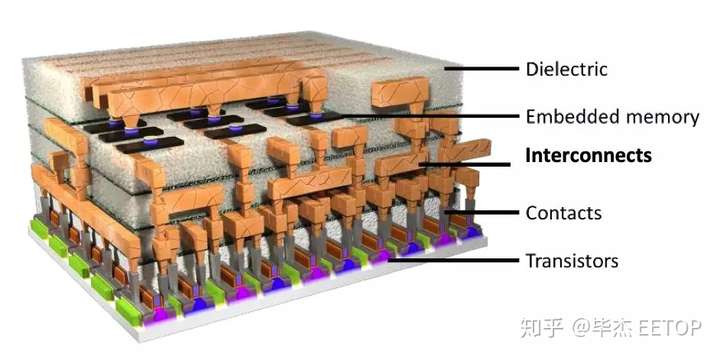

下圖是很漂亮的示意圖,圖中銅顏色那個就是銅。實際的芯片里這些金屬層可以有12層之多,把最底下的晶體管互聯起來形成電路。

這就是最微觀層面搭建的宏偉大廈。想想看,這是在芝麻大的空間里,上億個晶體管上面復雜搭建了上億根銅筋的混凝土建筑。

金屬釕是替代銅的另一個選擇。而在晶體管材料上,硅鍺合金和擁有更佳電性能的銦、鎵和砷化物也在被深度考慮或已應用。

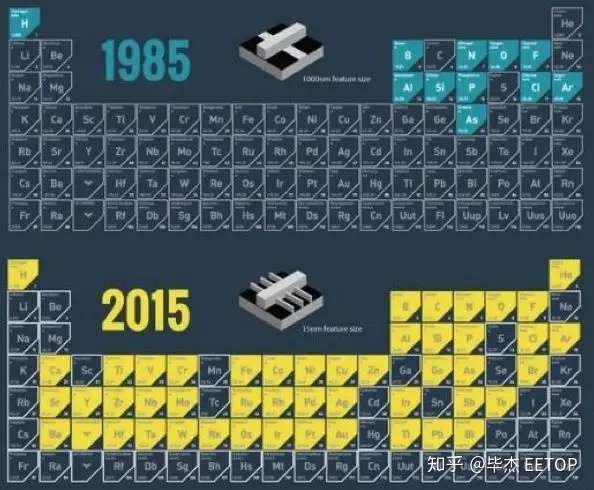

下圖很好地展示了在半導體發展歷程中,人類絞盡腦汁使用了元素周期表上的各種可能。這還不包括各種化合物。

(Photo Credit: SEMI)

看到這種精神,你認為讓科技精英們直接放棄摩爾定律,會那么容易嗎?

五

5nm制程基本上還是會用已經成熟的FinFET架構,FinFET比平面Planar更大的電流和更快的開關速度足夠支撐到5nm。只是光刻必須要用到EUV,否則掩模的層數要多到失控了。

(Photo Credit: IMEC)

目前各家的3nm方案都是更加立體的FET,nanosheet和nanowire等統稱為GAA(Gate all around)。“到處都是閘門”,這個名字顯示了這些小樂高晶體管的詭異模樣。它們還包括了碳納米管等各種復雜的材料。

IMEC目前篤信CFET將是打開1nm大門的鑰匙,到那時各廠市場部宣傳的單位將是埃米而不是納米。

雖然這些技術都在實驗室實現了,但是距離量產還有數不清的險阻。但最大的障礙是:錢。

目前開發一款7nm芯片的成本是3億美元,5nm預測是5億美元,而3nm很可能到10億美元。

究竟未來能有幾家公司需要做這種芯片呢?

這時,可怕的摩爾第二定律也閃現了威力:“新晶圓廠的成本每兩年翻一番”。

目前新7nm工廠是150億美元,那么5nm工廠將需要投資300億美元,3nm則理論上是600億美元。

六

正是因為各種不確定性或各種悲觀,否定摩爾定律的聲音越來越多。確實,對于目前硅架構存在量子隧穿效應極限。

不過,可行的方法不僅只有繼續縮小晶體管的尺寸,還包括做多層晶體管的方案和疊加晶圓的方案等。

英特爾也在試圖改進處理器架構的方法來實現另類摩爾定律,因為我們的最終目的是為了實現單位芯片面積計算力的每年提高。早期CPU性能是靠提高主頻實現的,但后來英特爾的Core架構和AMD的Zen架構都成功實現了主頻不變算力的突破,所以這個思路一定還有突破空間。

從目前情況看,至少未來十年人類還有充足的技術手段繼續倍增芯片性能。再往后,也許量子計算真的會到來?

關鍵詞: 摩爾定律