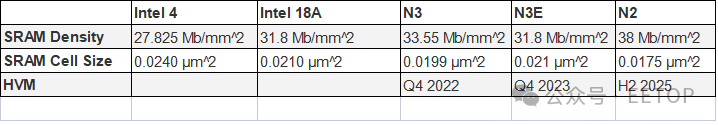

考慮到現代設計對SRAM(靜態隨機存取存儲器)的高度依賴,SRAM單元的大小和密度成為了新制造技術的關鍵特性。根據ISSCC 2025預先發布的計劃,英特爾18A制造工藝(1.8納米級)的SRAM密度明顯低于臺積電N2(2納米級),而更接近臺積電的N3。不過,英特爾的18A可能在其他方面具有重大優勢。英特爾的18A制造工藝采用了高密度SRAM位單元,尺寸為0.021微平方米(從而實現約31.8Mb/mm2的SRAM密度),與英特爾4代中0.024微平方米的高密度SRAM位單元相比有了顯著提升,但與臺積電的N3E和N5相當。相比之下,臺積電的N2制造技術將高密度SRAM位單元尺寸縮小至約0.0175微平方米,實現了38Mb/mm2的SRAM密度。

18A和N2都采用了環繞柵極(GAA)晶體管,但與英特爾不同,臺積電在其依賴鰭式場效晶體管(FinFET)的前代技術基礎上,成功地將高密度SRAM位單元尺寸大幅縮小。值得注意的是,除了SRAM位單元尺寸外,SRAM的另一個關鍵特性是功耗,而我們目前尚不清楚18A和N2在這一指標上的對比情況。談及英特爾的18A,該節點相比其前代產品具有兩大優勢:GAA晶體管和背面供電網絡(BSPDN)。BSPDN不僅有望改善對晶體管的供電,從而提高某些設計的性能效率,還能使設計師設計出更小的芯片,從而提高邏輯密度。

盡管現代芯片設計大量使用SRAM,且其密度對于節點間的縮放至關重要,但邏輯密度比高密度SRAM(HDC SRAM)密度更為重要。目前,我們還無法比較英特爾18A和臺積電N2在這一指標上的表現。此外,邏輯密度難以估算,因為每種工藝技術都有高密度、高性能和低功耗的庫,這些庫通常會在單個設計中混合使用。至于抽象處理器的邏輯密度,英特爾和臺積電尚未公布相關數據。在現代工藝技術中,最難縮放的是SRAM密度,這歸因于其設計的復雜性、穩定性和可靠性的運行要求,以及在更小節點上增加的變異性。因此,某些現代技術相比其他生產節點具有更大的SRAM單元尺寸也就不足為奇了。