美國應用材料公司用于下一代3nm和GAA的半導體設備簡介

2022-05-13 10:55:45 EETOPEETOP編譯自anandtech

上個月,三星代工廠悄悄宣布,將在第二季度開始使用其 3GAE(3 納米級、全柵極晶體管)的早期工藝技術生產芯片。雖然業界首個采用 GAA 晶體管的 3 nm 級節點本身就是一項值得注意的成就,但特別重要的是,要高效地制造 GAA 晶體管,晶圓廠必須配備新的生產設備。正好,應用材料公司最近剛剛介紹了他們的下一代設備,這些設備將用于使三星(和其他晶圓廠)能夠構建他們的第一個 GAA 芯片。

環柵晶體管:一次解決許多問題

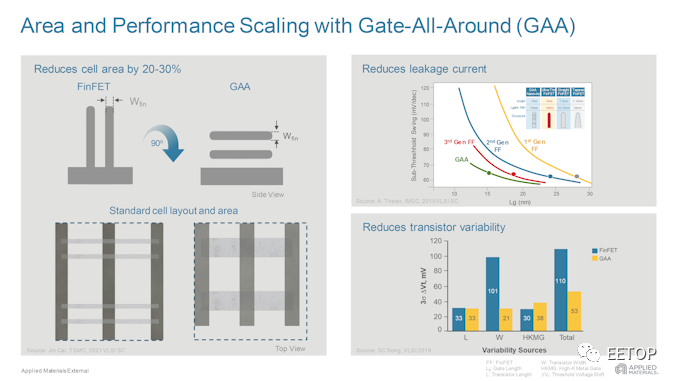

新的工藝技術應該能夠實現更高的性能、更低的功耗和更高的晶體管密度,以滿足芯片設計人員的要求。但近年來,這種組合特別難以實現,因為縮小晶體管尺寸會導致漏電流等負面影響。為了在最小化晶體管尺寸的同時保持縮放性能和電壓,該行業在 2012 年開始從平面晶體管過渡到 FinFET 晶體管(通過使柵極更高來增加晶體管溝道和柵極之間的接觸面積),并且這種類型的晶體管將繼續存在很長一段時間。但隨著晶體管縮小的負面影響開始顯現,基于 FinFET 的節點創新步伐正在放緩。

雖然所有芯片制造商都在各種學術行業活動中談論 GAAFET 及其相對于 FinFET 的優勢,但三星是第一家宣布過渡到 4 納米節點的新型晶體管的公司, 2019 年 ,它推出了基于 GAAFET 的 3GAE 和 3GAP 節點,并分別于 2022 年和 2023 年實現大批量生產。去年,該公司 再次強調 了在 2022 年使用其 3GAE 開始生產的計劃,本季度它表示將在第二季度開始量產。

制造業面臨挑戰

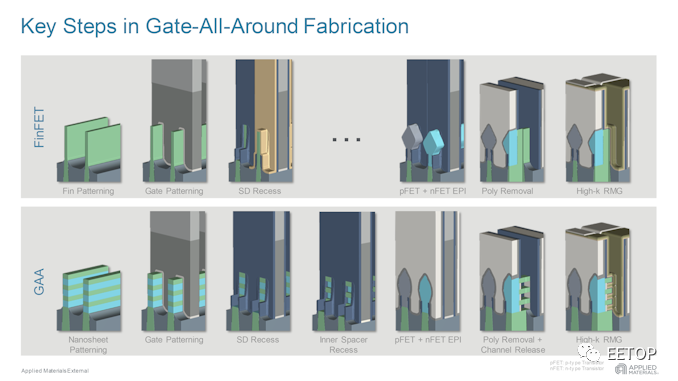

但是使用任何領先的工藝技術生產芯片都是具有挑戰性的,使用三星基于 MBCFET 的 3GAE 節點制造產品肯定會帶來一些風險,不僅因為我們談論的是 3 納米級制造工藝,而且因為 GAA 晶體管的制造是不同的而不是制造 FinFET。

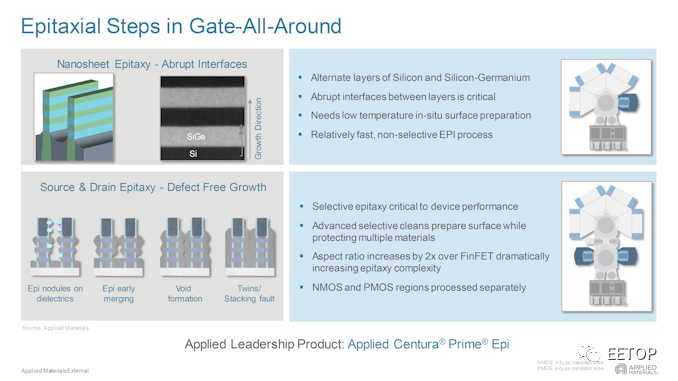

GAA 晶體管的通道采用光刻、外延和選擇性材料去除等工藝成型,這些工藝使芯片制造商能夠微調寬度和均勻性以獲得最佳功率和性能。與 FinFET 相比,這些外延步驟要復雜得多,因為制造商需要在微小的 10 nm 通道周圍沉積多層柵極氧化物和金屬柵極疊層,這是 GAAFET 面臨的關鍵挑戰。這就是應用材料公司的高真空集成材料解決方案 (IMS) 系統發揮作用的地方。

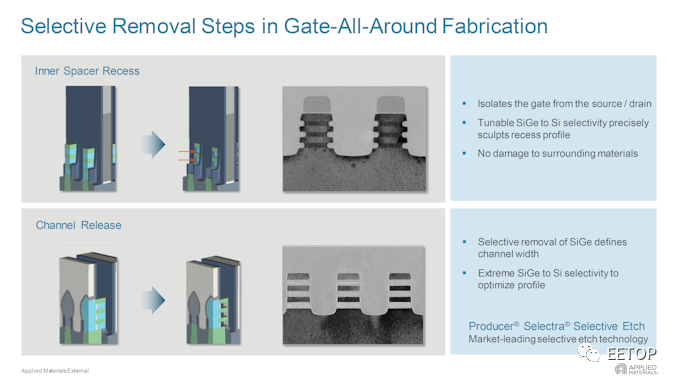

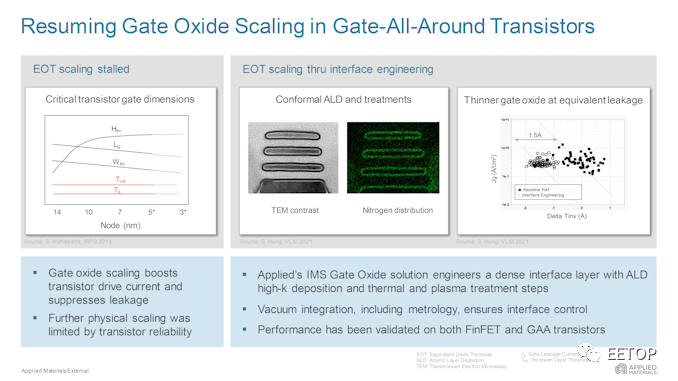

首先,應用材料公司的 Producer Selectra Selective Etch 腔體去除了不必要的 SiGe,以將柵極與源極/漏極隔離,并在不損壞周圍材料的情況下定義溝道寬度。其次,AppliedCentura Prime Epi IMS可以使用集成原子層沉積 (ALD)、熱處理、等離子體處理和計量步驟來沉積超薄柵極氧化層。與競爭解決方案相比,Applied 的 IMS 可以將柵極氧化層厚度減少 1.5 埃,這可以使柵極更厚并實現更高的驅動電流,從而提高晶體管性能,而不會增加電流泄漏,這是薄柵極的結果。

Applied 于 2016 年推出了其第一款 Selectra 蝕刻系統,從那時起已交付了 1,000 多個目前由其客戶使用的腔體,因此業界非常了解如何使用它們。雖然蝕刻是一種廣泛使用的工藝,但隨著行業開始轉向更新的工藝技術,包括基于 GAA 晶體管的工藝技術,它的使用和重要性將會增加。

需要注意的是,Applied Materials 共享的數據來自多家公司(包括臺積電和高通),不應僅適用于三星代工的 3GAE 和 3GAP 節點。同時,GAA/MBC/納米帶/納米片晶體管的一般優勢,以及其制造面臨的挑戰,對于整個行業來說都是相似的。

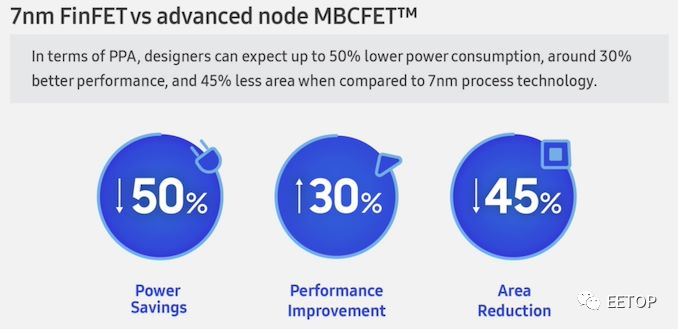

三星的 3GAE:+30% 性能,-45% 面積

說到優勢,三星預計其 3GAE 工藝與 7LPP 相比,性能提升 30% 或功耗降低 50%,面積減少 45%。這種有形的好處可能足以證明短期內與這種轉變相關的挑戰是合理的。

目前,使用依賴全新晶體管結構的 3GAE 制造技術總體上具有挑戰性,因為除了新的電子設計自動化 (EDA) 工具外,三星還需要發明新的 IP,并采用全新的設計規則. 所有這些,再加上新的光刻、新的蝕刻和新的沉積步驟,都將使三星的轉型變得困難。

但作為交換,它將比英特爾和臺積電提前數年開始獲得 GAA 晶體管的經驗,這可能會在長期的未來帶來一定的收益。此外,使用 GAAFET 的經驗將有利于三星的 DRAM 制造,因為內存大大受益于更小的單元尺寸和更高的晶體管密度。

原文:

https://www.anandtech.com/show/17385/applied-materials-new-tools-needed-for-3-nm-and-gaa-transistors