EDA國產替代!芯聯成最新電路分析軟件BunnyGS? V1.8.4版功能淺析

2021-12-07 11:22:05 EETOP

EDA(Electronic Design Automation,電子設計自動化)作為集成電路領域的底層關鍵工具,貫穿于集成電路設計、制造、封測等各個環節,是集成電路產業的戰略基礎之一,更是未來萬億數字經濟的重要基柱。EDA對于整個集成電路產業的繁榮發展,其重要性不言而喻。

EDA行業是一個具有高技術壁壘、高毛利率的行業,行業立基者經過三十多年的發展,通過技術研發和持續并購,已經構建起一條覆蓋全流程各環節的完整的產業生態,并牢牢掌握著全球大份額市場,挑戰者很難一時撼動其地位。

2020年,全球EDA&IP市場規模超過114億美元,僅Synopsys和Cadence兩家,就占據了全球高達61%的市場,其市值都在500億美元左右,高達市場規模將近5倍。但隨著碳化硅等第三代半導體材料的出現、先進工藝制程、先進封裝的演化、以及廠商產品的快速迭代,傳統EDA產業也在朝著更具人工智能化、更快算力、共享云端化等方向發展,當下中國,雖然還未誕生具有市場壟斷地位的EDA企業,但在該領域呈現百花齊放的態勢,有做全流程工具的,也有專注某個環節的,有針對器件仿真模擬的,更有與Fab廠硬件設備相配套的良率檢測系統等等。據云岫資本預測,當前中國EDA&IP市場規模約為百億人民幣,未來中國國內也將有望誕生高市值的EDA龍頭企業。

后摩爾時代,more than moore,芯片的設計不僅僅追求先進制程,更關注PPA(Performance、Power、Area)。能否快速響應客戶需求,針對客戶需求進行差異化定制,幫助客戶快速完成產品迭代,是芯片設計公司聚焦的重點。新時代的需求,對設計工具的迭代更新提出了更高的要求,設計自動化(人工智能化)、系統處理大數據時算力的強度和速度、系統的開放化以及系統上云等都是EDA工具力爭實現突破原有賽道的新方向。

“在30萬芯片人才缺口的當下,實現設計工具的高度智能化,有助于企業縮減大量人力成本,同時降低芯片的設計門檻。”這也是擺在芯聯成面前的一大現實難題。隨著超大規模數字集成電路(VLSI)的發展,百萬門甚至千萬門級的數字集成電路項目,更需要借助高性能的EDA工具實現自動化分析與設計。

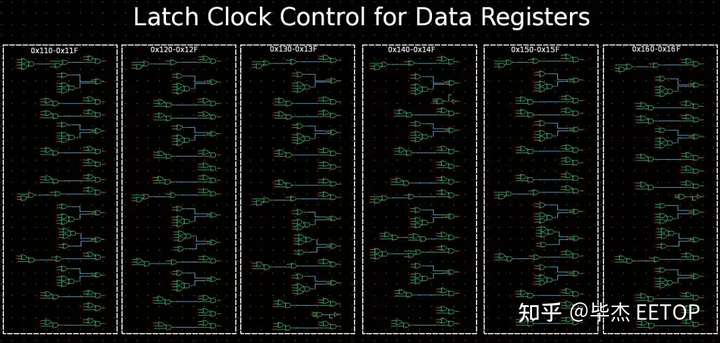

芯聯成自主研發的BunnyGS®系統,是一款專為IC&IP定制化設計研發的EDA工具軟件,融合了圖像處理、AI算法、云計算等關鍵核心技術,高度集成完備的版圖和原理圖編輯、數字電路信號流分析和自動布局布線等子系統,能滿足客戶對超大規模IC項目的分析需求,并可在和客戶共同確認芯片設計規格的基礎上,幫助客戶實現IC&IP定制需求。

從BunnyGS®V1.8.0到BunnyGS®V1.8.4,是一個經過歷次迭代更新與嚴格測試的長期考驗的過程,芯聯成在與客戶的合作交流過程中,認真聽取和收集客戶的需求反饋與建議,對BunnyGS®的原有功能的性能進一步提升,快速響應客戶新興需求,將新開發的點工具集成在原有系統,逐步打造完整的閉環生態系統。其平臺上所有數據都可兼容主流EDA設計軟件,同時可在Linux和Windows兩種平臺運行,具有層次化線網追蹤功能,能支持多用戶協同在線工作。

1、兼容Cadence PCell,支持PCell繪制版圖

PDK,全稱Process Design Kit,通常翻譯成“工藝設計套件”。PDK用代工廠的語言定義了一套反映Foundary工藝的文檔資料,是一組描述半導體工藝細節的文件,并用于EDA工具中。它是溝通IC設計公司、代工廠與EDA廠商的橋梁;也是設計公司用來做物理驗證的基石,更是流片成敗的關鍵因素。

PDK包含了多個文件,如:器件模型(Device Model)、Symbols & View、CDF、PCell、TechnologyFile、PVRule。其中Pcell(Parameterized Cell),中文稱“參數化單元”,是Cadence Virtuoso(Cadence公司推出的用于模擬/數字混合電路仿真和射頻電路仿真的專業軟件。)的PDK,它是用SKILL語言開發的,但是直到目前為止,其它主流EDA廠商都無法讀寫Virtuoso的PDK,無法原生態支持。

BunnyGS®軟件實現了一種能兼容Cadence PCEll工藝庫的方法,支持使用PCell繪制版圖,芯聯成自研的sltPcell程序,能支持CSMC、DB、HHNEC、SMIC、TSMC等常見工藝庫,提高了Cadence PCell工藝庫兼容的靈活性。

2、新增數字電路中組合邏輯的BOOL仿真功能

BunnyGS®軟件新增了數字電路中組合邏輯的BOOL仿真功能,目前最大支持13位數據輸入,即可一次完成8192次遍歷運算。同時,軟件支持對運算結果進行在線解碼,用戶可根據需要對輸入輸出信號進行排序和選擇,在選擇有效值后可直接得到解碼結果。

該功能常用于分析內部線網關系復雜、實例數量較大的電路模塊,如譯碼(器)電路、算法實現電路等,在使用時可忽略其內部復雜的結構,一次完成從輸入到輸出的邏輯映射,高效地完成電路分析。例如在分析以太網通訊芯片、距離傳感器芯片等具有復雜寄存器映射的芯片時,使用該功能通過一次仿真即幫助工程師得到芯片的完整寄存器映射,數據流向分析因此更快更準。

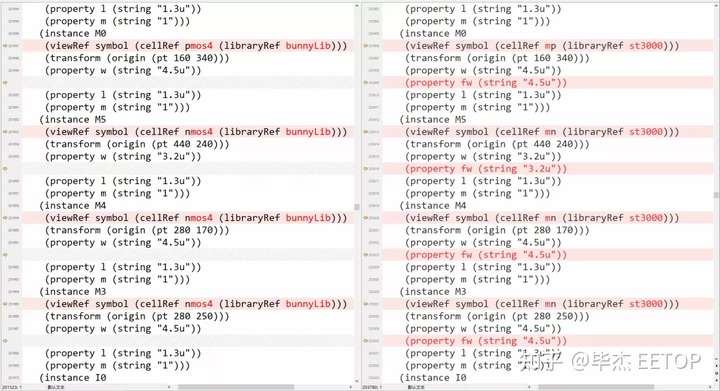

5GGJoKd" style="margin: 1.4em 0px; color: rgb(18, 18, 18); font-family: -apple-system, BlinkMacSystemFont, "Helvetica Neue", "PingFang SC", "Microsoft YaHei", "Source Han Sans SC", "Noto Sans CJK SC", "WenQuanYi Micro Hei", sans-serif; font-size: medium;">3、全新EDIF格式輸出算法,有效取代人工替換PDK單元

工程師整理好的電路有時需替換工藝庫,不同工藝庫之間的器件種類、數量及參數名稱和約束等都不相同,傳統的替換工藝庫的方法是在視圖上逐一修改器件類型。項目的器件數量巨大,逐個修改必然會帶來難以估計的工作量,同時器件參數存在映射或約束關系,無法直接修改。

芯聯成開發了一種高PDK兼容度的EDIF格式輸出算法,通過器件庫和PDK庫的器件名稱和參數映射關系配置pdkmap.xml文件,在導出EDIF時,軟件自動將BunnyGS®提取的器件轉換為相應的PDK器件,同時更新器件的參數。使用高PDK兼容度的EDIF格式輸出算法后,工程師能通過導出的EDIF文件準確、高效地替換PDK庫,為高效、高質量地交付項目提供了有力支撐。

4、BunnyGS®系統與仿真驗證軟件無縫對接

大規模數字電路仿真驗證中,需要導出模塊的verilog文件。BunnyGS®軟件支持分類別導出verilog,可以將所有基本單元的functional視圖導入到同一文件中,宏模塊導入到一個文件中。也可以將所有基本單元的functional視圖導入到同一文件中,不同宏模塊導入到不同文件中。將這些verilog文件導入到數字仿真軟件進行仿真驗證。

常用的數字仿真軟件有Synopsys公司的VCS和Verdi、Cadence公司的 ncverilog、Mentor公司的modelsim。Verdi等軟件的界面顯示的實例是無序的,沒有使用到規則的實例位置和有序的線網關系。

在進行驗證時,通常需要使用有序的信號或能快速地找到對應的信號。BunnyGS®軟件新增了格式化輸出線網名功能,對于整理好的電路,可以將有序的信號格式化為Verdi軟件調試格式輸出,減少了復雜和繁瑣的工作,方便工程師調試和跟蹤信號,讓工程師的工作重心落到驗證上。

芯聯成軟件有限公司成立于2016年,是國內領先的集成電路設計服務和知識產權分析服務供應商,致力于為客戶提供EDA軟件開發、芯片工藝分析、電路分析、專利侵權分析和IP&IC設計服務等一系列高技術服務。

芯聯成服務超過3000多個的電路分析和設計服務項目,包括:5G通訊應用的射頻SoC芯片、MCU系列芯片、多種高速低速ADC/DAC芯片、各類傳感器應用芯片、電源管理芯片、高速時鐘系列芯片、驅動應用芯片、接口和隔離芯片、DRAM/NAND存儲系列等各市場領域的應用芯片。通過為客戶提供EDA軟件開發、硅知識產權分析、以及全定制化IC&IP設計服務,芯聯成致力于成為IC設計公司的最佳合作伙伴。