回歸并行!芯片到芯片的最新超高速通信方式:超短距(USR)接口

2020-07-06 12:57:21 EETOP異構,多芯片2.5D封裝技術的最新進展導致了一種新型的接口,即超短距離(USR)接口,其電氣特性與傳統的印刷電路板走線有很大不同。長而有損的連接需要使用SerDes IP的串行通信通道,而短距離接口則支持并行總線體系結構。

SerDes信號需要(50歐姆)端接,以最大限度地減少反射和降低遠端串擾,從而增加功率耗散。2.5D封裝內的電短接口不需要端接。這些并行接口不需要 "恢復 "嵌入在串行數據流內的時鐘,以及相關的時鐘-數據恢復(CDR)所需的電路面積和功耗,而是可以使用更簡單的“時鐘轉發”電路設計-提供傳輸的時鐘信號帶有一組N個數據信號。

該接口的另一個優點是,大大降低了芯片之間靜電放電保護(ESD)的電路設計要求。內部封裝連接將具有較低的ESD電壓約束,從而節省了大量的I/O電路面積(并顯著減少了I / O寄生效應)。

2.5D封裝中裸片之間獨特的接口設計要求導致使用“小芯片”一詞,因為不需要SerDes鏈接的全芯片設計開銷。然而,到目前為止,這些USR接口所采用的電路和物理實現方法相當多樣。

在最近的VLSI 2020研討會的受邀演講中,臺積電提出了他們關于并行總線,時鐘轉發架構的提案“ LIPINCON”,該架構是“低壓,封裝內互連”的縮寫。

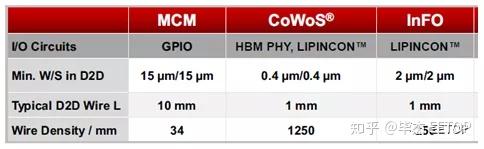

短距離接口設計的關鍵參數是:

架構師正在尋求最大程度地提高總數據帶寬(總線寬度*數據速率),同時實現非常低的每位功耗。無論小芯片接口是在多個處理器(或SoC)之間,處理器到內存還是處理器到I / O控制器功能之間,都將應用這些關鍵設計措施。

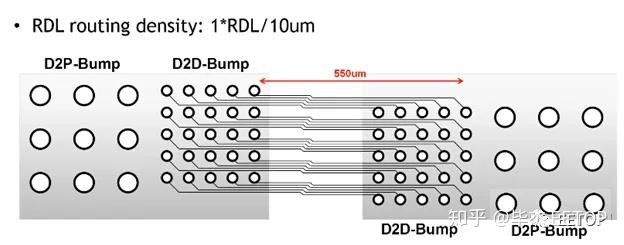

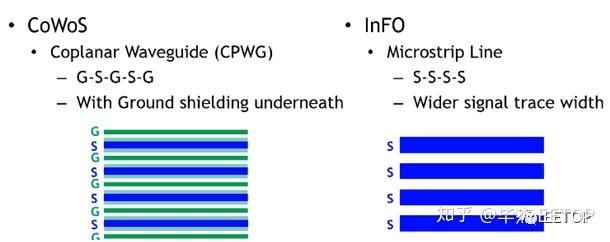

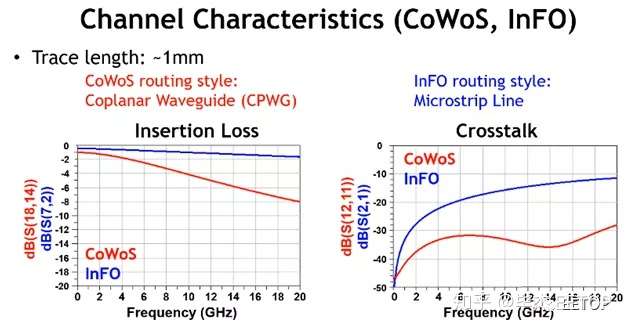

物理信號的實現方式會有所不同,具體取決于封裝技術。具有硅中介層的2.5D封裝的信號重新分配層(RDL)將利用可用的更精細的金屬間距(例如,TSMC的CoWoS)。對于利用重組芯片襯底嵌入芯片的多芯片封裝,RDL層要厚得多,間距要大(例如,TSMC的InFO)。下圖說明了與CoWoS和InFO設計相關的典型信號走線屏蔽(和無屏蔽),以及相應的信號插入和遠端串擾損耗。

下圖示意性地說明了臺積電LIPINCON IP定義的關鍵特性。

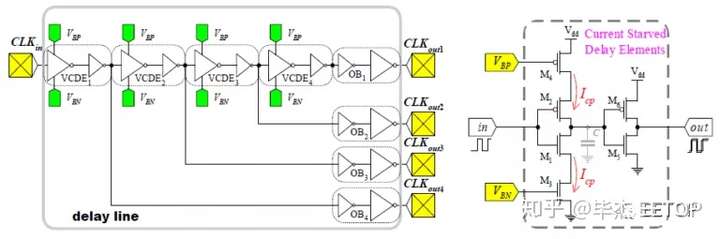

簡而言之,DLL是一個獨特的電路,它由相同延遲單元的(偶數個)鏈組成。下圖顯示了延遲鏈的示例。[2]通過調制輸入到各級輸入反相器(即“電流不足”的反相器)中的串聯nFET和pFET器件的電壓,可以動態調節各級的開關延遲。(其他延遲鏈實現會動態修改每一級輸出上相同的電容負載,而不是調節每一級的內部晶體管驅動強度。)

DLL中的“環路”由相位檢測器(帶低通濾波器的XOR型邏輯)形成,該檢測器將輸入時鐘與鏈的最終輸出進行比較。輸入時鐘相對于鏈輸出的超前或滯后特性可調節逆變器控制電壓-因此,鏈的整體延遲“鎖定”于輸入時鐘。DLL鏈中每一級的(相等)延遲提供與輸入時鐘信號的特定相位相對應的輸出。使用適當的相位輸出在接收器觸發器中捕獲并行數據,這是一種補償接口上任何數據到時鐘偏移的方法。

臺積電IP團隊針對SoC到內存接口的特定情況開發了一種創新方法。存儲器小芯片可能不一定嵌入DLL來捕獲信號輸入。對于非常寬的接口(例如,將512個地址,256個數據位分成多個子通道),成本敏感型存儲芯片中DLL電路的開銷會很高。如下圖所示,在SoC中出現了DLL相位輸出,它用作存儲器寫周期的輸入選通脈沖。(圖中還顯示了存儲器讀取路徑,該路徑說明了如何將來自存儲器的數據選通脈沖連接到read_DLL電路輸入。)

對于并行LIPINCON接口,與信號串擾相關的同時開關噪聲(SSN)是一個問題。對于上面說明的屏蔽(CoWoS)和非屏蔽(InFO)RDL信號連接,TSMC給出的結果說明了這種低擺幅信令的串擾非常易于管理。

可以肯定的是,設計人員可以選擇在小芯片之間開發邏輯接口,這些小接口使用數據編碼來最大程度地減少連續周期中的信號轉換活動。最簡單的方法是添加數據總線反轉(DBI)編碼-可以將下一個周期中的數據與當前數據進行比較,并使用真實值或反轉值進行傳輸以最大程度地減少開關活動。小芯片之間的附加DBI信號將這個決定傳遞給接收器,以解碼這些值。

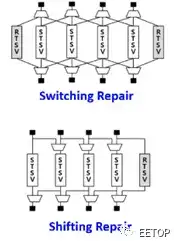

異種2.5D封裝的開發依賴于已知良好芯片/小芯片(KGD)的集成。盡管如此,通過增加冗余通道可以提高最終包裝的組裝后產量,該冗余通道可以在包裝測試后選擇(理想的是內置自檢)。臺積電的演示文稿包括可以集成到小芯片設計中的冗余通道拓撲的示例。下圖說明了用于將冗余的硅通孔(TSV)插入互連的兩種架構。當設計小芯片之間的接口時,這將是封裝良率與電路開銷的折衷。

在基于SerDes的設計中,完整的電路和PCB互連提取以及仿真用于分析信號損耗。針對接收器傳感放大器的電壓差分析了信號抖動和幅度的變化。還進行了基于硬件實驗室的探測,以確保在接收器處捕獲數據時適當的“眼圖張開度”。臺積電強調,這種接口驗證不適用于2.5D封裝技術。如下圖所示,他們的IP團隊開發了一種新穎的方法,將變體引入LIPINCON發送驅動器和接收捕獲電路中,以創建用于硬件驗證的等效眼圖。

臺積電的演講提到,他們的一些客戶已經為USR接口設計開發了自己的IP實現。一個示例顯示了一個非常低的擺幅(0.2V)電學定義,它是“以地面為參考”的(例如,信號擺幅高于和低于地面)。但是,對于尋求利用高級封裝而又沒有設計資源來“自行開發”芯片接口電路的無晶圓廠客戶而言,TSMC LIPINCON IP定義是一種極具吸引力的選擇。而且,坦率地說,考慮到臺積電能夠提供的動力,該定義可能會有助于加速尋求捕獲IP和小芯片設計市場機會的開發商中的“標準”電氣定義。

EETOP 官方微信

創芯大講堂 在線教育

半導體創芯網 快訊

相關文章