Hot Chips:IBM 用兩款新處理器解決生成式 AI 問題

2024-08-30 11:56:56 EETOP

IBM 設計的處理器保持了 IBM 大型機眾所周知的高安全性、可用性和性能級別。

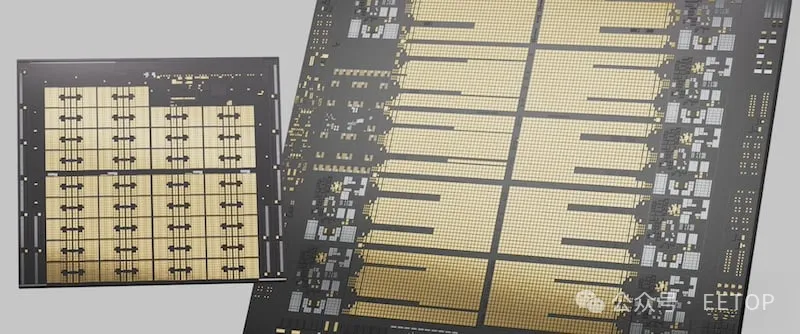

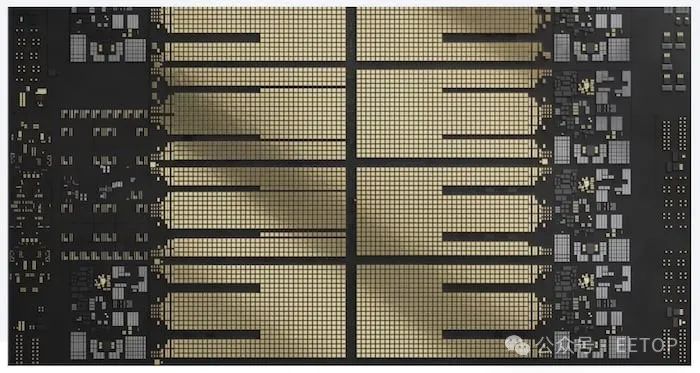

IBM 的 Telum II 處理器對其前身進行了顯著改進,具有更快的速度、更大的內存容量和新功能。

“我們設計了 Telum II,以便內核可以將 AI 操作卸載到模塊中其他七個相鄰處理器芯片中的任何一個,” IBM 微處理器設計師 Chris Berry 說。“它為每個內核提供了對更大 AI 計算池的訪問,從而減少了對 AI 加速器的爭用。”

該處理器利用八個高性能內核,每個內核以固定的 5.5GHz 頻率運行,并具有集成的片上 AI 加速器。該加速器直接連接到處理器的 CISC 指令集,以實現低延遲 AI 操作。與依賴內存映射 I/O 的傳統加速器不同,Telum II 的 AI 加速器將矩陣乘法和其他 AI 基元作為本機指令執行,從而減少開銷并提高吞吐量。Telum II 中每個加速器的 AI 計算能力翻了兩番,達到每個芯片 24 TOPS。

該處理器還大幅增加了緩存容量,每個內核都可以訪問 36 MB 的 L2 緩存,片上總計 360 MB。虛擬 L3 和 L4 緩存分別增長了 40%,達到 360 MB 和 2.88 GB。這些增強功能使 Telum II 能夠更高效地處理大型數據集,進一步支持其 AI 和事務處理能力。

Telum II 處理器的顯著特點之一是其集成數據處理單元 (DPU)。

在 IBM 大型機每天處理數十億個事務的企業環境中,I/O 運營效率極為重要。因此,Telum II 中的 DPU 連貫地連接到處理器的對稱多處理 (SMP) 結構,并配備了自己的 L2 緩存。

DPU 架構包括四個處理集群,每個集群有 8 個可編程微控制器內核,總共 32 個內核。這些內核通過本地一致性結構互連,該結構在整個 DPU 中保持緩存一致性,并將其與主處理器集成。這種集成允許 DPU 直接在片上管理自定義 I/O 協議。

Berry 說:“通過將 DPU 放在 PCI 接口的處理器端,并實現 DPU 與運行主要企業工作負載的主處理器的連貫通信,我們可以最大限度地減少通信延遲并提高性能和能效。“整個系統的 I/O 管理功耗降低了 70%。”

此外,DPU 包括用于循環冗余校驗 (CRC) 加速的專用硬件和用于批量數據傳輸的專用數據路徑,因此緩存不會受到瞬態數據的污染。

與 Telum II 處理器相輔相成的是IBM Spyre 加速器,這是一款專用的 AI 芯片,旨在將 AI 功能擴展到僅靠主處理器所能實現的之外。

Spyre 加速器安裝在 75 W PCIe 適配器上,具有 32 個內核,每個內核具有 2 MB 的暫存器內存,片上總計 64 MB。與傳統緩存不同,此暫存器通過共同設計的軟硬件框架進行優化,可在 AI 計算期間實現高效的數據存儲和管理。

Spyre 加速器支持大型語言模型和其他計算密集型 AI 工作負載。Spyre 在單個 I/O 模塊中的 8 個卡中提供高達 1 TB 的內存,使 IBM Z 系統能夠處理需要大量計算能力和內存帶寬的 AI 工作負載。加速器的核心支持 int4、int8、fp8 和 fp16 數據類型。在同時使用多個 Spyre 卡的情況下,系統可以擴展到 1.6 TB/s 的內存帶寬。

據 IBM 稱,Telum II 和 Spyre 旨在以優化 AI 工作負載的方式在更大的大型機架構中協同工作。

Telum II 的片上 AI 加速器提供集成在主處理器中的即時、低延遲 AI 處理功能。相比之下,Spyre 加速器為更復雜的大規模 AI 模型提供了必要的額外、可擴展的 AI 計算能力。

IBM 聲稱,兩者之間的協同作用解鎖了集成 AI,其中多個 AI 模型(包括傳統模型和 LLM)被串聯使用。例如,較小、節能的模型可以處理大多數事務,而更復雜的模型則保留給需要更高置信度的情況。此策略提高了準確性并優化了資源使用情況。

Telum II 和 Spyre Accelerator 為 IBM 大型機的未來提供了強大的集成解決方案。

“我們目前正在構建一個測試系統,其中將包含 96 張 Spyre 卡,其中總共將具有 30 peta-ops 的 AI 推理和計算能力,”Berry 總結道。“這就是我們正在討論添加到下一代 IBM Z 中的額外 AI 計算的規模。”

EETOP編譯整理自allaboutcircuits